概览

在规划进程的前期考虑您的发布硬件的规划方针,能够帮助您缩短产品上市时刻。您无需重复劳动,能够经过运用您所发布的产品的原型体系中的适当一部分软硬件,更快速地发布一个更牢靠的嵌入式体系或机器。

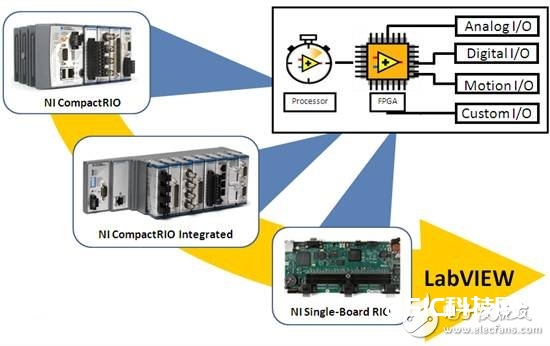

NI可重新装备的I/O(RIO)发布曲线

图1.NI RIO 发布曲线:从快速结构原型到低本钱装备

NI供给了多种商业上现成可用的(COTS)、具有一起的可重新装备的I/O(RIO)架构的硬件。该架构组合了一个实时处理器、一个现场可编程门阵列(FPGA)和多种I/O,其间包括模仿I/O、数字I/O、运动I/O和通讯I/O等。运用这一标准架构和NI LabVIEW图形化开发东西,您能够运用灵敏的高功用硬件,快速地规划嵌入式体系和工业监控机器并结构其原型。运用彻底的代码复用,您能够将您的原型体系快速转化为一个本钱优化的发布体系,该体系采用了相同的硬件架构然后降低了本钱并缩短了产品上市时刻。

NISingle-BoardRIO嵌入式操控与收集硬件

新推出的NISingle-BoardRIO嵌入式产品拓宽了NI RIO开发低本钱、板卡层次的嵌入式硬件的可用挑选。再次着重,经过标准的NI RIO架构和LabVIEW,您能够运用模块化的、灵敏的CompactRIO快速地开发嵌入式体系,并快速发布到新的、本钱更低的、板卡层次的 NISingle-BoardRIO嵌入式硬件。因为您能够从原型结构到开发复用相同的LabVIEW代码,您能够缩短产品上市时刻并提高嵌入式设备与机器的牢靠性。

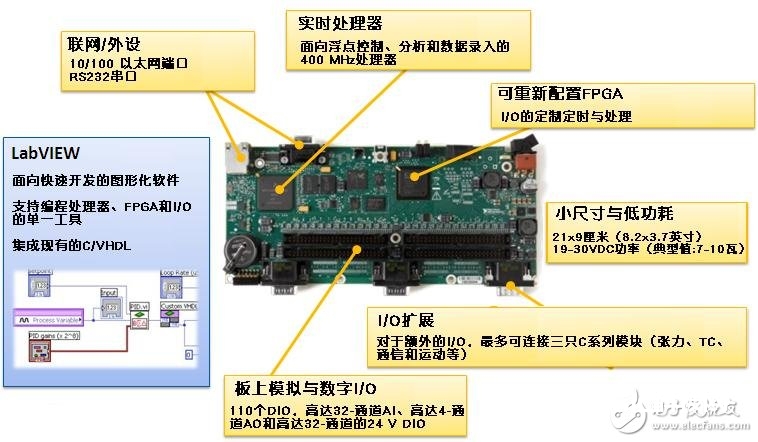

新推出的NISingle-BoardRIO产品供给了如下特性:

* Single-Board嵌入式操控与收集

* LabVIEW图形化编程与面向快速开发的中间件驱动程序东西

* 面向牢靠、独立操作与信号处理的板上实时处理器

* 面向定制I/O守时与处理的板上FPGA芯片

* 板上模仿I/O与数字I/O

* 面向板卡层次嵌入式规划的低本钱体系

图2. NISingle-BoardRIO在单个板卡上集成了一个处理器、FPGA和模仿I/O与数字I/O,您能够运用LabVIEW图形化东西对其进行编程。

每个NISingle-BoardRIO设备在单个板卡上集成了一个嵌入式实时处理器、一个高功用FPGA和板上模仿I/O与数字I/O。与NI推出的一切其他RIO硬件类似,该I/O直接与FPGA相连,供给了守时与I/O信号处理的低层次的定制完结。该FPGA经过一个高速PCI总线与嵌入式实时处理器相连。LabVIEW包括内置的数据传输机制,将数据从该I/O传输至FPGA并从该FPGA传输至嵌入式处理器,以完结实时剖析、进一步处理、数据录入或许与联网主机的通讯。

运用LabVIEW更快速地发布嵌入式体系

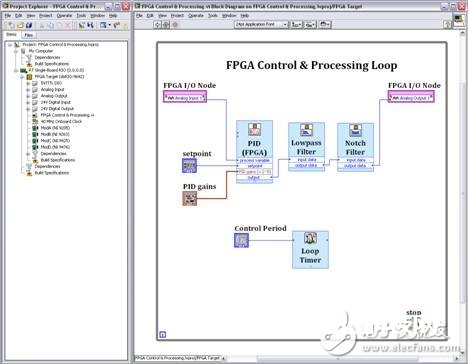

运用LabVIEW图形化开发环境,您能够运用相同的LabVIEW项目,对您的RIO嵌入式体系的实时处理器、可重新装备FPGA和I/O进行编程,以完结嵌入式操控、监测、处理和数据录入使用。运用专业的LabVIEW模块,您能够对实时处理器(LabVIEW实时模块)和 FPGA(LabVIEW FPGA模块)进行编程。LabVIEW也还具有一组广泛的中间件驱动程序,这些驱动程序完结了您的RIO嵌入式体系的一切硬件组件(模仿I/O与数字I /O、FPGA、处理器、外设和存储器等)的无缝集成。

图3.运用LabVIEW项目办理和编写处理、FPGA和I/O的一切代码。

LabVIEW实时模块

体系内的嵌入式实时处理器经过LabVIEW实时模块进行编程,该模块包括面向浮点操控、处理、剖析、数据录入和通讯的内置函数组块。 LabVIEW实时模块包括多个特性,例如:

* 面向分布式嵌入式实时体系便利联网的LabVIEW同享变量技能

* 到达奇妙精度确实定性软件守时

* 逾越600个浮点高档操控与信号处理函数

* 现有C/C++代码的集成

* 快速发布和仿制现有体系的体系仿制东西

LabVIEW FPGA模块

您能够运用LabVIEW FPGA模块对RIO硬件体系中的可重新装备的FPGA进行快速编程,以完结定制操控与高速操控、I/O守时和信号处理。LabVIEW FPGA模块具有下列特性:

* 面向现有HDL代码的便利集成的组件层IP(CLIP)节点

* 快速架构实时代码和FPGA代码的FPGA导游

* 使发动更为便利的FPGA项目导游

* 面向根据FPGA的操控、状态机以及其他的完结的LabVIEW状态图模块

* 便利开发与调试的FPGA仿真特性

* 定点FPGA IP函数组块:

1. 快速付立叶改换(FFT)

2. 多通道PID

3. 信号发生器

4. 陷波滤波器

5. 观察一切的预置的LabVIEW FPGA函数和IPNet中的IP

中间件驱动程序东西

嵌入式规划的最大应战之一就是创立、调试和验证用于集成嵌入式体系的一切硬件组件的、驱动程序层次的软件栈所需的巨大工作量。在传统情况下,这一集成进程是留给用户来完结的,这使得嵌入式体系的规划进程变得更为杂乱和冗长。

由传统的Single-Board计算机与其他嵌入式体系供货商供给的根本驱动程序提高了生产率与功用并缩短了产品上市时刻,而NI中间件驱动程序则逾越了这一根本驱动程序。每台支撑RIO的设备均包括有驱动程序软件和其他的装备服务软件。内置的中间件驱动程序东西包括如下功用特性:

* 面向模仿、数字、运动和通讯I/O与FPGA间接口的内置函数

* 面向FPGA与处理器间数据通讯的传输函数

* 面向FPGA/处理器至存储器间接口的办法

* 面向处理器至外设(RS232串口和以太网)间的接口的函数

* 面向高功用的多线程驱动程序

从原型到发布的转化

具有多个外形尺寸的RIO渠道供给了多种原型结构与开发选项。CompactRIO集成体系与NISingle-BoardRIO为高容量嵌入式体系供给了最佳特性。与其他板卡层次产品类似,NI Single-BoardRIO嵌入式硬件要求您确保您的规划与标准兼容需求(如电磁兼容性(EMC))共同,并支撑满足的散热。封装的、现成可用的 CompactRIO体系供给了这些认证。考虑表1中的标准以确认哪一种RIO硬件最契合您的使用需求。

表1.NI RIO硬件比较

CompactRIO模块化体系

CompactRIO集成体系

NI Single-BoardRIO

温度规模

-40~70 ºC

-20~55 ºC

-20~55 ºC

EMC认证

√

√

−

供给机械封装

√

√

−

混合调配操控器与底板的才能

√

−

−

C系列插槽或拓宽

4插槽或8插槽

8插槽

面向I/O拓宽的3个衔接端子

面向根据USB的存储的全速USB主机端口

√

−

−

内部非易逝性存储

高达2 GB

高达256 MB

高达256 MB

电源供给输入规模ie

Dual 9 to 35 VDC

9~35 VDC双电源

Single 19 to 30 VDC

19~30 VDC单电源

Single 19 to 30 VDC

19~30 VDC单电源

FPGA

Xilinx Virtex FPGA

Xilinx Spartan-3 FPGA

Xilinx Spartan-3 FPGA

NI公司供稿