数字信号处理技能在高分辨率图象、视频处理及无线通信等范畴的广泛运用, 导致对高速、高精度、依据规范CMOS 工艺的可嵌入式ADC 的需求量日积月累。关于迅速开展的依据IP 规划的片上体系集成技能, 功耗低、面积小、可嵌入的ADC 中心模块逐步成为数模混合信号IC 规划的要害。随同技能的开展, ADC 的结构呈现了多种完结计划, 如过采样Σ- △型、全并行( Flash) 、流水线和逐次迫临( Successive-approximatiON RegiSTer) 等结构。其间, FlashADC 转化器和Σ- Δ ADC 转化器,它们别离满意高速、高精度两个极点的需求。而逐次迫临转化器( SARADC) 具有中等速度( 5 MS/s 以下) 、中等精度( 8~18 位) 、低功耗和低本钱的归纳优势,在愈加宽广的范畴中得到了运用。

因为SARADC 能够习惯多种模仿输入办法( 单级、双级、差分) , 在开关、多通道运用中能确保零数据推迟,并且速度、精度适中, 功耗、本钱低, 因而, 在工业操控方面运用广泛, 适用于丈量各种物理量的传感器。例如, 在传感器网络中, 不计其数个传感器节点由1 块电池或许几平方毫米的太阳能电池供电, 这就要求传感器节点面积小、本钱低, 并且长时间作业耗费的能量也很小, SAR ADC 可满意这种运用需求。SAR ADC 还广泛运用于医学仪器的成像体系, 例如CT 扫描仪、MRI 和X 射线体系。SAR ADC零推迟、较高采样速率和较好DAC 目标的优势, 确保了成像体系的高改写速率和高成像分辨率; 并且,这种ADC 面积小、功耗低一级优势在便携式医学仪器、安防安检体系运用中也得到了充分发挥。

可是, ADC 的精度和线性度会遭到元件匹配度和体系失调以及噪声等要素的约束, 因而一般需求选用主动失调消除、数字校准等技能以改进其功能。

激光纠正技能一般用以进步转化器中元件的匹配度, 但也一起遭到封装时的机械应力、制作工艺以及生产本钱等问题的影响。

本文供给了一种依据二进制加权电容阵列DAC 的数字校准算法, 将校准差错在芯片测验时测出并烧写到ROM中, 并在ADC 运用时将ROM中的数据读出对应加载到电容阵列中, 完结对DAC 的校准; 一起选用了高效的比较器消除失调技能, 大大进步了ADC 的精度。

2 SAR ADC概述

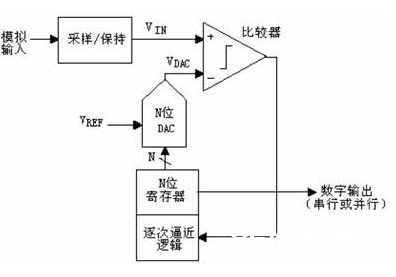

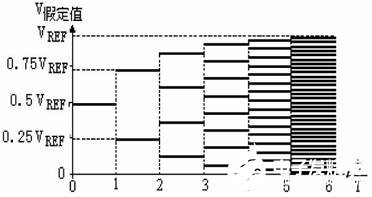

完结逐次迫临式ADC 的办法千差万别, 但其根本结构十分简略。如图1 所示, 模仿输入电压( VIN) 由采样/ 坚持电路坚持。如图2 所示, 为完结二进制算法, N 位寄存器首要设置在中心刻度( 即:100 …….00, MSB 位1) 。这样, 数字模仿转化器( DAC) 输出( VDAC) 被设为VREF/2, VDAC 是供给给ADC 的基准电压。然后, 比较判别VIN 是小于仍是大于VDAC.假如, VIN》VDAC, 则比较器输出逻辑高电平或1, N 位寄存器的MSB 坚持为1.相反, 假如VIN 《 VDAC, 则比较器输出逻辑低电平, N位寄存器的MSB 清为0.随后, 逐次迫临操控逻辑移至下一位, 并将该位设置为高电平, 进行下一次比较。这个进程一向继续到最低有用位( LSB) 。上述操作完毕后就完结了转化, N 位转化成果储存在寄存器内。

图1 N位逐次迫临A/ D 转化器的结构图

图2 A/ D 转化器的逐次迫临进程

3 数字校准算法

现在, 工业界的SARADC 产品以二进制加权电容阵列、分段电容和RC 混合结构三种结构为主, 精度从10 位到18 位不等。其间, 二进制加权电容阵列构成的SARADC 因为低功耗的优势运用更为广泛。

因为CMOS 工艺的约束, 无源器材的匹配精度不高, 二进制加权电容阵列SARADC 转化器只能到达12 位精度。运用激光批改等技能, 能够进步无源器材的匹配精度, 可是本钱较高, 不适于工业生产。因而, 提出了各种自校准办法, 以进步无源器材的匹配精度, 然后进步转化精度。如运用失调子DAC 和校准子DAC 预先对主DAC 的低位充电, 以到达校准的意图; 或运用多位非二进制加权电容DAC 和自校准算法, 使电容匹配到达较高的精度。

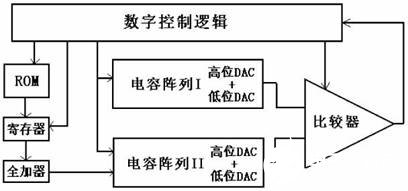

数字校准技能的含义即在ADC 正常运用前, 运用ADC 的已有电路对芯片的非线性要素进行测验,经过必定算法并依据ADC 运用时的时序发生相应的校准码, 加之于存储器中, 在ADC 作业时经过数字操控逻辑将所存校准数据对应加载到电路中, 然后到达校准失配的意图。关于本次SARADC 的规划, 咱们选用结构对称的两组18 位电容阵列数模转化器( DAC) 输入至比较器的正负输入端( 准差分结构) , 如图3, 这种对称输入能够使比较器正负两头输入负载持平, 另一方面, 两电容阵列的高位DAC 可对全差分信号进行采样, 并输出全差分的参阅电压, 而电容阵列I 的低位作为正常的低位子DAC 运用发生SAR 所需的参阅电压, 电容阵列II的低位则用于丈量和校准两组电容阵列高位的非线性。

图3 数字校准算法示意图

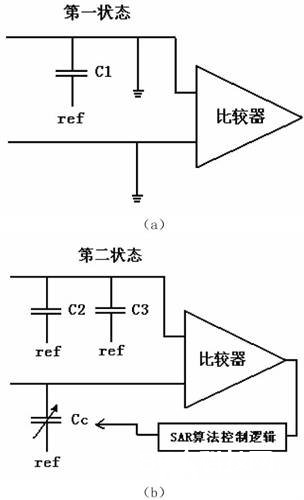

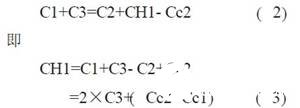

校准码的发生和运用能够有不同的算法, 中介绍了一种由高位到低位校准办法, 本文规划了一种由低位到高位顺次校准的办法。校准测验时电容阵列作业于两种状况: 首要是接入一组电容, 电容阵列输出接地, 即比较器两输入端均为0, 如图4( a) 所示; 然后接入待测电容, 输出直接接入比较器两输入端发生比较成果, 如图4( b) 所示, 依据比较器的输出及外部的查找算法调整电容阵列II 低位DAC 的输出然后测得待测电容所对应的寄生参数( 规划要求此DAC 的精度比正常运用时的DAC 至少高1位) , 经过对此数据的处理便能够得到相应的校准码。为完结由低至高的校准, 测验时需求用到电容阵列I 低位的3 组电容C1, C2, C3, 抱负情况下它们的权值应与两组电容阵列低位DAC 的最高位适当,考虑到不匹配问题, 可设C1≈C2≈C3, 设电容阵列II 低位DAC 接入的电容值为Cc, 依据二进制加权电容阵列性质可知Cc 的等效输出范围在0 到2 倍C1 之间。初度测验时, 榜首状况仅接入C1, 第二状况接到C2, C3 上, 一起电容阵列II 的可变Cc 接入,如图4, 经过调查比较器的输出, 可知, 当比较器输出跳变时, 有:

![]()

Cc1 为Cc 当时值, 可经过外部SAR 算法查找得到。

图4 ADC校准时分为两个状况

接下来即可对高位DAC 的最低位进行测验和校准, 设此位电容权值为CH1, 榜首状况电容接入C1, C3, 第二状况则接入C2, CH1 和Cc, 同理可得:

依上述办法能够推得:

![]()

ΣΔCc 为每位所对应Cc 差值与已校准低位Cc 差值的累加和, 将此电容值对应的二进制码用有符号数标明即所需校准码, 随后能够经过一次性烧写电路存储到ROM中, 完结SARADC 的校准测验。

数字校准的详细完结办法, 可经过增加芯片状况操控端口完结。如表1 中所示, 测验时将两个操控端口接地, 运用上述算法取得校准码; 随后将操控端口P2 接至高电平, 此刻将所需的校准码写入到芯片的ROM中; ADC 正常运用时, 将两个操控端口接到数字电源上即可。各个作业状况的详细逻辑电路完结, 遵从数字集成电路规划规程, 并需针对不同状况对芯片的端口进行装备。

表1 不同的操控端口逻辑完结芯片作业状况的切换

4 比较器失调消除技能

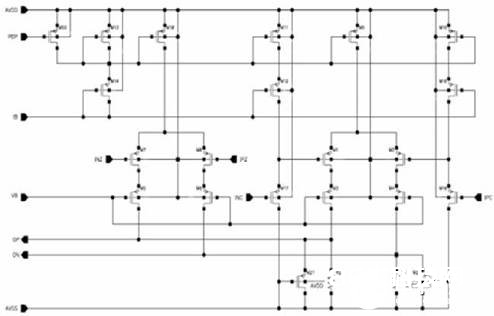

为完结较高的转化速度, 本次规划选用多级比较器结构,由四级低增益放大器和一级锁存器构成, 而高精度的完结需求对比较器进行失调校准技能。比较器的失调电压是因为电路元件的失配形成的, 这种失配一般是随机的, 不能预先估量。失调电压的存在会影响比较器的精度, 在较高分辨率的ADC 中, 输入失调电压不能太大, 这就要运用失调校准技能。失调校准技能在MOS 工艺中是适用的,这是因为MOS 器材的输入电阻近似无限大, 使得晶体管栅极上能够长时间储存电荷, 能够将失调电压储存在电容上, 经过与输入叠加来消除失调电压的影响。本次规划, 咱们选用在每一级放大器参加辅佐输入端的办法, 消除比较器的失调。

图5 运用辅佐输入端消除失调技能

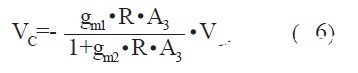

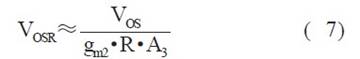

如图5 所示, 主放大器被规划成由两个跨导放大器组成, 因为比较时用于开环, 增益较小, 可用电阻作负载; A3 为反应环路上的调零放大器, 为高增益放大器。消失调时首要, 开关S1 闭合, S2 将主运放两输入接至共模电平, 此刻经过反应环路, 辅佐运放输入端上的电容存储的失调电压设为Vc, 则:

![]()

可得:

当S1 断开, S2 接入输入信号时, 比较器正常作业, 因为Vc 的作用, 能够得到此刻在比较器输入端的等效失调电压为:

依据ADC 的精度和电容阵列的校准算法, 并经过调理辅佐运放和调零运放的增益使多级比较器的精度到达规划要求, 本次规划比较器的精度需高于19 位。图6 为参加辅佐输入端的低增益跨导放大器的电路规划, 本次规划各级前放的增益约为22dB.

调零放大器选用全差分折叠式共源共栅结构, 一方面可完结高增益, 另一方面用于构成单位负反应, 然后可用电容检测并消除本身的失调。本次规划, 该运放增益需求到达70dB 以上, 一起为确保输出共模电平的安稳需参加共模反应。

图6 前置跨导放大器的电路完结

5 仿真成果

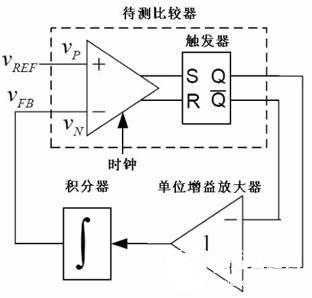

比较器的测验可选用动态失调测验渠道( DOTB) 进行,如图7 所示。此办法运用单位增益放大器、积分器的性质, 将比较器接入环路, 经过对测验精度的调整, 终究得到比较器的等效输入失调。

图7 动态失调测验渠道框图

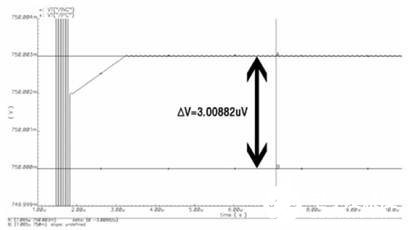

测验成果( 图8) 标明: 参加消失调机制后, 多级比较器等效输入失调约为3μV( 《4μV) , 然后使比较器的精度到达了20 位。

图8 单级比较器动态失调测验成果。

经过对ADC 进行频谱剖析, 丈量其动态功能,即可反映ADC 的精度与线性度,并验证数字校准的作用。为防止频谱走漏[7], 参加的正弦鼓励信号的频率和采样频率应满意如下联系:

Fin、Fs 别离标明输入信号频率和采样频率, Npoint为采样点数, n 为正整数, 且n

图9 ADC正弦鼓励下的频谱剖析( a) 未校准( b) 校准后。

6 定论

本规划经过由低到高顺次校准电容阵列的办法, 改进了电容DAC 的线性度; 运用辅佐输入端消失调技能, 将比较器的精度进步到规划所需的目标。

完结了18bit 的精度要求。选用了多级比较器各级一次性消失调的结构, 进步了ADC 的转化速度; 一起, 电容阵列DAC 的规划和运用使得较低的功耗成为本次SARADC 规划的另一长处。

责任编辑:gt