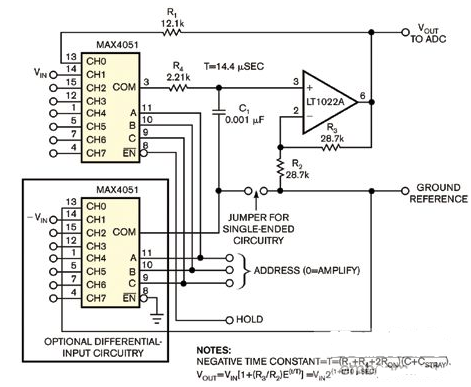

ADC需求有足够的信号收集模仿接口,才干取得最佳功用。传统的通用ADC前端包含多个差分输入通道,数字可编程增益,以及盯梢与坚持功用。本规划实例给出了一个完好的高功用、低元件数的全新ADC前端,完成了整套的规范功用(图1)。不过,它还带有飞跨电容差分输入概念,以及新近一个规划实例所描绘的发散指数负时刻常数(参考文献1)。本规划实例为该电路增加了多工输入以及一个通用的盯梢坚持功用。

图1:这款高功用、低元件数的ADC前端完成了规范功用组。

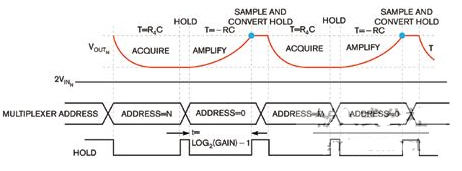

多路器地址与坚持形式状况位操控着信号的收集与整形。当坚持态为零,多路器地址等于所选的输入通道时,飞跨电容C1衔接到正、负差分输入端,用于输入电压的收集。坚持态转化为1时将C1与输入端阻隔。所以多路器地址为0,坚持态回来0,开端对输入电压作负时刻常数的指数扩大。从这一点,直到再次坚持,而且衔接的ADC作采样,以及转化输出电压的点,输入电压和输出电压都是时刻的发散指数函数,增益等于2(1+t/10μs)。

图2:只要扩大期间时序的分辨率约束着增益设定的精度。

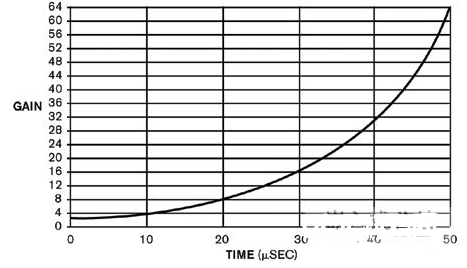

这个新电路建立在较早规划的基础上,具有多台仪器差分输入所需求的特性。别的,电阻匹配问题和运放的CMR(共模按捺)都不会约束电路的 CMR。杂散电容是对CMR的一个影响要素,但可以经过电路的精心布局,尽可能削减这一电容。电路亦有轨至轨的输入,以及简直无约束的可编程增益。此外,增益设置的分辨率只受扩大期间的时序分辨率影响(图2和图3)。此电路亦有±10V的输出起伏,比单片数字可编程增益外表扩大器要高出一至三倍。

图3:这个输入、输出电压增益图给出了盯梢/扩大逻辑转化的持续时刻。

所选运放的固有噪声与直流精度、指数时序生成的精度与可重复性、ADC采样分辨率,以及RC时刻常数的稳定性等,都是信号处理功用和扩大器精度的首要约束要素,如其增益设定精度、直流差错、噪声以及颤动等。在电路中,1 ns的扩大期间时序差错或颤动就相当于0.007%的增益设定差错。

责任编辑:gt