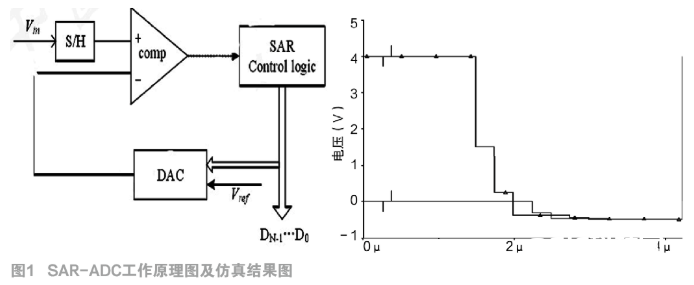

1、 SAR-ADC作业原理

逐次迫临转化器(SAR-ADC)由采样坚持、比较器、DAC和数字操控逻辑组成,其作业原理图如图1所示。而数字操控逻辑由逐次迫临寄存器(SAR)和操控逻辑组成。其详细作业进程如下:

●模仿输入先通过采样坚持送到比较器的一端,转化开始时,数字操控逻辑将逐次迫临寄存器(SAR)的最高位(MSB)置为1,其他位为0。

●DAC在SAR和操控逻辑的操控下,将Vin《Vref,送入到比较器的另一端, 此刻Vin和1/2Vref进行,假如Vin》1/2Vref,比较器输出1,则SAR最高位为1,假如Vin《1/2Vref,比较器输出0,SAR最高位输出0。

●以此类推确认到SAR的最低位,完结N位数字码的确认,此刻得到的数字量即为模仿输入的二进制代码。

2 、12bitSAR-ADC的规划与仿真

2.1原理规划说明

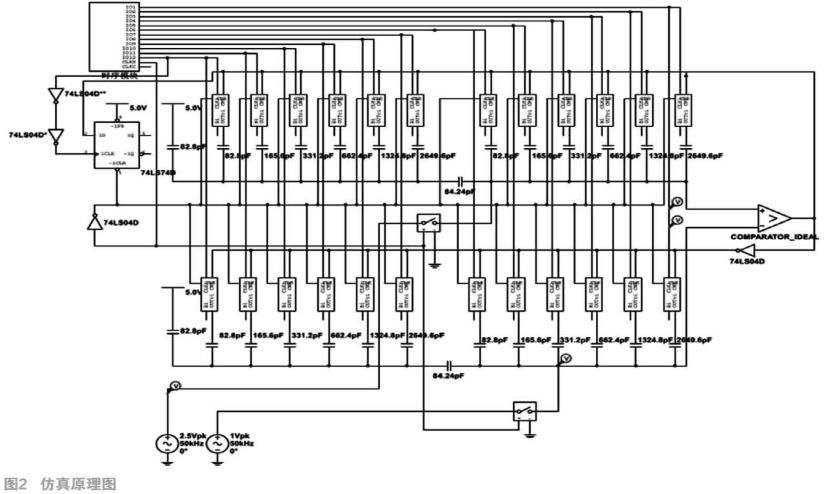

该规划的12bitADC具有低功耗和高精度的特色。它的原理图如图2。全差分的输入信号经采样开关和电荷定标型DAC阵列后,输入到比较器的两头。比较器的成果输入到SAR操控逻辑(即DAC电平切变电路),SAR操控逻辑可以依据比较器的成果来操控电容DAC阵列的电平切换开关,使DAC阵列的电荷从头分配。因而比较器的输入发生变化,然后鄙人一个时钟的低电平进行比较,并持续将比较成果送入SAR操控逻辑,之后不断重复。在12个比较周期后,可由SAR的输出得到12位数字成果。此刻体系复位,等候下一次比较。

电路图左上角是时序发生电路,由此为ADC供给采样时钟,比较时钟;中心部分是SAR操控逻辑(即DAC电平切变电路)和电容DAC阵列;最右边是抱负比较器;左下方是差分输入的正弦信号。

由图中可见,差分输入的正弦信号经采样开关输入到电容DAC阵列中和抱负比较器的两头。之后比较器的输出输入到SAR操控逻辑然后操控DAC阵列的电平切换,使比较器的输入发生变化。而数字成果可由SAR操控逻辑输出。

SAR ADC电路的缺陷是转化位数较高时,精度简单缺乏。因而针对12bit的ADC,咱们对时序发生电路和SAR DAC模块电路部分进行了立异式规划,然后来进步ADC的转化精度,详细的规划细节将鄙人面的各电路模块规划予以介绍。

2.2各模块规划说明

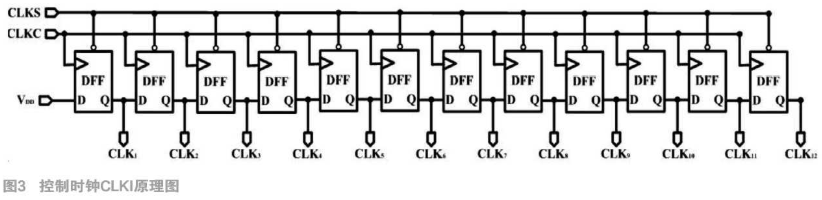

2.2.1操控时钟发生电路

如图3所示,操控时钟发生电路由采样时钟CLKS和比较时钟CLKC以及12位移位寄存器级联而成。CLKI的发生原理为:

●当CLKS为1时,CLKC、各CLKi信号均置0,此刻体系作业在采样/坚持阶段;

●CLKS为0时,此刻体系作业在比较阶段,发生12周期CLKC信号,并由CLKC操控移位寄存器的信号传递(上升沿触发),然后发生CLK1-CLK12的操控时钟。

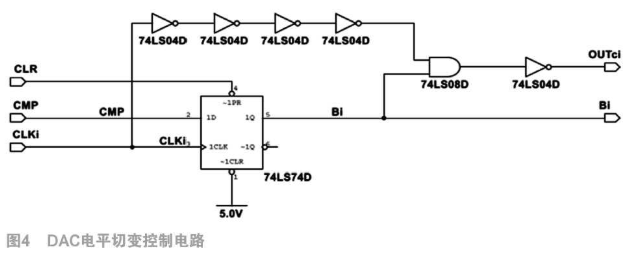

2.2.2DAC电平切变操控电路

DAC电平切变操控电路首要功能是依据比较器的输出成果来操控电容阵列的电平改换。为了更好的完结差值电平的减半比较,本规划选用图4所示的电路结构。

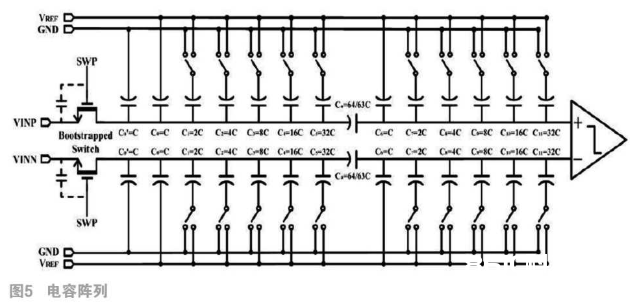

2.2.3电容阵列

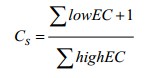

为了完结逐次迫临ADC的低功耗DAC,咱们选用了电荷定标型结构,一起选用并行二进制加权电容阵结构。考虑到本规划所做的是12bitADC,那么12位DAC就需要4096个单位电容,会占用较大芯片面积一起导致转化速度下降。为了处理上述问题,DAC选用分段电容阵列结构。如图5所示,考虑到桥接电容两头的二进制加权电容阵列位数持平时,整个逐次迫临的ADC总电容最小。因而在高6位与低6位之间用一个桥接电容Cs分隔,一起低四位二进制加权电容阵列还会接一个与单位电容等值的C。选用该种规划可以将电容的数量从4096削减到约128个。因而ADC的速度更快,功耗更小,芯片面积也更小。关于单位电容C的选取,本规划归纳考虑减小功耗和按捺噪声的影响,挑选单位电容的容值为82.8pf。桥接电容Cs

核算可得Cs=84.11pf。归纳考虑到AD转化的精确度和累计差错,桥接电容的容值为84.24pf。

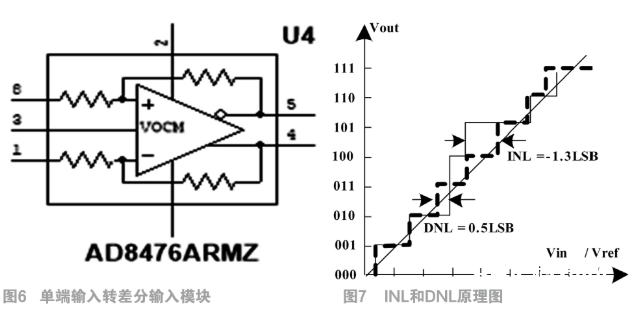

2.2.4单端输入转差分输入模块

考虑到所规划的ADC是差分输入,而一般信号都单端输入方法。因而在电路中附加了单端输入转差分输入模块AD8476,以确保差分信号同相以及充沛按捺共模信号,如图6。

2.2.5 12bitADC电路规划立异点

(1)选用逻辑门与触发器的方法发生时钟信号,静态功耗极低,动态功耗较小。

(2)电容阵列选用分段电容,加入了桥接电容,大大减小了电容面积,进步了ADC的速快,下降了功耗。

3、ADC测验目标介绍

3.1静态目标

分辩率

分辩率是指ADC可以分辩量化的最小信号的才能。如12位bit的ADC的分辩率为Vref/4096。

失调差错

界说为输入信号为零时输出信号不为零的值,失调差错会使实践的传递函数与抱负传递函数间存在一个固定的偏移。

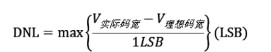

微分非线性

微分非线性(differentialnonlinearity,简称DNL)指在消除失调差错和增益差错后,实践搬运的台阶电压与抱负台阶电压(LSB)之差。其核算公式如下。其间,V实践码宽为实践丈量1LSB对应的电压宽度;V抱负码宽为抱负的1LSB电压宽度。

其间, V实践码宽为实践丈量1LSB对应的电压宽度; V抱负码宽为抱负的1LSB电压宽度。

积分非线性

积分非线性(Integratednonlinearity,INL)指在消除失谐和增益差错之后,实践传输函数违背抱负中心线的程度。其核算公式如下。

![]()

其间Vreal为实践丈量的台阶电压值;Videal为抱负的台阶电压值。INL和DNL的原理如图7所示。

3.2动态目标

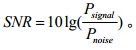

信噪比

信噪比(Signal—to—NoiseRaTIo,缩写为SNR)指的是ADC满量程单频的正弦波输入信号功率与ADC输出信号在奈奎斯特带宽内的悉数其它频率重量(不包含直流调和波重量)的总功率之比。理论上,ADC的信噪比取决于体系的位数。

其理论核算公示如下。

![]()

实践丈量时,其核算公式如下。

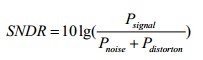

信号噪声失真比

信号噪声失真比也称为信纳比,可简写为SNDR,指的是ADC满量程单频的正弦波输入信号功率与ADC输出信号在奈奎斯特带宽内的悉数其它频率重量(包含噪声和一切谐波重量)的总功率之比,通常用dB表明。其核算公式如下。

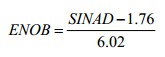

有用位数

关于一个非抱负ADC,由于输出中量化噪声和失真引起的高次谐波的存在,实践的转化位数小于N。因而ADC实践的转化位数称之为有用为数,其可由丈量出的信纳比算出。其核算公式如下。

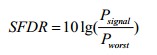

无杂散动态规模

无杂散动态规模是指ADC输出频谱中信号功率(Ps)与最大谐波重量功率(Pworst)的比值。其核算公式如下。

总谐波失真

一般缩写为THD,界说为体系一切谐波的总功率与输入信号功率之比。它可供给体系对称和非对称非线性发生的总失真巨细,用以表达其对信号的谐波含量的效果或许影响。其核算公式如下。

实践丈量时,常用码密度法来丈量DNL和INL,用FFT分析法来丈量动态目标。

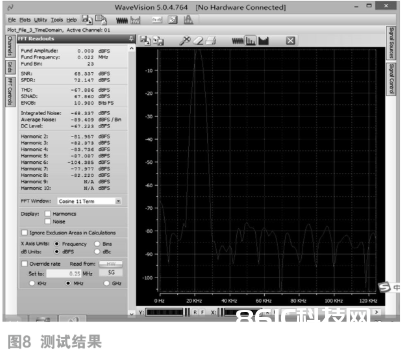

4、电路测验成果

输入正弦波

差分输入,别离输入起伏为2.5V,电压偏移为2.5V,频率为22Khz的正弦波和起伏为1.5V,电压偏移为2.5V,频率为22kHz的正弦波。

根据wavevision测验成果从图8中可读得:

信噪比(SNR)=68.887dBFS;

最大杂散动态(SFDR)=72.147dBFS;

总谐波失真(THD)=-66.886dBFS;

信纳比(SINAD)=67.860Dbfs;

有用位数(ENOB)=10.980bits。

作者简介:

张彪,1996年生,男,本科生,首要从事信号处理方向的学习与研讨;莘济豪,1997年生,男,本科生,首要从事信号处理方向的学习与研讨;梁文哲,1996年生,男,本科生,首要从事信号处理方向的学习与研讨。