触发器是一个具有回忆功用的二进制信息存储器件,是构成多种时序电路的最根本逻辑单元。触发器具有两个安稳状况,即“0”和“1”,在必定的外界信号效果下,能够从一个安稳状况翻转到另一个安稳状况。

触发器:具有回忆功用的根本逻辑电路,能存储二进制信息(数字信息)。

触发器有三个根本特性:

(1)有两个稳态,可别离表明二进制数码0和1,无外触发时可维持稳态;

(2)外触发下,两个稳态可彼此转化(称翻转),已转化的安稳状况可长期坚持下来,这就使得触发器能够回忆二进制信息,常用作二进制存储单元。

RS触发器是构成其它各种功用触发器的根本组成部分。又称为根本RS触发器。结构是把两个与非门或许或非门G1、G2的输入、输出端穿插衔接。

根本RS触发器、同步RS触发器、D触发器

具有回忆功用的门电路,作业特征与上述两种根本门和可控门数字电路,有了质的差异。现在的输出成果并不必定是“现在的”输入信号所导致的,可能为“过去时”,即“已消失”输入信号动作后的存储成果,电路有了“回忆的”才能。电路的动作办法,也一改输入信号的“长时收效”而变为“瞬时信号”的触发机制。

是具有回忆功用,能贮存一位二进制信息的逻辑电路。

该类电路,即数字电路中的根本RS触发器、同步RS触发器、同步D触发器、主从触发器、边际触发器等和在此根底之上的时序逻辑电路,而整个数字电路的大厦,也即由组合逻辑电路和时序逻辑电路所构成。

1、根本RS触发器

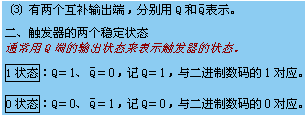

1)由与非门构成的根本RS触发器

由两个与非门电路穿插耦合即构成根本的RS触发器,因为电路中G1、G2效果相同,习惯上用逻辑符号予以表明。

具有回忆功用门电路之根本RS触发器、同

图1 由与非门构成的根本RS触发器

/RD、/SD为触发器的两个输入端,/SD称为置位(或置1)端;/RD称复位(或置0)端。在标示字母上方加短杠,表明低电平信号有用。触发器还有两个输出端,两者的逻辑电平相反,以Q端为基准。如Q=1,则/Q=0。

从电路结构来看,因仅有两个输入端子,则输入有四种电平组合,在适合的信号效果下,触发器能够从一种稳态翻转至另一稳态。

当/SD=0,/RD=1时,触发器置1;

当/SD=1,/RD=0时,触发器置0;

当/SD=0,/RD=0时,呈现输出竞赛现象,为不合法输入电平(正常使用时应防止呈现这种状况);

当/SD=1,/RD=1时,输出坚持不变。

综上所述,根本RS触发器具有置0、置1和坚持功用;但输入信号不能一起为0,是具有约束条件的触发器。

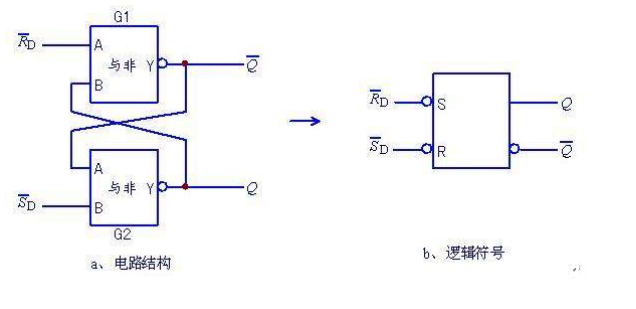

2)由或非门构成的根本RS触发器

用两个或非门穿插耦合,也可构成根本RS触发器,其电路结构和逻辑符号如图2所示。

具有回忆功用门电路之根本RS触发器、同

图2 与或非门构成的根本RS触发器

RD和SD别离为复位(置0)和置位(置1)端,与图1电路有所不同,它们均是高电平有用。其信号输入也有四种组合。当RD=0,SD=1时,触发器置1;当RD=1,SD=0时,触发器置0;当二者都为1时,触发器状况不确认(为不合法电平);当RD=0,SD=0时,触发器坚持原状况不变。

与一般门、受控门电路比较,前者输入为常态信号,输出状况取决于即时输入;后者输入为“瞬态”信号,有触发特性,输出有坚持功用,输出为输入的“过去时”,输入条件成立时输出坚持。输入信号存在约束条件,约束了其实用性。RS根本触发器是没有实践使用IC器材的,实践使用器材是在此根底上将功用提高后的IC产品,如同步RS触发器,同步D触发器等系列产品。

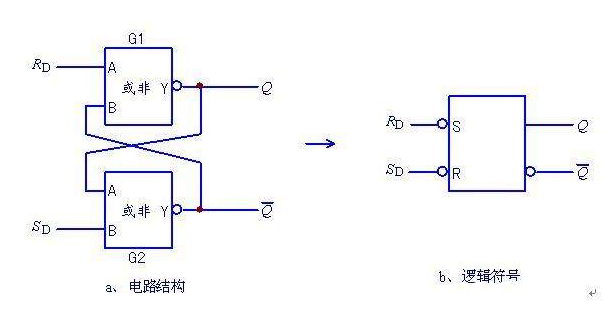

电路实例:三态R-S锁存触发器CC4044B。内部电路结构与引脚功用见下图。

图3 CD4044B三态R-S锁存器

将根本的R-S触发器加以改造,如在输出侧增设传输开关,就可得到具有三态传输功用的R-S触发器。从其内部电路结构可看出,a)添加了EN使能操控端,高电平为通态,低电平为关态;b)添加了受控输出级,为三态输出办法,当EN端为低电平时,输出级相对于外部电路,为高阻态(三态)。

从检修视点动身,咱们需求留意的着重点是在线怎么确认芯片好坏,并找到(引脚功用、尺度适合的)代替元件。

检修关键:

a)在高阻(传输关断)态,输出端电平不取决于输入信号,而由电路设计者人为限制(由外加上拉、下拉电阻的确静态高、低电平);

b)在正常传输(EN端为高电平)状况,具有根本R-S触发器的作业特性:可置0、可置1、输出坚持。能够经过对此三特性的验证来确认芯片好坏。

和一般门电路不同,现在的输出是“过去时”,不是对即时的输入信号作出的反映。欲的确电路好坏,需人为改动一下输入电平——进行置0或置1操作,据输出端做出的反映,的确判别芯片的好坏。必定条件下,咱们能够在输入端做出“人为动作”,来迫使输出端作出相应的反响。其实任何器材,都不难找到相应的检修和判别办法,器材的正常作业与否即便如雪泥鸿爪,也总会“有迹可寻”。为此,需求研讨触发器的输入电路办法,并据此选用相应的“人为动作”,而不会导致在线器材(如触发器的前级电路)的损坏。

对器材检测最好的办法,是上电检测输入、输出状况得出结论,远比丈量引脚电阻、摘下后放入IC测验仪进行检测,更为便利和精确。这是因为其外围电路及供电条件,现已供给了最为优秀的检测条件!

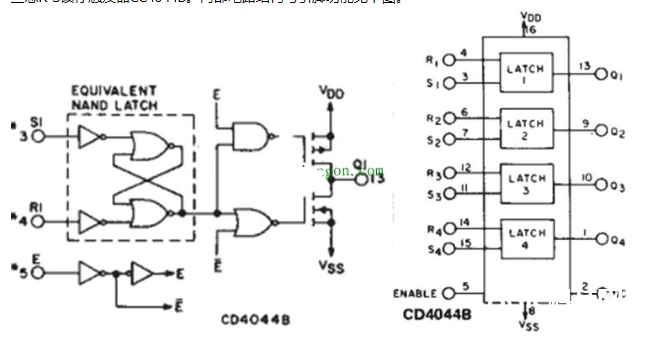

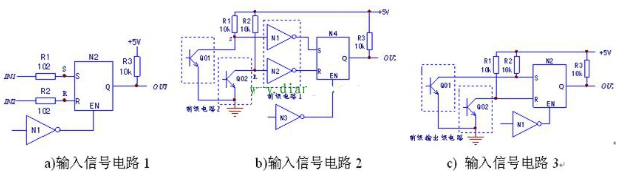

触发器的输入信号电路办法:

图4 触发器输入信号电路办法

图4中a)电路,因输入信号回路串入了R1、R2阻隔电阻,因而前级输入电路是何办法不再重要。该触电器为高电平信号输入有用,可知其常态(或静态)R、S输入端应该为低电平。在首要的确EN端为高电平(的确电路为通态)状况下(若EN端为低电平,阐明处于关态——高阻态,需查低电平原因并扫除之),若测Q端为低电平,此刻将图中S点与+5V短接一下(即输入置1信号),再测Q端应由0V变为5V高电平,并坚持。阐明N2芯片是好的。反之,若Q端为高电平,将图中R点与+5V短接一下(即输入置0信号),而Q端就变为低电平并坚持。不然阐明芯片已坏。

图4中b)电路,其信号输入前级电路为反相器电路,其内部输出级为电压互补放大器结构,N1、N2输出端静态为低电平,此刻若轻率将N4的R、S端与+5V短接制作人为高电平信号,则因形成N1、N2输出级对+5V电源短路而损坏N1、N2器材。在N1、N2的输出端无法做手脚,则然后往输入端电路查找,总能找到着手的当地。该前级电路2为开路集电极输出结构,接有R1、R2上拉电阻。此刻将Q01、Q02的集电极与供电地短接一下,即能便利地制作置0或置1信号,然后的确N4触发器电路的好坏。

同理,处理EN端电路,也可用类似办法,制作通态信号,以发明触发器的动作检测条件。

图4中c)电路,该电路是高电平有用触发办法,因而制作高电平的置1或置0信号,仅需短接Q01、Q02的发射结使其处于截止状况即可。

别的,若前级电路为三态门,将三态门处于高阻态时,此刻可在N2的R、S端随意制作高、低电平信号,如将R、S端接地或接+5V。但若三态门处于通态时,则应在三态门的输入端想办法,制作信号了。

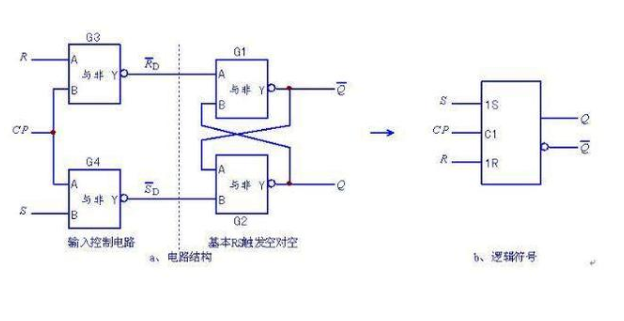

3)同步RS触发器

根本RS触发器只需输入信号改动,输出状况就会当即发生相应改动,这不光使得电路的抗干扰才能变差,也给多个触发器的同步作业带来不方便。在实践使用中,一般要求触发器的状况按必定的时刻节拍改动,即在时钟脉冲抵达时,才依据输入信号改动状况;没有时钟信号时,即便输入信号改动,也不影响触发器的输出状况。为此,添加时钟脉冲输入端CP以及相应的输入操控电路,就有了同步RS触发器这一类数字芯片。

同步RS触发器的电路结构和逻辑符号如图5所示。

图5同步RS触发器

与非门G1、G2构成根本RS触发器,G3、G4构成输入操控电路。作业原理如下:

①CP=0期间,与非门G3、G4被封闭,/RD=1,/SD=1。因而,不管输入信号R、S怎么改动,都不会影响触发器的输出Q和/Q,即触发器状况坚持不变。

②CP=1期间,与非门G3、G4翻开,输入信号R、S反相后加到由G1、G2构成的根本RS触发器电路,使Q和/Q的状况发生改动。

同步RS触发器的功用或状况,可由状况搬运表来描绘(此不赘述)。

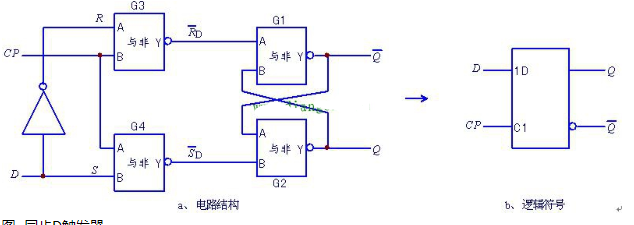

4)同步D触发器

同步RS触发器在R、S一起为1且一起失效后,触发器状况不确认,阐明其功用仍不完善。D触发器针对这一问题作出改善,处理了触发器状况不确认的问题。

因为只需令R、S不一起为1,触发器就不会呈现状况不安稳,最简略的办法便是令S=/R,此刻仅将S作为输入端(用D表明),就得到了D触发器。仍然是由RS触发器演化而来,是RS 触发器S=/R的特例,其电路结构和逻辑符号如图6所示。

图6 同步D触发器

作业原理如下:

①CP=0期间,与非门G3、G4被封闭,/RD=1,/SD=1。因而,不管输入信号R、S怎么改动,都不会影响触发器的输出Q和/Q,即触发器状况坚持不变。

②CP=1期间,与非门G3、G4翻开,触发器输出状况随D而改动,完结置0、置1和坚持等三种逻辑功用。

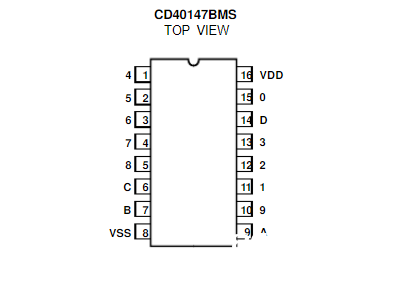

5)双主-从D型触发器电路检修举例

触发器系列电路办法太多,一会儿彻底搞理解是不必要的(不可能悉数记住,用得多的会天然把握)。以双主-从D型触发器CD4013为例,在没有全面深入把握原理及内部电路结构的前提下,能否依据端子功用快速把握其检修办法呢?答案是必定的。

操控电路的核心部件为双D触发器,型号为CD4013,内含两个独立的D触发器。从R、S或C端子承受上升沿触发信号,能使输出状况发生翻转。常用来组成单稳态、双稳态、无稳态电路。如图7-10所示,是内部一路D触发器的引脚功用图。

图7 CD4014的引脚功用图

咱们先把握CD4013的两个使用办法,从中体会其电路原理及动作办法:

a)双稳态电路。在数据端D和时钟端C都接地的状况下,在置位端S加一个脉冲高电平,则Q输出端变为高电位(被置位);在复位端R加一个脉冲高电位,输出端Q变为低电位(被复位)。端为Q端的反相输出。

依据此准则(或满意此检测条件下),CD4013“变身”为一般R-S触发器,在R、S端施加瞬时高电平信号,即可完结置0、置1及坚持功用检测。

b)数据检出电路。置位端S和复位端R都接地的状况下,在C端时钟脉冲效果下,D数据端的数据(0或1)被传输至输出端Q。D端只需0或1两个数据状况,C端上升沿脉冲效果期间,D端的数据为Q端所检出。

依据此准则(或满意此检测条件下),可在其时钟端人为施加“0”或“1”信号,检测Q端和D端数据传输状况,由此精确判别芯片好坏。

由上述,因而对如我——一位较懒散的检修人员来说,检测数字电路的好坏,无需研讨其冗杂的时序图,也不必管它传输频率是多少和详细的传输数据是什么,电路仅为凹凸电平信号处理器,或仅为传输一个直流5V和直流0V的信号电路。输出是此两种状况,而输入信号亦为此两种状况。彻底可用0V和5V充任输入端检测信号,检测输出端的5V和0V改动,只需电路是听话的讲理的,便是好的电路。