从开端的占地170平方的第一代ENIAC计算机开端,计算机开端了不断集成化、小型化的开展之旅。如今在单一芯片内部现已能够集处理器,存储,各型协处理器等,然后构成的强壮的单芯片的片上体系(SOC),而这些片上体系已存在于日子的方方面面。因而FPGA内部支撑片上体系,也算不上是别致的作业了。ALTERA和XILINX已各自推出了各自运用片上体系(FPGA范畴称之为SOPC,因而其片上体系能够依据事务需求来界说)。

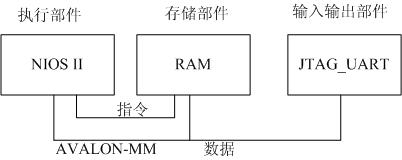

只需几K的资源,就能完结一个SOC的最小体系,关于FPGA工程师来说,没什么比这个更有吸引力了。那么,作为一个片上体系来说,其最小体系应该包含哪些:其至少需求三个部件,履行部件(处理器),程序履行部件(内部存储器),输出部件(输入输出单元)。(其别离相当于PC上的CPU、内存条,键盘鼠标显示器)。下图所示在ALTERA的QSYS上完结NIOS的最小体系所需部件。

(1) 处理部件:NIOSII为ALTERA器材中所专有的软核处理器,而xilinx所对应的为microblaze的软核。经过在Qsys的界面东西中供给许多IP,而NIOSII也供给三个版别供给运用,别离是高速型,标准型,以及经济型。假如FPGA内部逻辑有限,可挑选的经济型,其占用资源较少。假如需求内部资源丰富又需求运转嵌入式操作体系uclinux等杂乱软件。则主张挑选高速型,而要运转linux等操作体系,则在NIOSII高速型中装备MMU则是有必要的。如无详细需求,则运用标准型即可。值得一提的是,NIOSII为哈佛型体系结构,即数据和指令分隔,从Qsys能够看出,其接口分为指令接口和数据接口。

(2) 存储部件:关于在FPGA内部完结SOC来说,片内的块RAM便是完结SOC内部程序与数据的存储空间。也能够运用片外的存储区,如片外SRAM或许DDR等。也能够作为程序和数据的存储空间。关于NIOSII处理器来说,只要选取了片内存储区或许片外存储区,才干设定程序中止向量和复位开始方位的存储区。别的,尽管AVALON总线支撑数据总线和地址总线经过片上互联同一接口拜访单端口RAM。但主张运用时,例化为双AVALON接口的双端口RAM,一则是因为一般存储区所需RAM深度够大,一般支撑真双端口RAM,另一方面,数据和指令分隔,能够提高体系的功能。

(3) 输入输出部件:通常在嵌入式SOC体系中,最常用的输入输出部件便是串口(UART)。常常被运用于(打印printf(),scanf())函数的输入输出。假如体系规划了串口(一般为SOC体系中所有必要的),则例化体系中的支撑avalon接口的串口即可,假如体系中不幸没有,那么ALTERA公司供给了JTAG-UART接口供给给用户输入输出交互接口。即经过复用JTAG下载线来模仿串口的操作。假如体系中有多个输出输出设备,如有多个UART,则在编程时,需在BSP的环境中设定,挑选运用哪个UART作为体系的输出。

运用ALTERA的Qsys东西能够便利的在FPGA上构建SOC体系。只需挑选相应的IP(能够是体系自带,也能够运用自己构建支撑avalon-mm接口的IP)。经过体系的互联然后构成一个片上体系。图形化的界面只需经过avalon总线衔接信号将NIOSII和外设衔接在一起即可。衔接完毕后,还需求下面操作:

(1) 为每个外设设定地址,例如上图中RAM和JTAG-UART,每个外设都需求一个地址规模,能够点击体系中主动地址分配,也能够手动分配一个区间。只要为每个外设分配地址后(相当于整个体系的门牌号),处理器才干依据地址来拜访各个外设。

(2) 如外设有中止,则为外设分配中止号,也可主动或许手动完结。如不分配中止的话,那么处理器拜访外设,只要查询一种交互方法了。中止方法运用能够削减处理器的负载。

在ALTERA的QSYS东西中,硬件信息悉数存储在sopcinfo。主要是包含各个外设的地址信息等,用于发生system.h。也便是说,作为软件和硬件的交互的途径是每个外设的基地址,中止,和内部寄存器等信息。体系构建完毕后,剩余的就能够软件编程了,运转在建立的SOC体系上的第一个“hello world”的程序。

关于现在FPGA上的SOC规划,厂商为了其便利易用,做了很多的作业,只需依照其攻略一步步,就能够完结相应的规划,但一起,也约束了对其基本原理的深化的了解。什么作业都有其两面性,作为FPGA工程师,SOC的原理则应该能够要点重视,这样不论是ALTERA仍是XILINX其基本原理也是共同的。如不运用厂家的处理器核(NIOSII、microblaze),也能够运用其他的软核(如51等,ARM)在FPGA上完结SOC体系。只不过本来东西做的作业,就需求手动来完结了。

linux操作体系文章专题:linux操作体系详解(linux不再难明)