FIFO在FPGA规划中除了上篇所介绍的功用之外, 还有以下作为以下功用运用:

(1) 内存请求

在软件规划中,运用malloc()和free()等函数能够用于内存的请求和开释。特别是在有操作体系的环境下,能够确保体系的内存空间被动态的分配和运用,十分的便利。假如在FPGA内部完成此动态的内存分配和请求,相对来说较为杂乱,例如某些需求外部数据存储且需动态改动的运用需求下,需求对FPGA外部DDR(或SRAM等)的存储空间,进行动态的分配和开释。经过运用FIFO作为内存分配器,尽管比不上软件的灵敏和便利,可是运用也较为简洁。

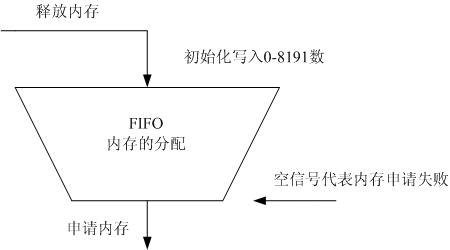

举例说明假定外部存储空间为8Mbyte,可将其区分为8192个1Kbyte空间。并将数值0-8191存储FIFO中,FIFO内部存储所标明可用的内存空间。如下图所示。

首要,进行内存的初始化,行将0-8191写入FIFO中。

如需请求内存后,从FIFO中读取值A,然后依据A的标明,写入A所指示的外部存储区(DDR)中相应的方位,即请求{A,10’h0_00} ->{A,10’h3_FF}的空间区域。

如开释内存后,即可向FIFO中写入相应的值。即可确保下次该空间能够被规划运用。

在此种规划中,FIFO承当了内存分配和开释器的人物。此刻只能请求或开释最小单元倍数的内存空间,如本例所示:为1Kbit。如FIFO读空,则代表请求内存失利,需求等候其他块内存开释后再写入FIFO中,才干再次请求。

(2) 串并转化

关于串并转化,或许关于FPGA工程师来说,十分常见,可是假如有专门的IP完成此功用,可简化规划,削减犯错及验证的工作量。例如:关于外部输入的需求进行串并转化的信号,并进行存储的信号,如规划进行串并转化在存储等操作,规划,能够直接经过例化读写位宽不一致的FIFO,例如1入8出的FIFO,可直接将外部输入信号直接转化成8BIT信号并进行存储后,供后续处理运用(其他的)。

(3) 事务优先级区分

经过FIFO设置不同水位线,能够区分不同的事务优先级,确保高事务优先级数据流在带宽受限时,优先经过,而低事务优先级只能在满意高优先级需求后有剩余的带宽时才干经过。而且能够区分多个优先级,满意多种事务的需求。规划将在今后篇幅中胪陈。

(4)固定带宽设定

经过对FIFO接口的读出使能,能够确保完成固定带宽的输出,例如FIFO读接口为32bit,而读时钟为50Mhz,则输出为1.6Gbit/S。如完成固定带宽的输出(如1Gbit/S),有两种方法,一种能够经过下降时钟频率到31.25Mhz。另一种方法,可经过读信号中心刺进等候周期,假如读出长度为N的数据所需时钟周期为M,则需等候(3M/5)的周期,然后下降至1Gbit/S的处理才能,这在某些需求进行流量约束的事务方法中运用。

关于FIFO来说,作为FPGA内部资源的一个常用器材,最常见运用于异步时钟域区分和缓冲数据,但不仅限于此,简化规划、削减耦合、输入输出接口固定,便于仿真和验证,都是运用FIFO带来的规划上的好处。