FPGA其在许多器材中能够被工程师喜爱的一个很重要的原因便是其强悍的处理才能。那怎么能够做到高速的数据处理,数据的并行处理则是其间一个很重要的办法。

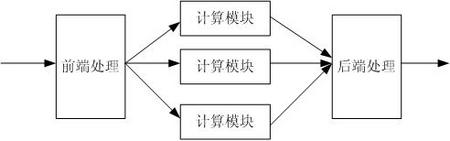

数据的并行处理,从结构上十分简略,可是规划上却是适当杂乱,关于现有的FPGA来说,尽管各种FPGA的容量都在添加,可是在有限的逻辑中到达更高的处理才能则是FPGA工程师面对的应战。常用并行核算结构如下图所示:

上图中:前端处理单元担任将进入数据信息,分配到多个核算单元中,图中为3个核算单元(几个依据所需的功能核算得出)。然后核算单元核算结束后,交给后端处理单元整合为一致数据流传入下一级。假如单个核算单元的处理才能为N ,则经过并行的办法,依据并行度M,其核算才能为N*M;在此结构中,涉及到几个问题:

一, 前端处理单元怎么将数据分配到多个核算单元,其间一种算法为round-robin,轮番写入下一级核算单元,这种办法一般运用用核算单元核算数据块的时刻同等。更常用的一种办法,能够依据核算单元的标明,即忙闲状况,假如哪个核算单元标明为闲状况,则分配其数据块。

二, 核算单元和前后端处理之间怎么进行数据交互。一般来说,核算单元处理频率较低,为要害途径地点。前后端处理流量较大,时钟频率较高,因而经过异步FIFO衔接,或许双端口RAM都是适宜的办法。假如数据可分块核算,且块的巨细不定,主张运用FIFO作为阻隔手法,一起运用可编程满信号,作为前端处理辨认核算模块的忙闲标明。

三, 假如数据有先后的标明,即先核算的数据需求先被送出,则后端处理模块需求额定的信号,确认读取各个核算模块的次序。这是由于:假如数据等长,则核算时刻等长,则先核算的数据会先被送出。可是假如数据块不等长,后送入的小的数据块肯能先被核算结束,后端处理单元假如不辨认先后核算的数据块,就会形成数据的乱序。这能够经过前端核算单元经过小的FIFO告诉后端核算单元获悉首要读取那个核算单元输出的数据,即便其他核算单元输出已准备好,也要等候依照次序来读取。

数据的并行处理是FPGA常用的提高处理功能的办法,其长处是结构简略,经过核算单元模块的复用到达高功能的处理。缺陷,清楚明了便是到达M倍的功能就要要消耗M倍逻辑。

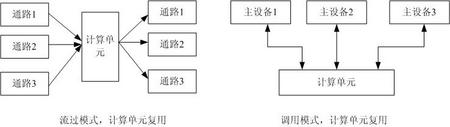

与之相反削减逻辑的另一种办法,则是复用,即一个处理才能较强的模块,能够被N的单元复用,经过复用,而不必每个单元例化模块,能够到达削减逻辑的作用,但操控杂乱度就会上升。其结构图如下所示:

上图复用的结构图中,别离介绍了流过形式复用和调用形式复用。流过形式下,核算单元处理多路数据块,然后将数据块分配到多路上,这种状况下,经过round-robin能够确保各个通路公正时机取得核算单元。其处理思路与上图描绘并行处理相似。

调用形式下,核算单元被多个主设备复用,这种架构能够经过总线及裁定的办法来使各个主设备能够获取核算单元的处理(有许多老练的比如可供运用,如AHB等)。假如多个主设备和多个核算单元的状况,则能够不经过总线而经过交流矩阵,来削减总线处理带来的总线瓶颈。

实践运用场合,规划的架构都应简略有用为好,交互矩阵尽管有用灵敏,但其逻辑量,鸿沟测验验证的难度都较大,在需求灵敏支撑多端口互联互通的状况下运用,可谓物尽其用。但假如只是用于一般核算单元才能复用的场景,就归于过度规划,其能够经过化简成上述两种简略形式,到达高速的数据处理的作用。

并行和复用,尽管是看其来特点相反的操作,但其本质上便是经过处理才能和逻辑数量的平衡,从而以最优的战略满意项目的需求。规划如此,人生亦然。