摘要

本文讨论ADI公司新推出且具有广泛商场的LIDAR原型制造渠道,以及它怎么通过供给完好的硬件和软件处理计划,使得用户能够树立其算法和自界说硬件处理计划的原型,然后协助客户缩短产品开发时刻;具体介绍模块化硬件规划,包括光接纳和发送信号链、FPGA接口,以及用于长间隔感测的光学器材;介绍体系分区决议计划,以凸显杰出的体系规划、接口界说和适宜的模块化分级的重要性;描绘开源LIDAR软件仓库的组件和渠道定制的API,显现客户在产品开发期间怎么获益,以及怎么将这些产品集成到其终究的处理计划中。

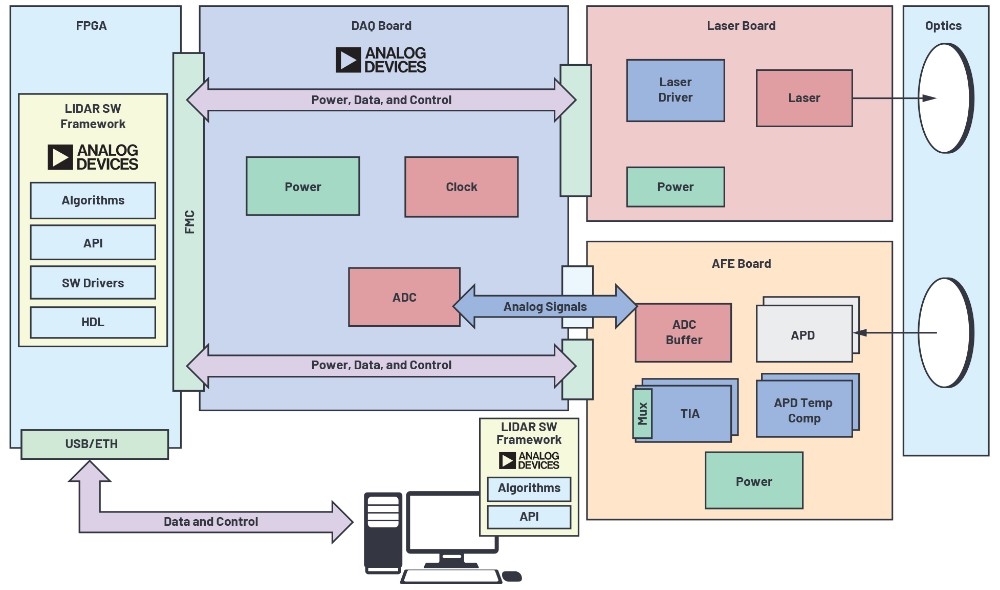

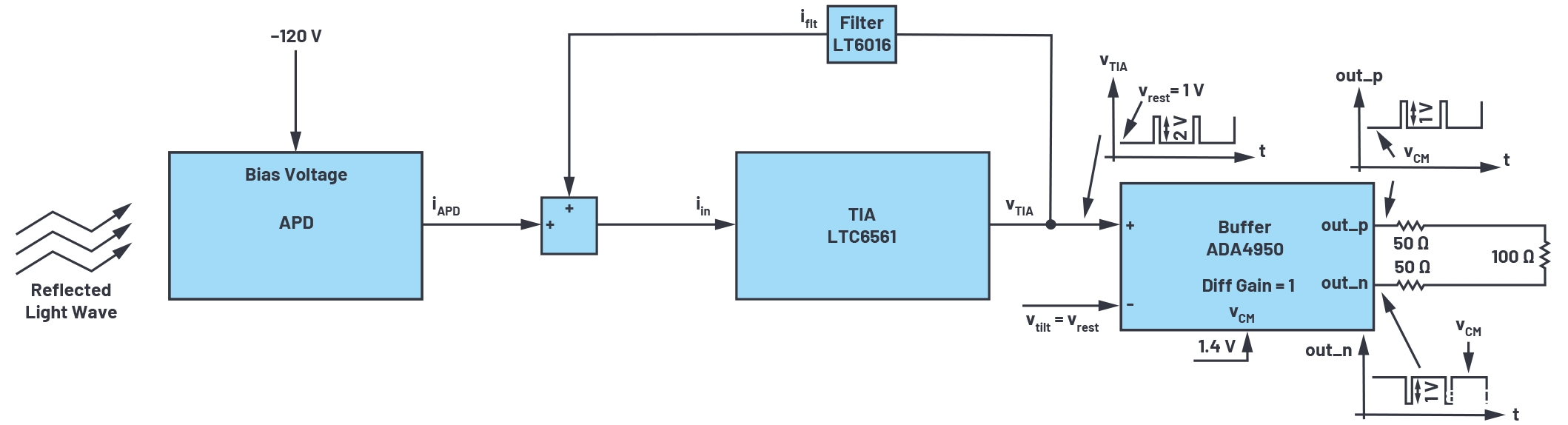

图1.LIDAR渠道体系规划。

简介

跟着主动驾驶轿车和机器人从幻想逐步变为实际,轿车和工业客户开端寻求新的环境感知处理计划,力求让这些机器能够主动导航。LIDAR是该范畴中开展最快的技能之一,跟着它越来越老练和牢靠,其运用规模也变得愈加广泛,带来了巨大的商场机会。许多草创企业和闻名传感器公司都致力于开发愈加精准、功耗低、尺度小,且愈加经济高效的LIDAR传感器,但在规划体系硬件、施行软件根底设施以和体系中的一切组件通讯时,他们都遇到了相同的应战。正是在这些区域,ADI能够通过软件参阅规划和开源软件仓库供给价值,令客户能够轻松将ADI LIDAR产品系列、软件模块和HDL IP集成到其产品和IC中,然后缩短上市时刻。

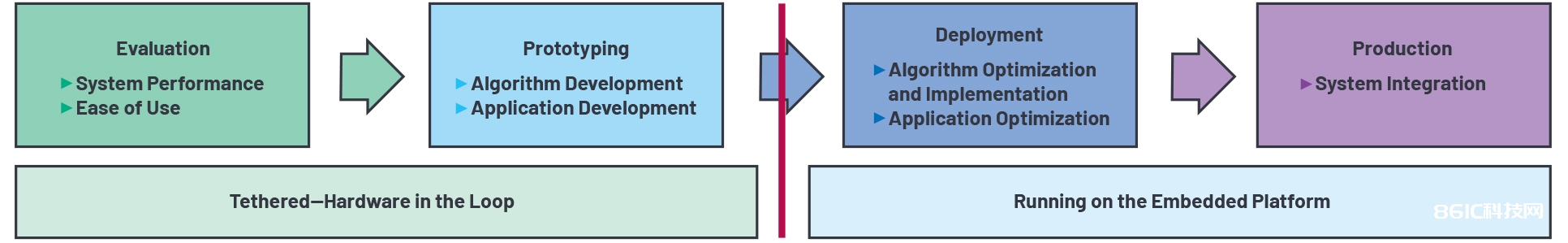

图2.产品开发周期。

体系架构

客户在开发自己的LIDAR传感器时,体系规划中会存一些不同之处:接纳和发送光学器材、激光器的数量和方向、激光发射形式、激光束操控,以及光接纳元件的数量。可是,不论做出什么挑选,在接纳信号链和激光器驱动信号要求方面,一切传感器都高度类似。依据这些假定,ADI公司规划出模块化LIDAR原型制造渠道AD-FMCLIDAR1-EBZ,以期让客户能够运用他们自己的硬件轻松装备或替换器材;该渠道依据特定的运用要求规划,但仍能够用作整个体系。该体系能够分为三个不同的电路板,每个都装备标准化的数字和模仿接口:

▶ 数据收集(DAQ)电路板,包括高速JESD204B ADC、对应的时钟和电源。此电路板上有一个契合FMC要求的接口,能够衔接至用户首选的FPGA开发板。它充任体系的基板,通过用于在这些板和FPGA之间路由操控和反应信号的数字衔接器,以及用于传输模仿信号的同轴电缆,将别的两个板衔接至这个板。

▶ 包括雪崩光电探测器(APD)的光传感器和整个信号链的模仿前端(AFE)电路板,信号链用于调谐APD输出信号,以便能馈入DAQ板上的ADC。

▶ 包括激光器和驱动电路的激光器板。

和以往相同,在体系规划中,模块化意味着灵活性,但它也有一些缺陷,比方复杂性添加、功能下降和本钱添加,在决议体系分区时有必要全面评价这些缺陷。在这种情况下,体系被分红三个板,原因如下:

▶ 不管运用哪种模仿前端,挑选哪种激光器处理计划,ADC和时钟很或许坚持不变。

▶ 模仿前端硬件规划和尺度依据所选的APD、全体的体系接纳灵敏度,以及挑选的光学器材而改变。

▶ 激光器板规划和尺度依据所选的照明处理计划和光学器材而改变。

▶ 关于接纳器和发射器的方位和方向,体系供给很大的灵活性,以便它们互相对应或和其他方针对应,因而运用柔性电缆来传输数字信号,运用同轴电缆来传输两个电路板之间的模仿信号。

包括硬件规划的软件仓库以分层办法为根底,以少量几个层级区分为适用于特定操作体系的驱动和接口、体系特定的API和运用层。这使得仓库的上层能够坚持不变,不管软件是在嵌入式方针上运转,仍是在通过网络或USB衔接与体系通讯的PC上运转。如图2所示,在不同的产品开发阶段,这一点十分有用,由于这意味着将体系衔接至PC以简化开发时,在原型制造期间开发的相同的运用软件可轻松布置到嵌入式体系中,乃至无需触碰低层接口。

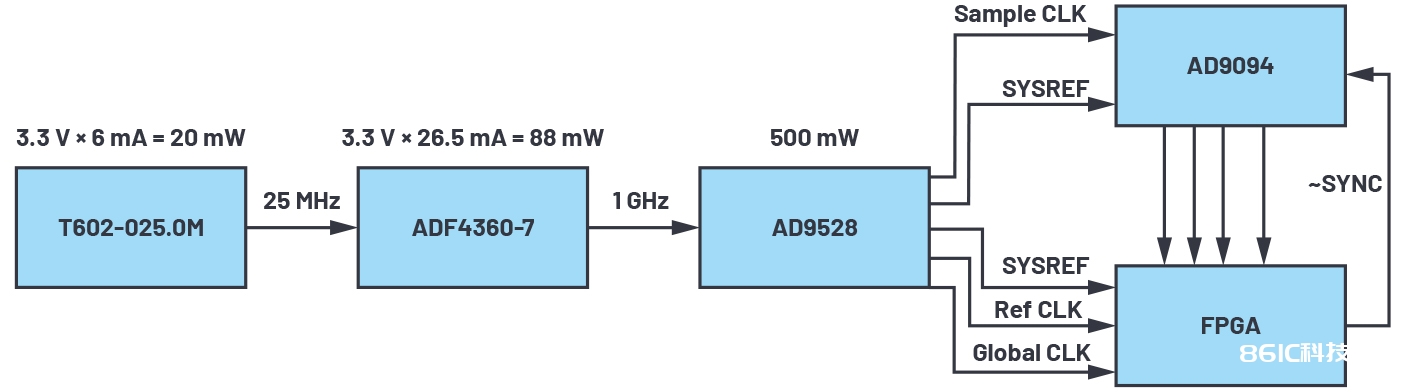

图3.DAQ板时钟和数据途径。

硬件规划

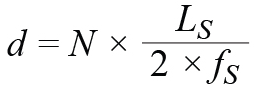

LIDAR传感器通过丈量光脉冲抵达方针并回来的时刻来核算与方针之间的间隔。丈量时刻时,以ADC 采样数据为增量, 这儿ADC采样速率决议了体系对接纳的光脉冲采样时的分辨率。公式1显现怎么依据ADC采样速率核算间隔。

|

|

其间:

LS 为光的速度,3 × 108 m/s

fS 为ADC采样速率

N为光脉冲生成至回来接纳期间ADC样本的数量

假定体系运用AD9094JESD204B四通道ADC的1 GHz采样速率,那么每个样本成果相当于15厘米间隔。因而,体系中不能存在采样不确定性,由于任何样本不确定性都或许导致巨大的间隔丈量误差。传统上,LIDAR体系以并行ADC为根底,这种ADC自身供给零采样不确定性。跟着接纳通道的数量不断添加,功率和PCB尺度的要求越来越严厉,这些ADC类型不能很好地扩展。另一选项是运用具有高速串行输出的ADC,例如JESD204B,以处理并行ADC存在的问题。这种选项的数据接口复杂度更高,因而难以完成零采样不确定性。

LIDAR DAQ板供给了处理这些应战的计划,通过展现为在Subclass 1形式下运转的JESD204B数据收集体系的电源、时钟和数据接口规划来确保确定性推迟,以完成零采样不确定性,一起运用JESD204B接口供给的一切优势,令时钟计划的功耗到达最低。要在Subclass 1形式下运转JESD204B,体系一共要用到5个时钟:

▶ ADC采样时钟: 驱动ADC信号采样进程。

▶ ADC和FPGA SYSREF: 源同步、高压摆率时序分辨率信号,用于重置器材时钟分频器,以确保取得确定性的推迟。

▶ FPGA大局时钟(也称为内核时钟或器材时钟):驱动JESD204B PHY层和FPGA逻辑的输出。

▶ FPGA参阅时钟:生成JESD204B收发器所需的PHY层内部时钟;需求等于,或是器材时钟的整数倍。

一切时钟都由一个AD9528 JESD204B时钟生成器生成,因而能够确保它们互相都同步。 图3显现了时钟计划,以及与FPGA的数据接口。

AFE板接纳光学反射信号,将其转化成电子信号,然后传输给DAQ板上的ADC。这个板或许是整个规划中灵敏度最高的部分,由于它混合信号调理电路(运用16通道APD阵列生成的微安电流信号),将光学信号转化成电子信号,并选用为相同的APD供电所需的–120 V至–300 V大电压电源。16个电流输出被馈送至4个低噪声四通道互阻增益放大器(TIA)LTC6561,带有一个内部4合1复用器,用于挑选之后向其间一个ADC输入端馈送的输出通道。要特别注意TIA的输入部分,以完成所需的信号完好度和通道阻隔等级,使得APD生成的极低电流信号中不会掺杂更多噪声,然后最大化体系的SNR和目标检测率。AFE板的规划显现,要完成最高信号质量,最好的办法是让APD和TIA之间的线路长度尽或许短,并在TIA输入之间添加椭圆孔,以最大化通道间阻隔;此外,在布置信号调理电路时,要确保该电路不会搅扰板上的其他电源电路。另一项重要特性是能够丈量APD的温度,以补偿APD信号输出的改变,这种改变是由于在正常运转期间APD温度上升导致的。供给几个旋钮来操控信号链的偏置和APD偏置,这些偏置转化成APD灵敏度,然后最大化ADC输入规模,以完成最大SNR。图4显现了AFE板信号链的框图。

激光器板生成波长为905 nm的光学脉冲。它运用四个激光器,这些激光器一起驱动,以添加光束强度,完成更长的丈量间隔。此激光器运用由FPGA载波板生成的具有可编程脉宽和频率的PWM信号来操控。这些信号在FPGA上生成,以LVDS从FPGA传输至激光器板,通过DAQ板以及衔接DAQ和激光器板的扁平电缆期间,不易遭到噪声影响。驱动信号能够回来至其间一个ADC通道,以取得飞翔时刻参阅。选用外部电源为激光器供电。其规划契合国际标准IEC 60825-1:2014和IEC 60825-1:2007中关于Class 1级激光器产品的要求。

AFE和激光器板都需求光学器材,以完成长间隔丈量。事实证明,该体系可在60米规模内丈量,运用快速轴准直器1,协助激光二极管将笔直FoV缩小到1°,一起在坚持水平视场不变的情况下,在接纳侧放置一个非球面透镜。

图4.AFE板信号链。