陈玉翔(电子科技大学电子科学与工程学院 四川 成都 610054)

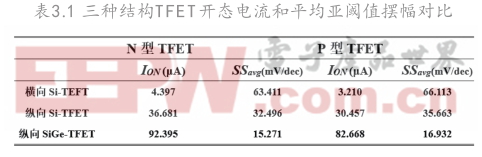

摘 要:地道场效应晶体管(TFET)因为其共同的带带隧穿原理而成为超低功耗规划中有力的候选者。传统MOSFET在室温下的亚阈值摆幅因载流子漂移分散作业原理而高于60 mV/dec;而根据量子地道效应的隧穿场效应晶体管,其亚阈值斜率能够打破MOSFET器材的亚阈值摆幅理论极限,而且具有极低的关态走漏电流。本文提出了一种异质结纵向隧穿场效应晶体管,用以改善器材导通电流和亚阈值特性,改善后的器材开态电流由36 μA/μm添加到92 μA/μm,均匀亚阈值摆幅从32 mV/dec下降到15 mV/dec。

关键词:隧穿场效应晶体管;带带隧穿;异质结;开态电流

0 导言

跟着MOSFET器材尺度不断缩小,下降功耗成为了集成电路规划的关键问题。热载流子注入效应在室温下将金属氧化物半导体场效应晶体管(MOSFET)的亚阈值摆幅(SS)约束在60 mV/dec,这种物理上的约束使得MOSFET难以适用于低电源电压 [1-2] 。隧穿场效应晶体管(TFET)具有低亚阈值摆幅和低关态电流的长处,可是遭到隧穿面积和隧穿几率的约束,TFET器材的电流密度一般比MOSFET低2~3个数量级左右,约束了TFET器材的实践运用 [3] 。

在器材中运用高K介质进步电场强度 [4-5] 或许窄禁带资料减小禁带宽度已经成为进步TFET功能常见的办法。有研讨人员在传统纵向TFET源区运用了窄带隙资料以添加隧穿电流 [6] ,虽然能添加导通电流并坚持低的关态电流,但该器材在异质结界面处呈现的缺点是一个严峻的问题。因为隧穿势垒一般坐落本征区中,因而能够测验替换本征区资料而不是源区资料。文献 [7] 运用窄带隙资料替换了整个沟道区域,可是运用此办法有必要考虑TFET双极导通效应,该效应会导致高关态走漏电流。别的有科研人员提出经过运用先进的设备操控器材掺杂散布,例如源区重掺杂薄层结构 [8-9] ,减小势垒区宽度增大电场强度,可是单边骤变结在实践工艺中很难完成,或许会导致实质性的制作差异。

本文提出了一种窄禁带纵向隧穿场效应晶体管(SiGe-TFET),经过在纵向TFET外延隧穿区运用SiGe资料,缩短载流子隧穿间隔,增大隧穿几率,器材具有高开态电流、低亚阈值摆幅和低关态走漏电流的特色;文章第2节首要描绘器材结构及作业原理;第3节给出仿真成果;第4节得出终究定论。

1 器材结构和作业原理

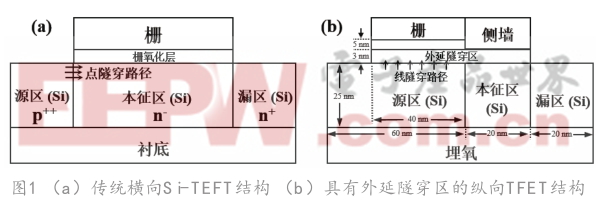

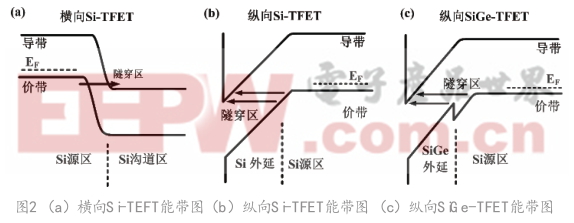

隧穿场效应晶体管的实质是一个栅压操控的P-I-N结。与MOSFET器材相似的是,TFET器材也是由栅极、源极及漏极等电极构成,不同的是MOSFET器材的沟道是指栅极下方的反型层,而TFET器材的沟道是指栅极下方的隧穿区域。依照隧穿方向与栅电场的联系,能够分为两种隧穿场效应晶体管,如图2.1所示:当隧穿方向与栅电场方向笔直时,该隧穿场效应晶体管为横向TFET器材;当隧穿方向平行于栅电场方向时,该隧穿场效应晶体管为纵向TFET器材。

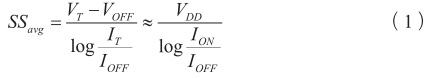

跟着超薄外延成长技能的开展,选用半导体异质结资料制作晶体管成为或许。与全Si-TFET比较,在器材中运用SiGe、InAs等窄禁带资料,能够有用地减小隧穿区的禁带宽度,进步载流子的隧穿电流。本 次研讨选用根据异质外延区的纵向TFET结构,如图2.1(b)所示,包含半导体衬底、源区、本征区、漏区、外延区、高K栅氧化层及金属栅。外延区选用SiGe以进步隧穿几率,坐落源区与本征区上方。为增强导通电流源区选用1×10 20 cm -3 的重掺杂,漏极为1×10 18 cm -3 的中等浓度掺杂用来按捺TFET双极导通效应;本征区为宽度20nm,浓度1×10 15 cm-3的轻掺杂区;栅氧化层选用5 nm厚度的HfO 2 。界说电流分别为 10 -7 A /μm和10 -13 A/μm时所对应的电压为阈值电压V T 和敞开电压V OFF ,开态电流I ON 界说为栅电压等于(V OFF +1)V时所对应的电流值,阈值电压 V T 和敞开电压 V OFF 两点之间的斜率作为均匀亚阈值摆幅(SS avg ):

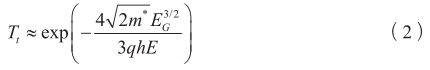

TFET器材的导通电流首要取决于隧穿几率,运用三角局势垒近似来核算隧穿,隧穿概率能够表明成:

式中, m * 为电子的有用质量, E G 为隧穿区资料的禁带宽度, q 为电子电荷, h 为普朗克常数除以2π的值,E为电场强度。经过对导带和价带态密度进行积分能够得到外加偏压V时的隧穿电流:

从上述成果能够清楚的看出,为了进步隧穿电流,器材隧穿区的电场强度应很大,而禁带宽度应尽或许地小,即隧穿间隔越小,则隧穿电流越大。传统横向Si-TFET,纵向Si-TFET和纵向SiGe-TFET带带隧穿能带图如图2所示。关于横向隧穿TFET结构,栅极只能操控使源区与本征区界面外表区域产生隧穿,隧穿区域面积很小导致无法取得较大的开态电流。而纵向隧穿TFET的载流子隧穿区域面积正比于栅极掩盖源区/外延区的面积,隧穿面积比较横向隧穿大得多,器材驱动电流较高。

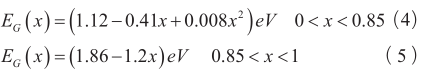

SiGe-TFET则是在纵向TFET的外延隧穿区选用了高Ge组分的SiGe资料,SiGe资料的禁带宽度和Ge组分有直接联系,疏忽资料之间的应力,禁带宽度与Si 1-x Ge x 资料Ge组分之间的联系能够表明为:

Ge组分越高,资料禁带宽度越小。从图2.2(c)也能够看出,将SiGe资料运用于外延隧穿区能够有用地下降该区的带隙并促进载流子的隧穿。TFET关态走漏电流途径首要存在于横向P-I-N结,当运用具有高Ge含量的SiGe资料时,反向走漏电流也会添加。在SiGe-TFET的规划中,外延隧穿区的厚度只要5 nm左右,SiGe资料的面积很小,因而这种规划能够削减关断电流的添加,能够一起满意高导通电流和低关态走漏电流的要求。

2 仿真成果

器材仿真运用了Synopsys公司的Sentaurus TCAD东西,选用了动态非部分带带隧穿模型,该模型用Wentzel-Kramer-Brillouin(WKB)近似来捕获穿越一切或许结和外表的隧穿。SRH(Shockley-Read-Hall)复合模型,迁移率模型,Fermi-Dirac计算散布模型和禁带宽度变窄模型被用来仿真器材电学特性。

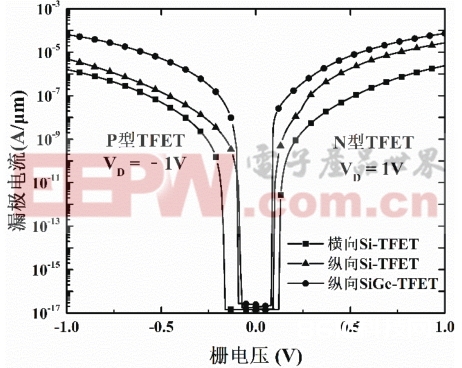

P型TFET与N型TFET相反,带带隧穿开始于重掺杂的N+源区,空穴从源区导带隧穿进入沟道区中的价带,器材在大的负栅极电压下导通。选用SiGe作为外延区资料的N型TFET与P型TFET,外延隧穿区的Ge含量相同,禁带宽度相同,因而在相同栅压下隧穿间隔相同,N型TFET与P型TFET隧穿概率附近,由此得到互补的搬运特性曲线。

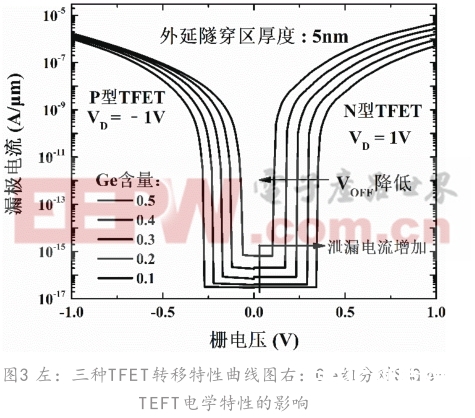

图3左图展现了参数优化往后的N型与P型横向Si-TFET,纵向Si-TFET和纵向SiGe-TFET在 V D = ± 1 V下的搬运特性的比较。能够看出,无论是N型仍是P型TFET,纵向SiGe-TFET的隧穿电流显着大于别的两种结构的隧穿电流。右图显现了SiGe-TEFT在外延区Ge组分不同的情况下,N型TFET与P型TFET搬运特性。经过在外延区中运用SiGe资料,器材敞开电压V OFF 将随Ge组分的添加而减小,导通电流与反向走漏电流都将跟着Ge含量的添加而添加。

3 定论

本文提出了一种新式的异质结隧穿场效应晶体管。经过在外延隧穿区运用SiGe资料,纵向SiGe -TFET能够在确保低关态电流的一起,有用进步N型TFET和P型TFET的驱动电流,并下降亚阈值摆幅。成果表明,导通电流由36 μA/μm添加到92 μA/μm,均匀亚阈值摆幅从32mV/dec下降到15mV/dec。一起,根据此结构的N型TFET和P型TFET能够选用同一种器材结构,仅需求改动相应区域的掺杂类型,就能够构成相似CMOS的互补隧穿场效应晶体管,这意味着其在未来超低压运用中具有巨大的潜力。

参考文献:

[1] Q. Zhang, W. Zhao, and A. Seabaugh,“Lowsubthreshold-swing tunnel transistors,” IEEE ElectronDevice Lett., vol. 27, no. 4, pp. 297–300, Apr. 2006.

[2] W. Y. Choi, B.-G. Park, J. D. Lee, and T.-J. K.Liu, “Tunneling field-effect transistors (TFETs) withsubthreshold swing (SS) less than 60 mV/dec,” IEEEElectron Device Lett., vol. 28, no. 8, pp. 743–745, Aug.2007.

[3] A. C. Seabaugh and Q. Zhang, “Low-Voltage TunnelTransistors for Beyond CMOS Logic,” Proceedings of theIEEE, vol. 98, no. 12, pp. 2095-2110, Dec. 2010.

[4] W. Y. Choi and W. Lee, “Hetero-Gate-DielectricTunneling Field-Effect Transistors,” IEEE Transactionson Electron Devices, vol. 57, no. 9, pp. 2317-2319, Sept.2010.

[5] K. Boucart and A. M. Ionescu, “Double-Gate TunnelFET with High-k Gate Dielectric,” IEEE Transactions onElectron Devices, vol. 54, no. 7, pp. 1725-1733, July 2007.

[6] S. H. Kim, Z. A. Jacobson and T. K. Liu, “Impactof Body Doping and Thickness on the Performance ofGermanium-Source TFETs,” in IEEE Transactions onElectron Devices, vol. 57, no. 7, pp. 1710-1713, July 2010.

[7] S. Mookerjea and S. Datta, “Comparative Study of Si,Ge and InAs based Steep SubThresholdSlope Tunnel Transistors for 0.25V SupplyVoltage Logic Applications,” 2008 Device ResearchConference, Santa Barbara, CA, 2008, pp. 47-48.

[8] R. Jhaveri, V. Nagavarapu and J. C. S. Woo, “Effect ofPocket Doping and Annealing Schemes on the Source-Pocket Tunnel Field-Effect Transistor,” in IEEETransactions on Electron Devices, vol. 58, no. 1, pp. 80-86,Jan. 2011.

[9] D. B. Abdi and M. J. Kumar, “In-Built N+ Pocket p-n-p-n Tunnel Field-Effect Transistor,” inIEEE Electron Device Letters, vol. 35, no.12, pp. 1170-1172, Dec. 2014.

(注:本文来源于科技期刊《电子产品世界》2020年第06期第50页,欢迎您写论文时引证,并注明出处。)