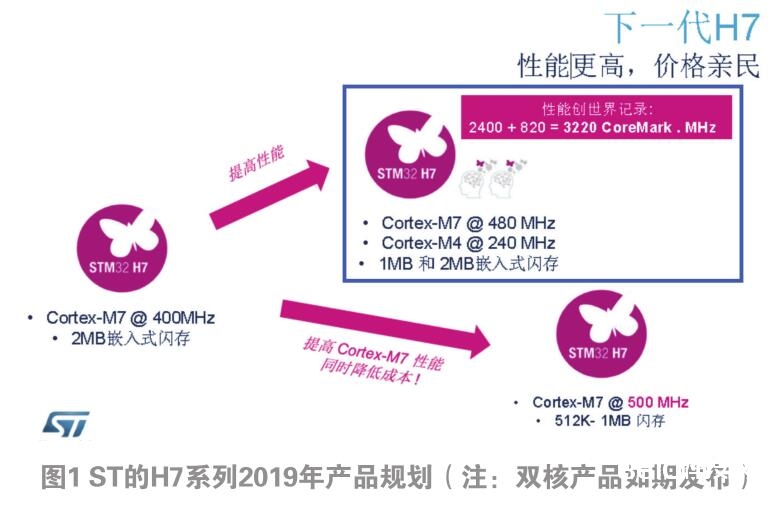

不久前,意法半导体(ST)发布了高功用的微操控器(MCU) STM32H7。其杰出特征之一是选用Arm Cortex-M系列中功用最高的480MHz Cortex-M7内核,并添加一颗240MHz Cortex-M4内核(如图1),完成了3224 CoreMark,可谓业界功用最高的Arm Cortex-M通用MCU。

1 经过双核完成超高功用的规划考量

众所周知,MCU的另一巨子厂商N公司两年前就推出了根据M7单核的MCU,名为“跨界处理器”,特征是无内置闪存,主频可达1 GHz、600 MHz等,CoreMark3000左右,完成了MCU的架构、MPU的运用。那么,ST为何不把H7的单核主频进步,而是选用了较为杂乱的双核战略?别的,双核是否意味着客户的软件编程难度进步了?

ST微操控器事业部STM32高功用产品线高档商场司理RenaudBOUZEREAU指出,在内核跑分上,需要从两方面看。

榜首,主频的进步会是影响Coremark跑分的一个十分重要的要素。

可是,整个工程的履行功率并不能只是看主频,还要看芯片内部的总线架构、拜访Flash的位数,以及其他外设资源和硬件加速器等。而内置Flash履行代码的功率比照与外置QSPI Flash这种形式会高许多,也避免了许多总线抵触和内存装备的问题。从嵌入式规划视点而言,外面添加元器件也会影响体系的稳定性。

第二,在规划产品的时分,ST一直在考虑功用和稳定性的平衡。

越高的主频,意味着产品会相对软弱。ST研讨过许多竞争对手的芯片,发现在高温测验的时分,往往要下降主频才干确保体系的稳定性。所以ST在评论和研讨后,以为480 MHz的主频会是一个很好的平衡点。

为了处理双核编程的应战,ST从两方面下手。榜首,从硬件视点,在STM32H7双核产品里,内置了硬件信号量的机制,硬件信号量能够将两个核的运转状况进行同步,例如有些外设经过M4处理的时分,经过硬件信号量告诉M7内核该外设暂时不能被拜访的。

其次,从软件视点,ST自有的CubeMX及IDE(集成规划环境)都现已支撑双核的开发。在双核开发时,两个工程都会摆在同一个界面上做调试,这样关于开发者会比较简单,包含第三方操作体系,例如FreeRTOS,现在支撑双核的规划,两个核之间的通讯会经过内部Mailbox的机制进行通讯,将两个核的信息进行同步。

除此之外,双核还有共同的“1+1>2”的优势。①经过灵敏运用两个内核,开发人员能够轻松升级现有运用,添加更先进杂乱的图形用户界面。以电机操控为例,将曾经在单核Cortex-M4MCU上的旧代码迁移到STM32H7Cortex-M4上,一起在Cortex-M7上运转新GUI(图形用户界面)。

另一个比如是经过下降主处理器的密集型作业负荷,例如,神经网络、校验和、DSP过滤或音频编解码,进步运用功用。②双核架构还有助于简化代码开发,并缩短项目开发周期,将用户界面代码与实时操控或通讯功用的开发分隔进行。

2 内置闪存、SRAM的考虑

友商N公司的高功用MCU/跨界处理器的首要特征之一是无闪存。

但ST的方法依然是供给丰厚的闪存/内存。ST我国区微操控器事业部商场及运用总监曹锦东解释道,据ST查询,现在商场上超越80%~90%的客户期望的架构是MCU内置flash(闪存)和RAM的,并具有更多先进的外设,首要,这样的架构能够缩小用户的PCB(印制板)面积和规划本钱;其次,内置闪存十分安全,可防止外部盗取或篡改数据。因而,此次新的H7 MCU在片上额定供给高达2MB闪存和1MBSRAM。