NOR闪存已作为FPGA(现场可编程门列阵)的装备器材被广泛布置。其为FPGA带来的低推迟和高数据吞吐量特性使得FPGA在工业、通讯和轿车ADAS(高档驾驭辅佐体系)等运用中得到广泛选用。轿车场景中摄像头体系的快速发动时刻要求便是很好的一个比如——车辆发动后后视图像在仪表板显现屏上的显现速度是最为杰出的规划应战。

上电后,FPGA当即加载存储于NOR器材中的装备比特流。传输完结后,FPGA转换为活动(已装备)状况。FPGA包含许多装备接口选项,一般包含并行NOR总线和串行外设接口(SPI)总线。支撑这些总线的存储器在不同厂商的产品之间总是存在细小的不兼容性,增添了收购多款存储器材的困难程度。

全新发布的JEDEC

xSPI标准由各大首要NOR闪存厂商联合拟定。新标准完毕了数十年来NOR闪存厂商独立开发产品、各自为营的局势。尽管存在细微差别,但现在各厂商产品的中心JEDEC

xSPI功用已完全相同。JEDEC

xSPI标准对总线业务、指令和很多内部功用进行了标准化。结合高吞吐量这一功用,这些下一代闪存可完结全新的运用和功用。例如,赛普拉斯Semper NOR

Flash系列契合JEDEC xSPI标准,并供给持续400MB

/s读取传输速率,非常合适作为FPGA装备存储器。详细而言,凭仗400MB/s的数据速率,容量为128MB(1Gb)的器材,其内容可在320ms内完结传输。

FPGA装备前史回忆

当FPGA初次问世时,可挑选的装备存储器是并行EPROM或并行EEPROM产品。跟着时刻的推移,NOR闪存技能应运而生,一起因其体系内可重复编程性和高性价比而被广泛选用。在第2次革命性转折中,SPI存储器接口在大多数运用中替代了并行NOR接口。今日的SPI存储器产品具有高密度、小封装尺度和高读取吞吐量,以及最重要的特色——更高效的低引脚数接口。

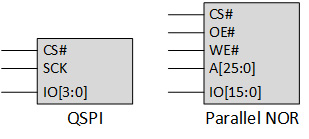

图1 – 千兆位四路SPI(6引脚)和并行NOR(45引脚)接口

图1显现了千兆位SPI器材与千兆位并行NOR的引脚分配的比照。关于一个千兆位存储器,四路串行外设接口(QSPI)器材具有六引脚接口,而并行NOR器材则需求45个引脚。引脚数量的巨大差异导致QSPI器材作为首选装备接口而被广泛选用。QSPI接口答应在不改动器材占用空间的情况下更改密度。

FPGA装备速度

跟着工艺节点缩小,FPGA器材得以持续添加可用的可编程逻辑模块数量,然后导致对更高密度和更快速度装备存储器的需求。现代FPGA在装备期间需求加载多达128MB的数据。这些高密度装备比特流需求更长的时刻才能从NOR闪存器材传输到FPGA。装备接口不只针对读取吞吐量进行了优化,还专心于促进不同NOR闪存制造商之间的互操作性。

SPI读取吞吐量

曩昔几年,从开端以x1形式运转的SPI接口开端,一直到以x4

DDR形式运转的现代QSPI产品,SPI读取吞吐量发生了明显增加。从表1能够看出,下一代闪存器材能够推进SPI总线功用完结又一次跃迁。

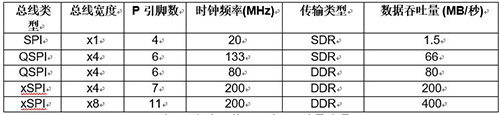

表1 – 闪存器材SPI读取吞吐量选项

现代SPI器材能够永久装备为固定的总线宽度和传输类型,可在上电时当即运转。FPGA须支撑这一永久装备,以便在上电后当即发动装备进程。

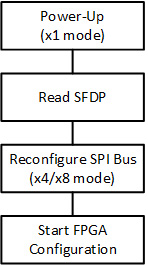

又或许,SPI存储器可在x1形式下退出通电状况,然后答应主机体系(FPGA)查询存储器中的串行闪存可发现参数(SFDP)表中的特性。这一x1形式已成为多家存储器厂商支撑的标准功用,并答应FPGA检索有关器材功用的要害信息。一旦检索到器材特性,就能够快速重新装备FPGA存储器控制器和SPI存储器器材,以取得最大的读取功用。

图2 – 通电时运用串行闪存可发现参数(SFDP)表装备SPI总线功用

在选用可运用x1、x4或x8总线宽度以及SDR或DDR传输类型运转的下一代闪存设备时,运用集成SFDP表检索要害设备信息将分外重要。所挑选的总线宽度和传输类型有必要与FPGA上完结的总线接口基础设施保持一致。

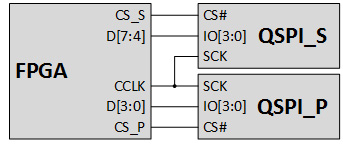

双QSPI装备接口

为削减FPGA装备时刻,许多现代FPGA答应将装备位流分区至两个QSPI器材(图3)。这两个QSPI器材以并行方法衔接,其间位流的低半字节存储在“主”QSPI器材(QSPI_P)中,位流的高半字节存储在“辅佐”QSPI器材(QSPI_S)中。这两个器材在加载位流时并行运转,然后有用地使读取数据传输速率提高一倍。

请注意,除同享SCK(串行时钟)线以外,接口在两个器材上基本上是独立的。之所以要同享SCK线,是为了在以并行方法(即一起)读取器材时完结时序误差最小化。当运用相同方针地址履行相同操作时,能够一次仅对一个器材进行拜访,也能够一起对两个器材进行拜访。

图3 – 双QSPI装备接口(11个引脚)答应装备位流在两个QSPI器材之间进行分区,然后有用地将读取数据传输速率提高一倍。

当大型FPGA器材需求以最快的方法传输大装备(即高密度)装备比特流时,这种11引脚双QSPI装备将具有非常大的优势。

闪存装备

下一代闪存选用x1(首要用于SFDP拜访)、x4或x8 IO总线宽度运转,支撑SDR或DDR格局传输数据,而且经过运用新的数据选通(Data

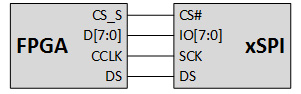

Strobe)信号以促进高速传输。例如,运用11引脚接口的赛普拉斯Semper NOR闪存八进制装备(图4)。

图4 – 低引脚数接口支撑SDR或DDR格局的x1、x4或x8 IO总线宽度传输数据。图中显现的是选用11引脚接口的赛普拉斯Semper

NOR闪存八进制装备。

这一新的数据通选有必要结合到FPGA装备接口中,然后可使用下一代闪存器材的高吞吐量读取功用。数据选通与输出读取数据边际对齐,其方法与低功耗DDR

DRAM器材上的选通方法相同(图5)。数据选通“制作”数据眼图,并答应FPGA以高时钟频率有用抓取数据。

图5 – 具有数据选通功用的x8 DDR读取业务与输出读取数据边际对齐,使FPGA能够以高时钟频率有用抓取数据。

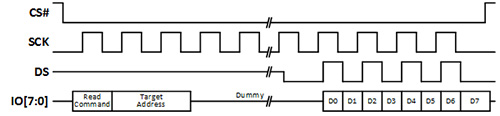

支撑接连读取操作是非常适用于FPGA装备的闪存功用之一。接连读取始于主机(MCU(微控制器)或FPGA)置位CS#(CS片选引脚),然后宣布读取指令,后跟方针地址。经过屡次推迟周期,存储器从方针地址输出数据。假如主机持续切换时钟,则存储器将经过从下一个次序地址输出数据来呼应。只需时钟持续切换,存储器将持续从次序地址输出数据。这种次序读取功用能够答应FPGA装备单个读取业务。

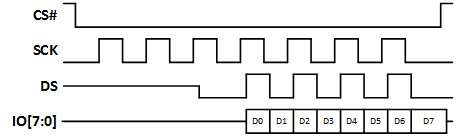

AutoBoot(主动发动)是另一项有助于FPGA装备的功用。AutoBoot在通电复位期间从预先装备的方针地址履行主动读取,然后在第一次CS#置位时当即输出数据(图6)。此功用对需求简略装备机制的ASIC(专用芯片)器材也非常有用。一旦CS#免除置位,内存将回来其待命状况,并以正常方法处理后续操作。

图6 – 运转中的AutoBoot读取功用(具有3个预热周期)

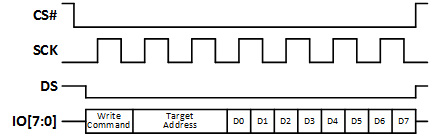

NOR

闪存器材的写入业务(图7)与标准SPI操作简直完全相同,但有两点破例。首要,在整个业务期间有必要将新的数据选通讯号驱动为LOW(低电平)。其次,当装备为DDR操作时,数据被写为字(16b),而非传统SPI产品的字节写编程粒度。

图7- NOR 闪存的写入业务需求在整个业务期间将数据选通讯号驱动为LOW,而且在装备为DDR操作时将数据写为16位字。

下一代NOR闪存器材可供给满意大规模FPGA运用的高密度和随开即用要求所需的高吞吐量。各大NOR闪存制造厂商都参加了JEDEC

xSPI标准的开发,为代工厂商供给了广泛的收购挑选。JEDEC

xSPI标准涵盖了上述八进制SPI接口以及HyperBus接口,两者均供给400MB/s的读取吞吐量,已完结的读取吞吐量远高于传统SPI产品。为使用高速基础设施,需求对FPGA

SPI控制器进行修正。需求考虑的新功用包含DDR数据速率,用于数据抓取的新数据选通引脚和扩展的x8总线接口。此外,一些NOR闪存器材(例如赛普拉斯Semper

NOR系列)答应在施行双QSPI装备架构时消除其间一个QSPI器材。在需求进行快速FPGA装备的情况下,以及在履行实时重新装备的FPGA运用中,下一代闪存所供给的功用将具有强壮的优势。

关于作者:Cliff

Zitlaw具有长达36年的半导体存储器开发经历,要点重视能够完结在各类运用程序束缚范围内优化内存功用总线接口。Cliff是Xicor微处理器串行存储器接口(EEPROM),美光科技(Micron)CellularRAM接口(PSRAM)和赛普拉斯Hyperbus接口(NOR和PSRAM)的发明者。

Cliff是49项与内存功用和用法相关的专利著作者或合著者。空闲之余,Cliff喜爱烧烤,看电视,或在周六小睡顷刻。