作者 韩晓冰 高梦1,2 汪金萍1,2 1.西安科技大学 通讯与信息工程学院(陕西 西安

710054) 2.西安斗极安全技能有限公司(陕西 西安 710100)

韩晓冰(1968—),男,陕西西安人,教授,从事无线通讯与无线检测的研讨;高梦(1993-)女,陕西西安,学生,硕士,电子与通讯工程;汪金萍(1991-)女,甘肃白银,学生,硕士,通讯与信息体系。

摘要:本文运用MAX2769芯片规划射频前端,将卫星射频信号下变频到数字中频;以FPGA+USB3.0的高速数据收集渠道为中心,选用FPGA芯片作为主处理器,操控射频与USB接口芯片,完结数据传输和存储,完结多种卫星中频数据收集体系的规划。运用已收集好的卫星信号中频数据,在MATLAB渠道进行编程仿真,研讨了依据FFT的信号捕获算法,能够一起处理GPS和斗极两种体系的中频数据并完结信号捕获。经过编写FPGA传输数据的Verilog程序、USB设备的固件程序、上位机程序,给出了体系硬件结构以及软件算法流程,完结中频数据的接纳、传输和保存,仿真验证了信号捕获进程,给出捕获成果。试验成果标明,该GPS\BD双模中频数据收集体系能够满意后续定位处理要求,能够被运用于全部依据方位服务(LBS)的运用场景中。

0 导言

跟着全球卫星导航体系GNSS的建成和完善,在不久的将来用户将收到越来越多的卫星导航信号,多模接纳机是一个必定的趋势[1],GPS是美国研发的全球定位导航体系,开展最为老练并在全球规模内得到广泛运用,跟着对GPS软件接纳机进行深化的研讨,为我国自主立异的COMPASS斗极导航体系研讨也堆集丰厚的经历和技能。

软件接纳机的规划首要包含射频前端,中频信号处理和导航定位信号解算三大部分。射频前端是一切后续信号处理的根底,担任信号下变频和A\D转化,输出的数字信号用于后续中频信号处理[2];中频信号处理包含中频信号的收集,捕获和盯梢等,中频信号收集体系能够完好地保存GPS\BD两种卫星的中频信号数据,为下面的基带信号处理算法供给根底。导航解算部分首要担任信号的盯梢和确认的软件部分、数据的解调、伪距的提取以及导航数据的解算,它的处理根底是中频信号处理,原始数据来自于收集体系。

本文首要研讨规划出双模单通道的GPS\BD中频数据收集体系,依据USB3.0与FPGA相结合的技能,完结对卫星信号的收集和传输,接着对中频频域并行码捕获算法进行了研讨,确立了依据快速傅里叶改换FFT(Fast

Fourier Transform)并行捕获算法的计划,经过MATLAB仿真验证了该计划的可行性。

1 体系硬件规划

卫星中频数据是进行软件接纳机研讨的条件。为了完结规划要求,不只需考虑器材的实时性和高效性,还要顾及体系的可扩展性[3]。射频前端模块将卫星信号中频化,选用现在高速数字信号处理广泛运用的现场可编程门阵列FPGA(Field

Programmable Gate

Array)作为体系操控中心,对数字中频信号进行处理,完结数据格式转化、数据缓存和USB状况操控,对USB进行端点装备、编写固件程序和PC软件规划,再经过USB接口完结数据的快速传输和PC存储,建立硬件渠道,完结对GPS

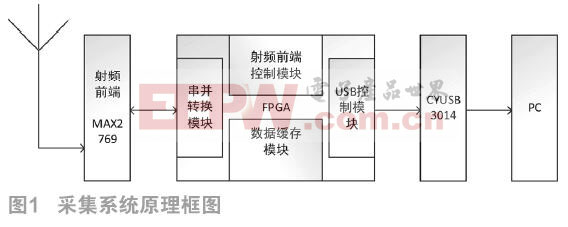

L1和BD B1信号的数据收集。体系原理框图如图1所示。

其间,天线担任GPS\BD卫星信号的接纳,射频前端将接纳到的卫星信号扩大,滤波,下变频和模数转化为中频信号后输出;FPGA芯片完结射频前端MAX2769的操控与中频信号的接纳和处理,转化数据格式送入USB芯片端点FIFO缓冲,构成主从FIFO结构与CYUSB3014之间完结高速数据传输[4],再经过USB3.0接口传输数据并在PC端完结收集和存储。

本文规划建立的GPS\BD中频信号收集体系,硬件部分首要包含:射频前端和中频信号收集单元,其间中频信号收集单元包含FPGA操控和USB高速数据传输电路的规划[5]。

1.1 射频前端

射频前端的首要功用是将天线接纳到的射频信号进行下变频,对这些弱小信号进行扩大,将输出的信号转化为数字办法,并能够在可编程数字信号处理器中处理,例如DSP、FPGA

和PC等。

本文射频前端规划计划选用MAX2769芯片完结,因为其内部集成了完好的接纳机链路,只需合作少数的外围元器材就能够完结GPS、斗极、伽利略等多种卫星信号的接纳和处理[6],构建一个完好的低成本接纳机计划。芯片内部集成了双通道低噪声扩大器(LNA)、温补晶体振荡器(TCXO)

、混频器(MIXER)、基带可编程增益扩大器(PGA)、按捺镜像滤波器(IRF)、Σ-Δ小数N分频频率合成器 (VCO),总噪声系数低达1.4dB。集成的ADC

既能够为I、Q通道各输出1或2bit数字中频信号,也能够I支路输出三个量化位[7]。

1.2 信号收集单元

FPGA选用Altera公司出产的Cyclone

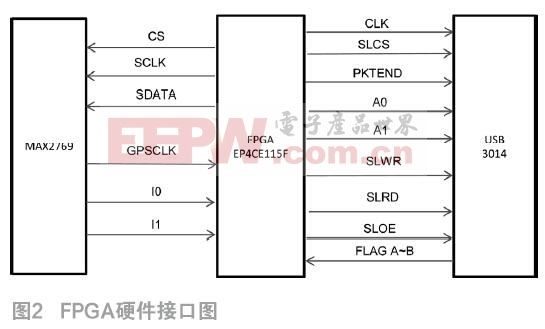

IV系列EP4CE115F芯片,该芯片数据传输速率高达3.125Gbps,片内集成114480个逻辑单元(LE),234K位RAM,多达360个嵌入式18×18乘法器,用户I\O口多达532个,资源适当丰厚。收集体系中硬件衔接规划如图2所示[8]。

图2所示编程操控MAX2769芯片作业在SPI形式下,经过3线接口SDATA(串行数据),SCLK(串行时钟)和CS(片选)完结其内部10个寄存器的装备,射频前端对高频信号(L1\B1)进行处理并降至中频(IF),经过单通道体系收集取得实时2bit数字中频数据(符号SIGN和MAG)后,送至基带信号处理器(Digital

Baseband Processor)。

USB芯片选用Cypress公司EZ-USB

FX3系列中CYUSB3014来完结[8]。该芯片集成了USB3.0和USB2.0物理层(PHY)以及32位ARM926EJ-S微处理器,具有强壮的数据处理才能,并可用于构建定制运用,一起还配有512

kb的内置SRAM以及更多的接口,具有强壮的数据处理才能。体系运用通用可编程接口GPIF II的Slave

FIFO办法完结数据的上传需求,由外部操控器操控USB芯片在隶属FIFO形式下作业。

图2中FX3芯片与FPGA衔接部分[9],FPGA对接纳到的数据进行处理,操控USB芯片作业状况,将数据传送到USB端口FIFO。CLK为16.369

MHz接口时钟,由芯片内部发生;FLAGA和FLAGB为CYUSB3014回来给FPGA的状况信号,FIFO

标志位管脚,反映USB端口FIFO当时的状况,FPGA依据回来的状况信号决议是否对CYUSB3014芯片进行数据的读写。

2 软件规划与验证

卫星中频数据收集体系先运用射频芯片、FPGA芯片等硬件进行前期的数据传输等处理,再经过USB接口送入PC机进行后期软件处理。软件规划包含三大部分:FPGA编写对射频前端操控,中频数据接纳传输、USB芯片作业的Verilog程序和CYUSB3014固件程序、PC端收集存储程序规划[9]。

2.1 程序规划

FPGA程序首要完结射频前端操控、USB芯片的接口操控以及生成缓存FIFO,完结数据传输和操控。将中频信号先缓存在USB接口芯片的缓存区内,一起依照FX3的数据接纳时钟发送给FX3,FX3经过特定的固件程序主动完结数据向上位机的发送,经过上位机软件对接纳来的数据进行存储。

FPGA程序开发环境为QUARTUS II,编写Verilog

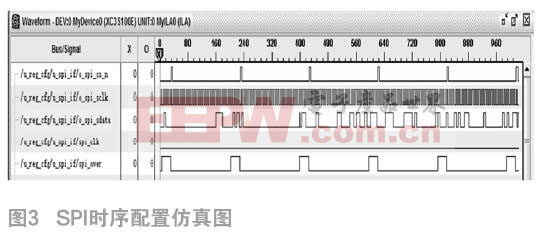

HDL代码,经过SPI串行协议装备设置参数别离接纳GPS和斗极卫星信号,完结多种卫星信号的中频数据接纳。首要经过时序传输对射频前端进行装备,将串行输入端口设置为从ADC输出2位CMOS值,每个寄存器有28个比特位,4个地址位。装备时,数据在先地址在后,串行数据MSB在先,LSB在后。

MAX2769的串行装备时序如图3所示。

经过装备后射频前端输出的卫星中频信号,FPGA将2位串行数据经缓存转化成16位并行数据传输到USB并行数据总线,一起选用Slave

FIFO从机办法对USB芯片进行读写操作的操控,将传送至端点FIFO中的并行数据处理后供上位机完结存储和处理。

固件程序首要完结对CYUSB3014芯片的初始化,装备GPIF II接口为32位同步Slave

FIFO作业形式,外部处理器可像对一般FIFO相同对FX3

FIFO进行读写;将经过采样和FPGA处理后的数据存入CYUSB3014的FIFO缓冲区,并发给主机,接纳和履行PC机的指令,经过UART与FPGA进行通讯[10]。

上位机程序完结数据的传输以及校验,确保数据传输进程正确无误,一起还要完结传输的即时性、灵活性以及简单明了的界面信息显现。上位机软件读取USB端点FIFO的数据,保存到硬盘文件,为接下来的数据测试以及基带处理算法研讨供给数据。

2.2 体系验证

默许收集的GPS L1信号经射频前端下变频为3.996 MHz的模仿中频信号,BD B1中频中心频点为3.996875

MHz,经过A\D采样为2bit数字中频信号,采样时钟为16.369 MHz。MAX2769芯片变频频率规模为1550~1610

MHz,为验证射频前端模块能否正确收集卫星信号,并进行处理,下图4所示为射频开发板衔接实物图,

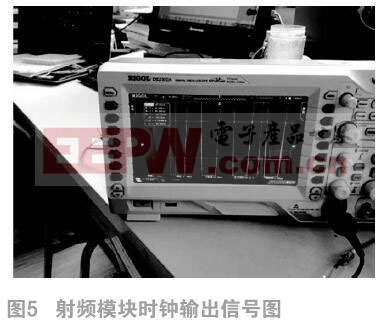

示波器所示对MAX2769装备后输出时钟信号频谱如图5所示。

射频模块屏蔽罩能够有用削减外界环境对射频信号的搅扰,确保接纳机能安稳的作业。卫星中频数据送至信号处理部分,选用的HG-USB30-A开发板,带有USB3.0接口,适用于FPGA数据的收集,操控和开发。

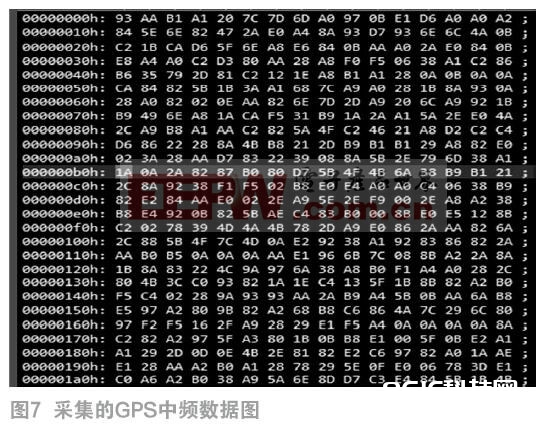

为验证规划的GPS\BD双模单通道中频信号收集体系是否正确作业,建立试验环境,在室外运用该收集体系进行卫星信号收集,经过上位机软件,将接纳到的卫星中频数据保存到硬盘,用16进制文本器检查数据。

中频信号收集体系硬件渠道如下图6所示,图7所示为上位机软件收集到的GPS文本数据。

3 捕获算法研讨

信号捕获是GPS接纳机内信号处理的第一步,是信号盯梢定位、解调导航等后续处理进程的条件,因为卫星的移动和信号的传达,可见卫星及其信号的载波频率,码相位等要害参数是不断改变的,因而接纳机需求经过捕获来确认这些参数,对这以后盯梢环路进行初始化。而怎么完结高动态下的快速捕获是难点[11],传统时域串行滑动相关算法,因为其捕获时间长,资源和功率耗费大的缺陷,本文研讨依据FFT的频域并行码相位捕获算法并对其进行改善。

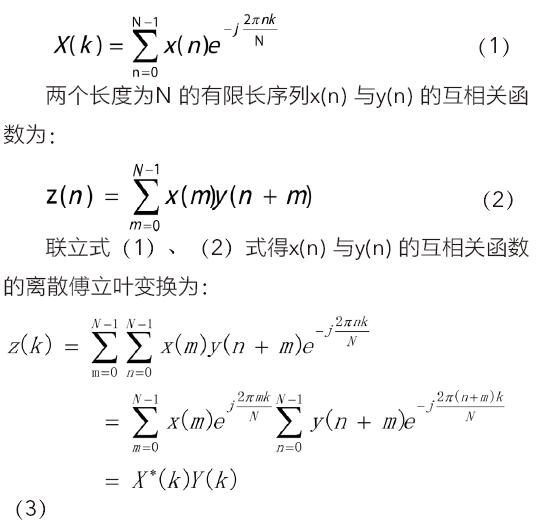

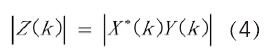

3.1 算法剖析

FFT算法的中心是解扩输入信号,把本地伪码的时域循环运算与中频信号转化到频域中的乘法运算,其本质即输入的中频信号与码相位的二维查找完结同步对齐的进程,长度为N的有限长序列x(n)

的DFT(离散傅立叶改换)为:

依据式(4)能够较快地查找到BD/GPS输入信号和本地信号之间的相关性,从而找到C/A码的开始方位和多普勒频率初始值。

FFT改善算法的体系框图如图8所示。

本文FFT算法依据快速傅里叶改换和信号卷积的联系,详细的捕获进程为:

1)用收集的中频信号数据与本地发生的载波的同向和正交两路信号相乘,再经过低通滤波器得到基带复信号;

2)对复信号做FFT;

3)对本地伪码发生器的输出伪码信号做FFT处理并对它取共轭;

4)对2)、3)进程的成果进行复数相乘并做快速傅里叶反改换IFFT(Inverse Fast Fourier Transform);

5)对第4)步的成果取模与门限比较并断定捕获成果,大于门限即能够为捕获成功。

经过不断调整本地载波频率和伪码相位,直至载波频率差和伪码相位差为零的进程,到达抱负的状况,实际上只需大于设定门限,在信号存在且强度满足的情况下就会完结强自相关峰的成果完结信号的捕获。

3.2 算法完结

用MATLAB编写依据FFT的GPS\BD卫星信号捕获程序,该试验中选用中频信号体系收集到的数字中频信号,中频数据频率为fc=3996875

Hz,采样频率为fs=16367667 Hz,多普勒规模±6500 Hz,多普勒扫描步长500 Hz。C\A码的码元速率为1.023

MHz,整个码周期包含1023个码元,依据一个C\A码周期为1 ms,有5714个离散的采样数据[12],完结捕获处理有必要至少用1 ms的数据。

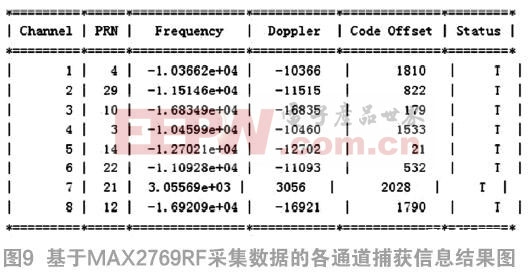

图9所示为捕取得到的各通道卫星信息成果显现图,GPS的28、20号卫星和BD的3、14号捕获三维图如图7所示。尖峰为信号捕获到的相关峰值,当捕获成果中未呈现峰值,标明中频信号中不包含该号卫星的信号,假如呈现了最大相关峰值,阐明收集到的中频信号中包含该号卫星的信号。从图7中可看出此种算法得到了很好的相关峰.

从仿真成果中能够看出,依据FFT的频域并行码相位捕获算法能够有用地捕获到GPS\BD信号,得到可测卫星的编号,以及该卫星码相位以及多普勒频移,是一种快速高效,功用牢靠且利于软件完结的查找办法。

4 定论

本文规划了GPS\BD中频信号收集体系,包含硬件的详细完结进程和软件规划的完结。运用该收集体系能够完结双模单通道卫星信号的接纳,传输和保存等功用,为后续捕获和盯梢算法的研讨供给了牢靠的原始数据。捕获算法研讨用收集到的数字中频信号进行仿真验证,完结了接纳机的根本定位功用,对软件接纳机的研讨有必定工程运用价值和实际意义。

参考文献:

[1]严伟.GPS中频信号收集与捕获技能研讨[J].东南大学学报, 2009,(6):76 ~78.

[2]王晓东.依据FPGA的GPS接纳机16通道快速捕获相关器规划[D].南京理工大学硕士学位论文,2010

[3]悠远,李辰.FPGA运用开发入门与典型实例[M].北京:人民邮电出版社,2010.

[4]胡辉.依据USB2.0的GPS中频数据收集器研发[J].河南师范大学学报(自然科学版),2012,(5):56 ~57.

[5]赵琳,王野,丁继成.依据FPGA和USB的GNSS中频信号收集器规划[J],遥测遥控,2014

[6]李豹,曹可劲,马建国.GPS软件接纳机盯梢环路规划[J].电子规划工程,2010(2):4-6

[7]赵丽,陈小惠,潘树国.GPS频域并行码捕获改善算法[J].北京:电子丈量与仪器学报,2011,25(11):985-991

[8]赵琳,高帅,郭丽姝.GNSS射频前端的多频信号兼容采样[J].我国惯性技能学报,2010(3):316-320

[9]曹冲.高灵敏度 GNSS 接纳机为何特别遭到重视[J].卫星与网络.2006.(12): 38-40

[10]马煦陶,春燕,蒋谢彬.“斗极一号”导航定位体系运用现状及开展趋势展望[C].我国全球定位体系技能运用协会第八次年会论文集.北京:我国全球定位体系技能运用协会,2005,358-360

[11]杨翠翠,朱向东,李帆.依据 USB3.0协议的PC与FPGA通讯体系的规划[J].电子科技,2014

[12]谢钢.GPS原理与接纳机规划[M].北京:电子工业出版社,2009:236-237.

[13]A.Polydoros and C.L.Weber,A unified approach to serial search

spread-spectrum code acquisition[J],IEEE Trans.Commun-Part I:General

theory,2000,32:pp42-49

[14]DAVID WEBER,ROGER BREMER.Universal GPS receiver lets you use a laptop

PC for Soft baseband processing[J].Maxim’s Engineering Journal,2008,63: 1-8

[15]Jin Tian,Qin HongLei,Zhu JunJie,Liu Yang.Real-time GPS Software

Receiver Correlator Design[C].Proceedings of the Second International Conference

on Communications and Networking in China,Beijing,2007, 8:549-553

本文来源于《电子产品世界》2018年第12期第66页,欢迎您写论文时引证,并注明出处。