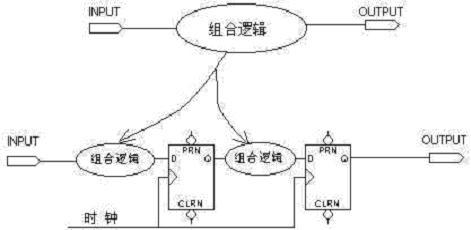

图1是许多为了进步体系时钟选用的拆分大组合逻辑的办法,可是没有供给详细怎么拆分的实例。我觉得实例才是重要的。但我不明白在写代码时,怎么知道这样写会被综组成一个很大的逻辑,一些简略的能够想到(比方大的计数器应该分红多个来做),可是更杂乱的实在是欠好了解。

图1

能够经过流水线的方法分拆组合逻辑,这也是一种进步芯片速度的一种方法。 在组合逻辑中心刺进寄存器,规划成流水。 很典型的比如便是调度器,假如做64调度器,或许中心的延时太长,不能满意体系速度要求,这时候就能够做成一级16调度,一级4调度,来完结64调度的功用。

用加法器做比如,设输入ABCD输出OUT 上半部分便是: out = A+B+C+D;

下半部分便是:

always @(posedge clk)

begin

sumreg1 = sum1;

sumreg2 = sum2;

sumreg3 = sum3; end

assign sum1 = A+B;

assign sum2 = C+D;

assign sum3 = sumrge1+sumreg2;

assign OUT = sumreg3;

一般主张运用下半部分的算法,假如能够运用流水线。

一般是这样的,没有比如看起来是欠好了解,可是一有详细的比如就十分清楚了。我也来学着给个计数器的比如计数255,假如用一个寄存器来计那么需求开的深度为8的,假如拆分为两个那么只需容量为4的两个寄存器,所需的逻辑较小,不知道对不对。

reg[3:0]ad1;

reg[3:0]ad2;

always @(posedge clk)

if(!rest)

begin

out=0;

ad1=0;

ad2=0;

end

else

if(ad1==15)

begin

ad2=ad2+1;

ad1=0;

end

else

if (ad2==15)

begin out=1;

end

else

ad1=ad1+1;

ad1加满后去触发ad2加。

always @(posedge clk)

if (reset)

counter0 = 0;

else

counter0 = counter0 + 1;

always @(posedge clk)

begin

counterreg0 = counter0;

if (counterreg0 == 4’b1111)

outreg0 = 1;

else

outreg0 = 0;

end

assign counter1 = counterreg1 + outreg0;

always @(posedge clk)

begin

counterreg1 = counter1;

if (counterreg1 == 4’b1111)

out = 1;

else

out = 0;

end

lflhust 写的程序没有到达逻辑拆分的意图, 原因很简略, 那个程序综合后生成的电路的流水线深度仍是1。 zf0579那个程序的流水线深度才是2,到达了拆分的意图。 作逻辑的起点不是写HDL代码,而是在写代码前脑子里边要有 你需求完成的逻辑的电路结构。

作逻辑的起点不是写HDL代码,而是在写代码前脑子里边要有。你需求完成的逻辑的电路结构。