0 前语

SAR模数转化器的前端器材包含两个部分:驱动放大器 和RC滤波器。放大器

和RC滤波器。放大器 调理输入信号,一起充任信号源与ADC输入端之间的低阻抗缓冲器。RC滤波器约束抵达ADC输入端的带外噪声,协助衰减ADC输入端中开关电容的反冲影响。

调理输入信号,一起充任信号源与ADC输入端之间的低阻抗缓冲器。RC滤波器约束抵达ADC输入端的带外噪声,协助衰减ADC输入端中开关电容的反冲影响。

为SAR ADC挑选适宜的放大器 和RC滤波器或许很困难,特别是当运用不同于ADC数据手册的惯例用处时。依据各种影响放大器

和RC滤波器或许很困难,特别是当运用不同于ADC数据手册的惯例用处时。依据各种影响放大器 和RC挑选的运用要素,咱们供给了规划攻略,可完成最佳解决方案。首要考虑要素包含:输入频率、吞吐速率和输入复用。

和RC挑选的运用要素,咱们供给了规划攻略,可完成最佳解决方案。首要考虑要素包含:输入频率、吞吐速率和输入复用。

1 挑选适宜的RC滤波器

要挑选适宜的RC滤波器,有必要核算单通道或多路复用运用的RC带宽,然后挑选R和C的值。

图1显现了一个典型的放大器 、单极点RC滤波器和ADC.ADC输入构成驱动电路的开关电容负载。其10 MHz输入带宽意味着需求在宽带宽内确保低噪声以取得杰出的信噪比(SNR)。RC网络约束输入信号的带宽,并下降放大器和上游电路馈入ADC的噪声量。不过,带宽约束过多会延伸树立时刻并使输入信号失真。

、单极点RC滤波器和ADC.ADC输入构成驱动电路的开关电容负载。其10 MHz输入带宽意味着需求在宽带宽内确保低噪声以取得杰出的信噪比(SNR)。RC网络约束输入信号的带宽,并下降放大器和上游电路馈入ADC的噪声量。不过,带宽约束过多会延伸树立时刻并使输入信号失真。

图1. 典型放大器、RC滤波器和ADC

在树立ADC输入和经过优化带宽约束噪声时所需的最小RC值,能够由假定经过指数方法树立阶跃输入来核算。要核算阶跃巨细,需求知道输入信号频率、起伏和ADC转化时刻。转化时刻tCONV(图2)是指容性DAC从输入端断开并履行位判别以发生数字代码所需的时刻。转化时刻结束时,保存前一样本电荷的容性DAC切换回输入端。此阶跃改变代表输入信号在这段时刻的改变量。此阶跃树立所需的时刻称为“反向树立时刻”.

图2. N位ADC的典型时序图

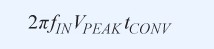

在给定输入频率下,一个正弦波信号的最大不失真改变率可经过下式核算:

假如ADC的转化速率大大超出最大输入频率,则转化期间输入电压的最大改变量为:

这是容性DAC切换回收集形式时呈现的最大电压阶跃。然后,DAC电容与外部电容的并联组合会衰减此阶跃。因而,外部电容有必要相对较大,到达几nF.此剖析假定输入开关导通电阻的影响可忽略不计。现在需求树立的阶跃巨细为:

接下来核算在ADC收集阶段,ADC输入树立至½LSB的时刻常数。假定阶跃输入以指数方法树立,则所需RC时刻常数τ为:

其间, tACQ 为收集时刻, NTC 为树立所需的时刻常数数目。所需的时刻常数数目能够经过核算阶跃巨细 VSTEP, 与树立差错(本例为½LSB)之比的自然对数来取得:

因而,

将上式代入前面的公式可得:

等效RC带宽 =

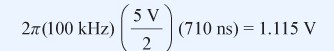

示例: 凭借RC带宽核算公式,挑选16位ADC AD7980 (如图3所示),其转化时刻为710 ns,吞吐速率为1 MSPS,选用5 V基准电压。最大方针输入频率为100 kHz.核算此频率时的最大阶跃:

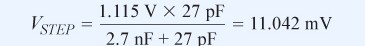

然后,外部电容的电荷会衰减此阶跃。运用27 pF的DAC电容并假定外部电容为2.7 nF,则衰减系数约为101.将这些值代入 VSTEP 核算公式:

接下来核算树立至½LSB(16位、5 V基准电压)的时刻常数数目:

收集时刻为:

核算τ:

因而,带宽为3.11 MHz, REXT 为 18.9 .

图3. 选用16位1 MSPS ADC AD7980的RC滤波器

最小带宽、吞吐速率和输入频率之间的这种联系阐明:输入频率越高,则要求RC带宽越高。相同,吞吐速率越高,则收集时刻越短,然后进步RC带宽。收集时刻对所需带宽的影响最大;假如收集时刻加倍(下降吞吐速率),所需带宽将折半。此简化剖析未包含二阶电荷反冲效应,它在低频时变成首要影响要素。输入频率十分低时(10 kHz,包含DC),容性DAC上树立的始终是大约100 mV的电压阶跃。此数值应作为上述剖析的最小电压阶跃。

多路复用 输入信号很少是接连的,一般由不同通道切换发生的大阶跃组成。最差情况下,一个通道处于负满量程,而下一个通道则处于正满量程(见图4)。这种情况下,当多路复用器切换通道时,阶跃巨细将是ADC的满量程,关于上例而言是5 V.

图4. 多路复用设置

在上例中运用多路复用输入时,线性呼应所需的滤波器带宽将进步到3.93 MHz(此刻阶跃巨细为5 V,而非单通道时的1.115 V)。假定条件如下:多路复用器在转化开端后不久即切换(图5),放大器和RC正向树立时刻足以使输入电容在收集开端前稳定下来。

图5. 多路复用时序

关于核算得到的RC带宽,能够使用表1进行检查。从表中可知,要使满量程阶跃树立至16位,需求11个时刻常数(如表1)。关于核算的RC,滤波器的正向树立时刻为11 × 40.49 ns = 445 ns,远少于转化时刻710 ns.正向树立不需求悉数发生在转化期间(容性DAC切换到输入端之前),但正向和反向树立时刻之和不该超越所需的吞吐速率。关于低频输入,信号的改变率低得多,因而正向树立并不十分重要。