简介

控制器局域网络(CAN)可在多个网络站点之间供给强壮的通讯才能,支撑多种数据速率和距离。CAN具有数据链路层裁定、同步和错误处理等特性,广泛用于工业、仪器仪表和轿车运用之中。在ISO 11898标准的框架下,凭借分布式多主机差分信令和内置毛病处理功用,DeviceNet、CANopen等多种协议针对物理层和数据链路层规则了相应的完成方法。本文旨在描绘怎么针对给定运用优化设置,一起考虑控制器架构、时钟、收发器、逻辑接口阻隔等硬件约束。文章将会集介绍网络装备问题——包含数据速率和电缆长度——阐明何时有必要对CAN节点进行重新装备,以及怎么从一开端就完成对节点的优化装备。

逻辑接口阻隔

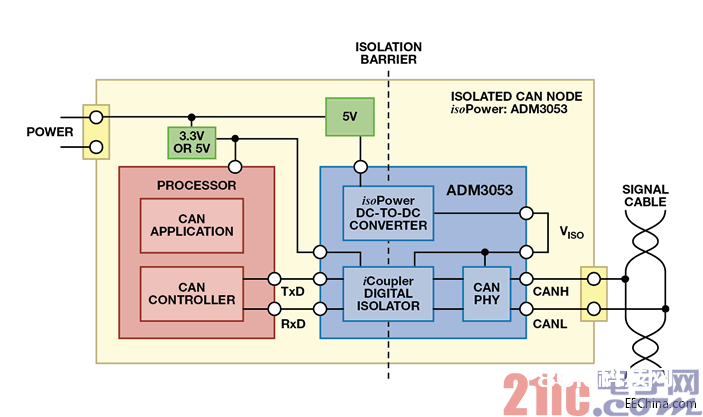

关于恶劣的工业和轿车环境,可经过阻隔CAN收发器的逻辑接口进一步增强体系的鲁棒性,答应接地节点之间呈现较大的电位差,一起供给抗高电压瞬变才能。 将CAN收发器与数字阻隔器集成起来即可构成阻隔式CAN节点。 ADM3052、ADM3053和ADM3054阻隔式CAN收发器供给多种接口供电选项。 关于DeviceNet网络,阻隔侧可经过总线供电;因而,ADM3052集成了一个线性调理器,以便运用24 V总线电源供给5 V电源。ADM3053(如图1所示)集成了一个isoPower DC-DC转换器,用于驱动收发器和数字阻隔器的总线端。已有一个阻隔式DC-DC转换器能够在阻隔栅上供给电源的体系能够选用ADM3054,后者只集成了数字阻隔器和CAN收发器。

图1. 阻隔式CAN节点(ADM3053收发器由isoPower DC-DC供电)

传达推迟的影响

布置一个CAN节点需求一个阻隔式或非阻隔式CAN收发器,以及一个搭载有相应协议仓库的CAN控制器或处理器。能够运用独立式CAN控制器,乃至能够运用不带标准协议仓库的控制器,可是,CAN运用中运用的微处理器或许现已包含CAN控制器。在任一状况下,都有必要对CAN控制器进行装备,以谐和总线上的数据速率和时序,而硬件振荡器则用于控制器。

跟着电缆长度的添加,信号中的高频组分衰减,因而,长距离条件下的数据速率都有限。 总线是一种多主机,因而,一切节点都能够测验一起传输,裁定取决于物理层信令。传达推迟也会随电缆长度而添加,或许对节点间同步和裁定构成搅扰。

CAN总线上的差分信号或许处于两种状况之一:主动(逻辑0,信号线路CANH和CANL之间存在一个差分电压)或被迫(逻辑1,无差分电压,一切CAN收发器输出均为高阻抗)。假如两个节点测验一起传输,则主动位传输会掩盖一起进行的被迫位传输,因而,在传输时,一切节点都有必要监控总线状况,假如在传输被迫位时产生掩盖,则要中止传输。如此,传输主动位的节点赢得裁定,如图2所示。

图2. 两个CAN节点之间的裁定逻辑

CAN 2.0b界说的是数据链路层的完成方法,对用于传输的CAN帧结构进行了规则。一个包含音讯ID的裁定字段发动音讯传输。较低的音讯ID(最初的零较多)将具有更高的优等级,因而,在传输音讯时,相应节点赢得裁定的概率更大。

虽然CAN节点与总线传输同步,可是,因为两个一起传输的节点之间存在传达推迟,所以不会完全同步。要让裁定实在发挥作用,传达推迟不能过大,不然,较快的节点或许在检测到较慢节点传输的位状况之前就对总线进行采样了。最差条件下的传达推迟为两个最远节点间推迟的两倍。在图3中,假如节点A和B是总线上相隔最远的节点,则至关重要的参数是双向传达时刻PropBA与TPropBA之和。

图3. 实践条件下两个CAN节点间的裁定(含传达推迟)

总传达推迟由经过电缆、两个CAN控制器I/O和两个CAN收发器的双向传达时刻构成。CAN控制器I/O并不是传达推迟的首要贡献者,往往能够忽略不计,但进行完全评价时有必要予以考虑。循环时刻由从TxD到CANH/CANL、再回到RxD的传达推迟构成。电缆传达推迟取决于电缆和距离,典型值为5 ns/m。

在较低数据速率下,答应的位时刻较长,因而,传达推迟(及电缆距离)也或许变长。在最高标准CAN数据速率(即1 Mbps)下,答应的传达推迟更受约束,虽然ISO 11898-2标准规则,在总线长40米时,可支撑1 Mbps的数据速率。

阻隔的影响

阻隔条件下,在核算双向传达推迟时,有必要考虑额定的要素。比较光耦合器,数字阻隔器可削减传达推迟,但即使是最快的阻隔式CAN收发器在这方面也与较慢的非阻隔式收发器适当。假如答应的总传达推迟坚持不变,阻隔体系中,最大电缆长度较短,但能够重新装备CAN控制器,以进步答应的总传达推迟。

传达推迟的补偿

为了补偿因较长总线或阻隔添加的传达推迟,有必要为CAN控制器设置与时序和同步相关的特定参数。在装备控制器时,不只是挑选一个数据速率,而是要设置决议着控制器所用位时刻的变量。面向振荡器或内部时钟的波特率预分频器(BRP)设置时刻量子(TQ),位时刻为TQ的倍数。振荡器的硬件挑选,以及BRP和每位时刻TQ数的软件装备设定数据速率。

控制器的位时刻分为三个或四个时刻段,如图3所示。每位时刻的TQ总数包含一个同步以及传达推迟(PROP)、相位段1 (PS1)和相位段2 (PS2)的设定数量。有时候,会把PROP和PS1加起来。装备调理采样点,以支撑传达推迟和再同步。

把采样点设在位时刻的稍后部分能够支撑更长的传达推迟,但就如总数据速率相同,采样点取决于其他时序变量,这些变量都有自己的约束。例如,内部时钟/振荡器或许固定不变,只能运用整数BRP和TQ数。因而,特定电缆长度要求的抱负数据速率或许底子无法完成,因而,有必要缩短电缆,或许下降数据速率。

再同步会使PS1加长,PS2缩短,加长量和缩短量为同步跳宽(SJW)规则的TQ数,因而,PS2不得短于SJW。 SJW所需TQ数取决于CAN控制器的时钟容差,关于SJW和PS2,晶振一般支撑最小TQ数。

CAN控制器的装备

为了完成节点间时序牢靠、同步牢靠的稳健网络,体系有必要能接受所选数据速率和CAN控制器时钟条件下的传达推迟。假如不能,能够挑选下降数据速率、缩短总线或许运用不同的CAN控制器时钟速率。装备进程包含以下三个过程。

第一步: 查看时钟和预分频器——匹配数据速率

先核实在给定方针数据速率和CAN控制器时钟条件下,有哪些或许的装备。TQ距离有必要依据时钟和各种BRP值核算,或许组合只需那些TQ距离为位时刻的整数倍的组合。依据所在体系设计阶段,也或许考虑其他CAN控制器时钟速率。在表1所示核算示例中,给定的最大数据速率为1 Mbps,运用的是一个Microchip® MCP2515独立CAN控制器和一个内置CAN控制器的ADSP-BF548 Blackfin 处理器。MCP2515 fOSC 取决于所运用的外部硬件振荡器,而ADSP-BF548 fSCLK 则取决于硬件CLKIN和内部PLL设置(VCO的CLKIN乘数,SCLK的VCO分频)。只需CAN控制器时钟和BRP(整数个TQ)的某些组合支撑1 Mbps的数据速率,如粗体所示。 这会约束位时序的设置,因而一旦挑选某个总线数据速率,只需部分选项可用。

表1. 给定f和BRP时1 Mbps速率下的TQ数

第二步: 确认位段装备

下一步是确认每个位段要求的TQ数。最困难的状况是在1 Mbps的数据速率下支撑最大传达推迟,例如,电缆长40米,阻隔式节点。抱负状况下,应对位时刻段进行装备,使采样点在位中尽量晚。在表1中,关于每个整数的TQ总数,一个TQ有必要供给给SYNC段,PS2(或TSEG2)段有必要足够大,以包容CAN控制器信息处理时刻(只需BRP大于4,MCP2515为2 TQ,ADSP-BF548为小于1 TQ)。别的,关于MCP2515,PROP和PS1最多能够各有8 TQ;关于ADSP-BF548,TSEG1 (PROP + PS1)最多能够为16 TQ。

图4和图5别离展现了MCP2515和ADSP-BF548的或许总TQ装备,关于1 Mbps速率条件下的有用时钟和BRP组合,可支撑最近采样点。MCP2515的最佳TQ总数为19,要求38 MHz的硬件振荡器和1的BRP。关于ADSP-BF548,TQ总数为5的状况在外,一切装备至少为85%采样点,但最佳设置是10 TQ,要求fSCLK = 50 MHz且BRP = 5。

图4. MCP2515的或许TQ总数装备(速率为1 Mbps,最大传达推迟)

图5. ADSP-BF548的或许TQ总数装备(速率为1 Mbps,最大传达推迟)

第三步: 使收发器/阻隔推迟和总线长度与装备相匹配

在协助CAN控制器完成最佳采样点今后,最终一步是比较答应的传达推迟与运用的CAN收发器/阻隔器和总线长度。设ADSP-BF548最佳装备为10 TQ(fSCLK= 50 MHz,BRP = 5),或许完成的最大传达推迟为900 ns。 关于集成阻隔式电源的ADM3053阻隔式CAN收发器,数据手册中的最大环路推迟(TxD封闭,接纳器处于非活动状况)为250 ns。有必要使其添加一倍(500 ns),以便一起支撑总线最远两头的两个节点处的发射推迟和接纳推迟。

设电缆传达推迟为5 ns/m,ADSP-BF548能够支撑40米的总线长度(依据ISO 11898标准,此为1 Mbps条件下的最大值),ADSP-BF548的位时刻总共为10 TQ,TSEG2位段仅1 TQ。实践上,略早的采样点就够了,因为一个节点上的极点收发器传达推迟乃至很或许导致简略的再传输(由数据链路层CAN控制器主动处理),可是,因为CAN控制器I/O与CAN收发器之间存在小推迟,因而主张把采样点装备到尽量靠后的点。

定论

阻隔有利于进步鲁棒性,但一起也会添加发射和接纳两个方向的传达推迟。有必要使该推迟添加一倍,以支撑两个节点参加裁定。 假如体系答应的传达推迟是固定的,在添加阻隔办法之后,能够削减电缆长度或数据速率。另一种方法是重新装备CAN控制器,使其支撑最大传达推迟,以确保支撑所需的数据速率和总线长度,即使是在节点采取了阻隔办法的条件下。