多核处理器在嵌入式设备中无处不在,可是关于开发安全要害型设备来说,仍然是一个严峻应战。多核处理器供给实在的并发性,意味着需求实在多线程的编程,这依旧很难处理。在使命要害型软件中,静态剖析是要害,由于它能够捕捉到传统测验(例如单元、功用和体系测验)遗失的缺点,及开发者花费数个小时乃至许多天才能处理的缺点。在安全与保安要害型体系中,多核渠道的优势有必要大于危险。

安全要害型体系中的多核

多核处理器及其相应的硬件渠道为安全要害型体系供给许多重要的功用:

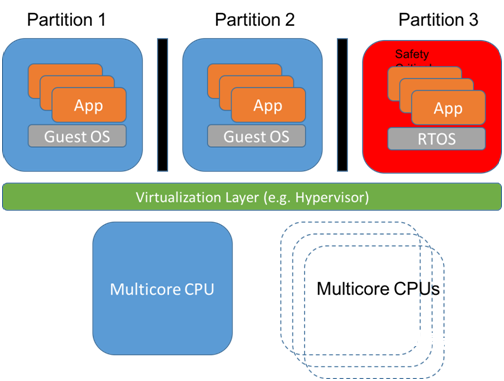

1.分区:一个单一硬件单元能够经过虚拟分区装置多个操作体系和应用软件。多核CPU为强壮的分区供给功用和处理器支撑。

2.切割:类似于分区,可是能够将体系要害部分与非要害部分切割开来。例如,嵌入式渠道能够装置一个实时操作体系,来操控一个带用户界面的强壮且多功用的操作体系。

3.整合:多核渠道在单一渠道上供给切割功用,大幅削减产品所需的资料本钱。进步单位电压的处理器功用会下降运转本钱。

图1. 在多核渠道上选用虚拟分区的体系事例。依照要害性和功用来切割是具有可操作性的。

可是,多核处理器为多线程软件引进了实在且依据硬件层级的并发功用,而在开发编程中十分难侦测并处理潜在缺点。虽然在极点状况下,能够向单一线程操作体系中强制施加安全要害性代码,可是功率却十分低。挑选恰当的并发程序设计和正确的东西能够使得多核处理器上编程的危险较低。

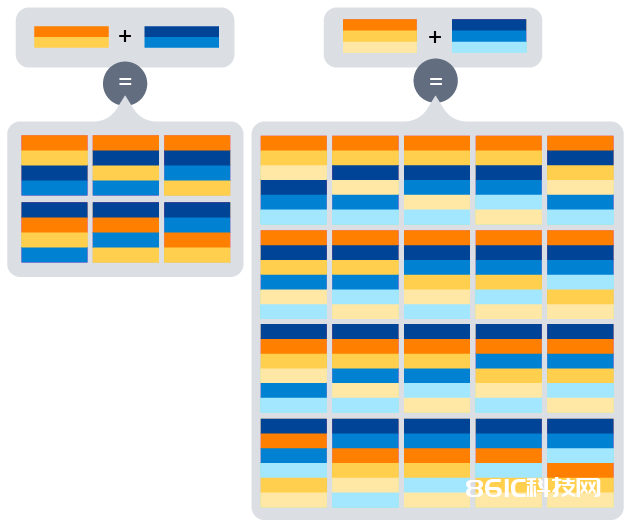

传统单元测验与多核并发编程比较

一般来说,单元测验假设为单线程操作体系——为估计输出供给输入和输出查看。在多线程编程中,“单元”之间的联系杂乱,正确的测验办法是需求优先考虑的要素。多核渠道加入了实在的硬件并行行,这就意味着线程是实在并行运转的。此外,事情在体系中的方案和调度变得不确定,由于指令交织在可用的处理器内核(或许超线程CPU线程)中。下图显现了从两个指令和两个线程到三个指令与两个线程之间交织的杂乱性。依据安全要害程度,这或许会被制止。假如不制止,那么就意味着需求特别当心,以保证正确操作。

这种杂乱性明显增加了测验的工作量、缺点的危险度和脆弱性。幸运地是,静态剖析东西能够协助检测数据拜访抵触状况和同步缺点,这些在单元测验和次级单元测验中都很难被勘探出来。

静态剖析,侦测并发问题

静态剖析东西创立剖析软件的内部表征(IR),以推理出估计的行为。作为这种推理的一部分,它能够侦测或许会逾越传统测验技能的抵触状况和并行性问题。GrammaTech CodeSonar能够侦测出多线程并行应用程序中的以下杂乱缺点:

—-数据抵触:当两个线程都拜访一个同享数据,且没有明晰且正确的同步时,会呈现数据抵触。这种过错解导致体系处于不稳定状况,或许会偶然随机呈现。

—-死锁:当单线程经过同步机制拜访同享资源,但没有为其它线程拜访开释时,就会呈现死锁。这通常是由于一起选用了多种同步机制(确定一个资源后再确定第二个,但仍然处于等候状况)。

—-进程饥饿现象:当线程被阻塞在一个同步目标上很长一段时间时,就会发生饥饿现象(starvation)。在实时软件中,这会影响体系运转,或触发监督正告。

—-不妥同步:乱用线程同步源语,例如缺失确定或解锁对导致不行猜测的体系行为。CodeSonar能勘探到软件中的多种确定和解锁乱用。

安全与保安的影响

并发过错和不妥线程行为关于开发者进行侦测、确诊和修正来说是一个令人头疼的问题。由于这些过错解对体系行为发生严峻影响,因而,它们会发生巨大的安全与保安危险。在极点状况下,实在的并发编程会由于安全问题(会选用上述分区来处理)遭到制止。但是,运用实在并发会带来功用优势,这两者是并行的。选用时,需求加倍当心。

静态剖析东西为测验安全要害性体系供给绝无仅有的优点,由于他们不依托测验用例(反过来,这或许有缺点),而且处理传统体系测验无法处理的问题。在布置的使命要害型软件中,在布置前或许没有发现的严峻并行缺点,运用CodeSonar会发现并处理。

由于潜在的影响,运用并发缝隙是一个稳重的考虑。触发并发过错解导致体系不稳定和拒绝服务,乃至更糟。好像一切其它的潜在缺点相同,假如存在要挟向量,需求依照正确的优先级进行处理和呼应,那么并发过错或许也是安全缺点。

总结:

传统测验往往忽视并发问题,只到体系测验阶段才会发现,或许彻底遗失——此刻现已太迟、太危险,也太过于昂贵了。在安全性体系中,这就意味着很多的返工和从头测验,由于验证环境意味着高额本钱。GrammaTech CodeSonar在前期,即开发代码时,经过体系行为剖析,无须很多的测验,即可检测这些问题,下降危险,节省本钱。