1 导言

有两种根本的数字化采样办法:实时采样(real-time sampling)与等效采样(equivalent time sampling)。实时采样对波形逐点收集,能够实时显现输入信号的波形,因而适用于任何办法的信号波形,重复或许不重复的,单次的或许接连的。因为所收集的样点是按时刻次序的,因而易于完结波形的显现功用;实时采样的首要缺陷是时刻分辨率较差。每个样点的采样、量化、存储有必要在小于采样距离的时刻内完结。依据Nyquist 采样定理为能够完结的重建波形采样频率至少应为信号最高频率的2倍,因而对实时采样提出了更高的要求。鉴于此呈现了等效采样技能。等效采样技能能够完结很高的数字化转化速率。其根本原理便是经过屡次触发,屡次采样而取得并重建信号波形。条件是信号有必要是重复的。等效采样经过屡次采样,把在信号的不同周期中采样得到的数据进行重组,然后能够重建原始的信号波形。

2 等效采样的原理和办法

等效采样的根本原理是把高频、快速信号变成低频、慢速重复信号。一般在重复信号的每个周期或相隔几个周期取一个样,而每个取样点别离取自每个输入信号波形不同的方位上,若干个取样点成为一个周期,能够组成类似于原信号的一个周期的波形,可是周期拉长了。例如收集一个停止图画帧数据(采样每秒30 帧规范)的采样计划。假定一幅画面的带宽是6MHz.选用实时采样办法,感觉采样定理,采样频率应为12MHz。假如选用等效时刻采样办法,能够采样100kHz 的模数转化器,每隔120 个像素采样一次,帧间采样率稍低于100kHz确保挪后一个像素。则对榜首帧采样的成果是1,121,241…像素的数据,第二帧则是2, 122,242…像素的数据。这样继续4 秒,收集120 帧数据,然后得到400k 的整个图画帧数据。显着再这个进程中咱们利用了画面的停止特性,也便是利用了信号的重复性。

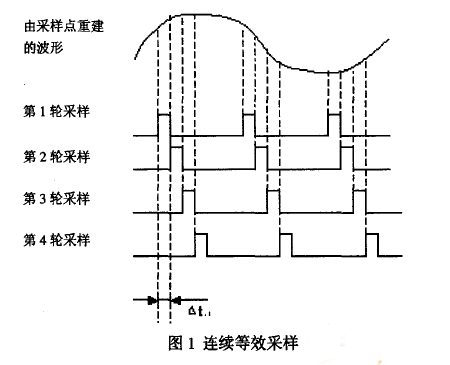

有两种等效采样的办法:随机等效采样和接连等效采样。接连等效采样在每个触发捕获一个样值,而不依赖于时刻/格的设置和扫描速度,每发现一个触发经过一个虽然很短却清晰的推迟(deltat) ,就取得样值。当发生下一次触发肘,推迟添加一段小的增量△t。这个增量便是等效样的周期。数字转化器则又采下一个样值。该进程重复屡次. deltat 不断添加到前一个捕获量中,直到时刻窗口填满。如图1 示:

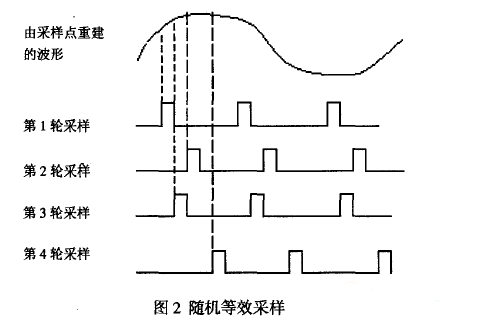

随机等效采样选用内部的时钟,它与输入信号和信号触发的时钟不同步,样值接连不断的取得,并且独立于触发方位。经过记载采样数据与触发方位的时刻差来确认采样点在信号中的方位来重建波形。这就发生了精确丈量与采样触发点相关的方位的问题。这是随机等效采样的难题之一。虽然采样在时刻上是接连的,可是相关于触发器则是随机的,由此发生了随机等效时刻采样的说法。如图2 所示.。

关于依照等效采样得到的信号是否包括有原信号的悉数频率成分,下面给出剖析。

将接连信号x(t)和冲激函数p(t)相乘即可得到采样后的离散信号x(n Ta)。

x(n Ta)=x(t)xp(t) (1)

因为输入信号是周期信号,所以关于任一采样点x(t-kT-mTl-jTa)

因为T1/Ta, 为整数,有

F[x(t-kT-mTl- jTs)]=F[x(t-qTs )]eiPTax(2)

所以采样点x(t-kT-m Tl –jTa )所包括的信息和x(t-q Ta)所包括的信息量相同,因而咱们用采样点x(t-kT-mTI-j Ta)来替代x(t-q Ta)重建输人信号的波形。

采样数据经过重组算法重组后p(t)变为

由此能够看出,此定论和咱们了解的采样定理具有相类似的成果。只需等效采样的细小的时刻增量△t 满意的小即满意1/△t≥2fmax就能够恢复出原信号。

不论选用哪一种办法,最终对收集的数据经过特定的算法进行重组,都完结原始输入信号波形的重建。重组后的数据的采样事都是每一轮采样之间采样信号之间的推迟的细小增量△t来确认的。经过操控这个△t的巨细,就能够操控等效采样的频率,也便是实践采样的频率。假如这个△t满意的小,也便是等效采样的频率满意高,对各种高频成分都能够收集到。这样就完结了低频收集高频。

3 依据EDA 技能的等效采样计划

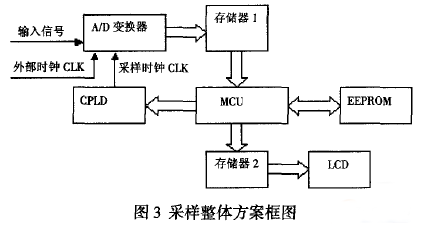

本计划是关于接连等效时刻采样的研讨成果。等效时刻采样是针对输入信号是周期信号的采样办法,并且对杂乱的周期信号失效。本计划因为选用了依据EDA 技能的采样信号发生电路,能够处理杂乱周期信号等效采样失效的问题,进一步下降了对输入信号的要求。本计划的另一大特征是,改变了接连等效采样一个采样信号只能做一次采样的办法,在整个作业进程中,A/D 变换器在采样信号的操控下,一向处于作业状况。采样功率能够到达随机等效采样的水平,又能够防止随机等效采样的不行操控时隙的问题。全体计划框图如图3 。

其间, A/D 变换器有两个作业时钟,对应于两种作业状况。一个时钟是由外部震动器发生,一个由CPLD 发生;存储器1为双端口存储器,用来暂存收集的数据;存储器2 寄存重组后的数据;CPLD 用来发生采样信号;MCU 担任整个体系的操控,并完结数据重组。

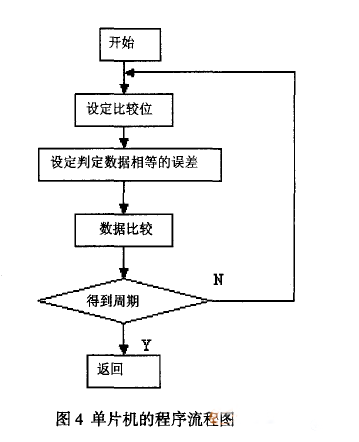

本计划的作业进程分两步,首要A/D 对输入信号采样,收集后的数据寄存到RAMI 中,然后单片机对收集后的数据处理计算出输入信号的周期或许周期的整数倍。传统的等效采样信号的发生多选用电平触发的办法,在输入信号相同电平的方位就发生一次触发。传统办法只是由一个方位的电平相同就确认为下一周期的开端,用这种办法来判别周期是很不严厉的,假如关于杂乱的周期信号,假如在一个周期中有两个或许更多个相同的电平,这种办法显着是失效的。本计划因为A/D 变换器对输入信号的一个周期内收集了接连的满意多的数据,经过判别这些数据的周期来得到输入信号的周期。这种办法相当于对不同周期的多个方位进行电平的比较,能够处理杂乱周期信号的等效采样失效问题。CPLD 依据取得的周期数据发生采样信号。

第二种作业状况下为等效采样形式, A/D 变换器依据CPLD发生的采样信号对输入信号进行采样。收集后的数据寄存到RAM1 中,然后由MCU 对收集后的数据依照本文提出的数据重组算法进行重组,重组后的数据寄存到RAM2中,能够供显现设备运用或许进行进一步的处理。整个进程的操控由单片机完结,本计划选用的MCU 为89C51 。

4 信号周期的取得

传统的触发办法多选用电平触发,这种办法对杂乱的周期信号失效。本计划选用数字化办法来直接取得输入信号的周期。当有信号输入时, A/D 芯片首要作业在接连采样形式下,直到存储器满。因为输入信号为周期信号,设周期为T ,又设A/D转化器的时钟周期为T1,则最多经过T*T1时刻后采样数据开端重复。单片机能够对收集的数据经过比较算法很简单的得出输入信号的周期或许周期的整数倍。这个数据便是采样信号发生的根底。CPLD 依据得到的信号的周期来发生采样信号。

5 采样信号的发生

采样信号有必要满意以下几个要求:(1)能够重复发生。(2)每个采样信号依据等效采样的周期发生一个步进。本计划的采样信号,改变了传统的采样信号每个周期只能发生一个采样信号,每个采样信号发生一个采样数据的办法,在输入信号的每个周期内一向依照A/D 变换器的作业频率进行采样。到达和随机等效采样根本相同的速度。并旦防止了丈量与采样触发点相关的笔直和水平方位。特别是对频率低于A/D 变换器时钟的输入信号有显着的优势。

下面是用VHDL 言语编写的收集信号的发生程序及其仿真波形。

UBRARY IEEE; USE IEEE.STD_WGIC_1164.ALL;

ENTITY clk_d IS

PORT(CLK:INSTD)_LOGIC; clkf: OUTSTD_LOGIC);

END clk_d;

ARCHITECTURE behav OF clk_d IS

SIGNAL m:STD_LOGIC_VECTOR(9 DOWNTO 0);

SIGNAL n,k:STD_LOGIC_VECTOR (7 DOWNTO O);SIGNALn7,fc:STD_LOGIC:=’O’;

BEGIN

PROCESS(clk)

BEGIN

IF clk’EVENT AND CLK=’1′ THEN

IF m =0000000000 THEN k=k+l;n=k; m

END IF; END IF;

END PROCESS;

PROCESS(n7)

BEGIN

IF n7’EVENT and n7=’O’ then fc=not fc; END IF;

END PROCESS;

n7=n(7);clkf=fc;

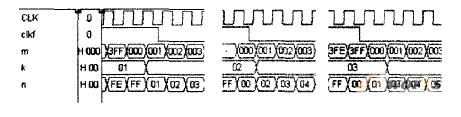

END behav;仿真波形如下图所示:

由以上仿真波形能够看到采样信号以输入信号的周期为距离移动了一个时钟(CLK)周期这样经过若干轮采样今后,将以收集的数据刚好以时钟(CLK)频率完结对输入信号的采样。依据Nyquist 采样定理,将能够采到输入信号中频率为clk/2 的成分,这样就能够完结用低频收集高频信号。

6 结束语

经过对接连等效采样的研讨。进一步下降了等效采样对输入周期信号的要求,处理了杂乱周期信号采样失效问题。一起因为EDA 技能的运用,还能够便利的发生采样信号,使A/D 变换器一向作业于采样形式下,改变了传统的采样形式下一个采样信号只能收集一个数据的问题,提高了体系的作业速度,能够到达和随机等效采样相同的功能,并且又避开了随机等效采样中丈量与采样触发点相关的笔直和水平方位的问题,大大下降了硬件电路的杂乱性。

本文作者立异点是用EDA 技能,便利地发生了采样信号,大大简化采样触发电路,处理了传统等效采样对杂乱周期信号失效的问题,进一步下降对输入信号的要求,并提高了体系的作业速度,并且下降了硬件电路的杂乱性。