在现代电子体系中,数字化和集成化成为开展的必然趋势,电子规划自动化(EDA)技能现已逐步成为电子体系规划的首要方向和潮流,传统的数字体系没计办法现已逐步被筛选。作为电子工程师和体系规划人员学习、把握相关常识和技能已势在必行。EDA便是运用计算机规划电子电路和体系的软件东西,极大地提高了电路规划的功率和可靠性。减轻了规划者的劳动强度。它的完结是与可编程逻辑器材CPLD/FPGA(ComplexPro—grammableLogicDevice/FieldProgrammableGateArray)技能的迅速开展休戚相关的。这一类器材能够通过软件编程对其硬件结构和作业办法进行重构,打破了软硬件之间的屏障。美国Altera公司推出的开展较完善的MAX+Plush软件便是用于开发CPLD的EDA软件东西,它界面友爱。易学易用并具无与伦比的灵敏性和高效性。

1. MAX+Plusll软件开发渠道介绍

规划CPLD时能够运用Altera公司供给的免费根本版MAX+PlusIll0。2软件完结。此软件可通过Altera公司网站免费下载。

MAX+Plush软件的规划流程分四步。即规划输入、规划编译、规划验证和器材编程。

①规划输入。MAX+Plush软件的规划输入的办法有多种,首要包含:

原理图输入办法:这种输入办法多用于不太杂乱的体系规划中,关于咱们的频率计规划就能够选用。由于用此办法不光便利也很直观。

文本规划输入办法:文本规划文件能够运用AHDL言语、VHDL言语、VerilogHDL言语。三种都是硬件描绘言语,每种都有其各自的特色。

波形输入办法:规划者依据树立的输入,输出波形生成逻辑联系,本规划将不运用这种输入办法,但能够运用波形联系进行规划验证。

②规划编译。MAX+P1usII供给了一个全集成编译器,编译进程阅历网表提取,数据库树立,逻辑归纳,资源分配,适配,时序仿真网表文件提取,安装等环节。生成一系列标准文件,若在其间某个环节呈现过错,编译器会中止编译,告知你过错呈现的方位及原因。

③规划验征。MAX+Plush还有时序剖析,功用仿真,输入输出波形剖析等功用,以协助验证规划的正确性。

④器材编程。对规划文件编译。仿真后,将规划的项目下载(或称为装备)到所选器材上的进程。

2. 数字电路规划

PLD规划中,原理图输入比较直观。功率高,但规划大规模CPLD时显得很繁琐。当进行大规模CPLD规划时一般挑选文本输入办法。如前所述,文本输入有AHDL、VHDL、VerilogHDL三种言语,咱们挑选其间VHDL言语简略介绍给我们。VHDL言语硬件描绘才能很强。同样是根据英语的一种编程言语。相似其他高档编程言语。只需有必定英语常识,就会很简略把握并了解VHDL言语的描绘。

(1)电路功用描绘

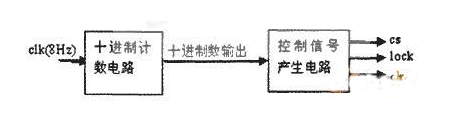

运用VHDL言语规划一个简略的数字电路。原理框图如图1所示,该电路用于计数电路之前的操控信号发生,功用要求是对外部电路发生送入的clk(8Hz)信号进行计数,输出信号送入操控电路周期性地发生3个信号操控后级计数电路,这三个信号分别是:

①闸口信号CS,也称计数操控信号:操控计数模块的计数和中止计数,计数控CS的高电平部分正好是1秒,CS的低电平部分是计数模块中止计数时刻。

②锁存信号lock:当计数模块在1秒时刻计数完毕后发生一个送数信号,即把计数信号送进锁存器,高电平有用。

③清零信号clr:在每次计数模块开端计数前,铲除模块内原先的计数值,使其为零,同样是高电平有用。

图l 电路原理框图

(2)电路规划

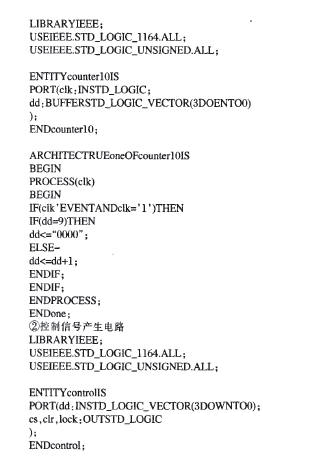

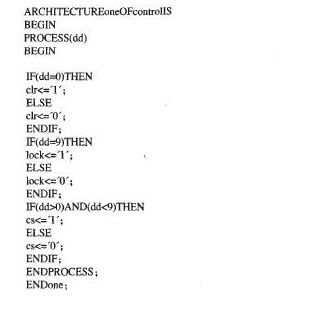

运用MAX+PIusII软件环境下树立VHDL言语输入文件规划操控信号发生电路,输入源程序如下:

①十进制计数电路

单元电路规划完结后,树立相应电路符号,在原理图输人办法下,将各单元电路符号按图1所示电路原理框图逻辑联系衔接,通过保存、编译,承认正确无误后能够说完结了CPLD内部电路的规划。

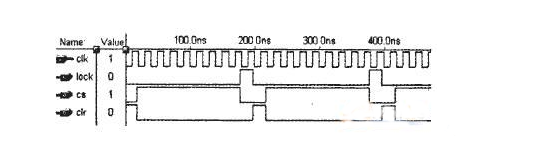

逻辑功用仿真:创立波形修正文件,保存为*.scf,得到仿真成果如图2。

通过器材挑选,管脚确定,编程下载等作业即可将规划项目下载至芯片,完结数字电路功用。

图2 电路的仿真成果

3. 完毕语

明显,比重用卡诺图化简再用相应集成片连线搭接电路.运用EDA技能规划数字电路更为灵敏便利,规划周期也大大减小。本规划选用自顶向下的规划办法,从体系整体功用动身分解出相应根本逻辑模块条理清晰,修正起来也更便利,能够说,EDA技能改变了传统数字体系规划办法、规划进程和规划观念,必将成为现代电子体系规划的中心。