导语

依据FPGA的通用CNN加快规划,能够大大缩短FPGA开发周期,支撑事务深度学习算法快速迭代;供给与GPU相媲美的核算功能,但具有相较于GPU数量级的延时优势,为事务构建最微弱的实时AI服务才能。

WHEN?深度学习异构核算现状

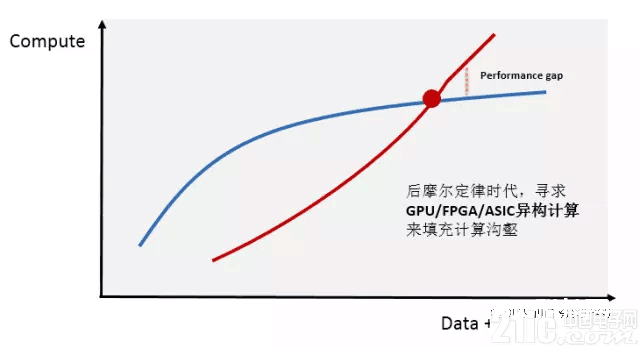

跟着互联网用户的快速增长,数据体量的急剧胀大,数据中心对核算的需求也在迅猛上涨。一起,人工智能、高功能数据剖析和金融剖析等核算密集型范畴的鼓起,对核算才能的需求已远远超出了传统CPU处理器的才能所及。

异构核算被认为是现阶段处理此核算沟壑的要害技术,现在 “CPU+GPU”以及“CPU+FPGA” 是最受业界重视的异构核算渠道。它们具有比传统CPU并行核算更高功率和更低推迟的核算功能优势。面临如此巨大的商场,科技职业很多企业投入了很多的资金和人力,异构编程的开发规范也在逐渐老练,而干流的云服务商更是在活跃布局。

WHY?通用CNN FPGA加快

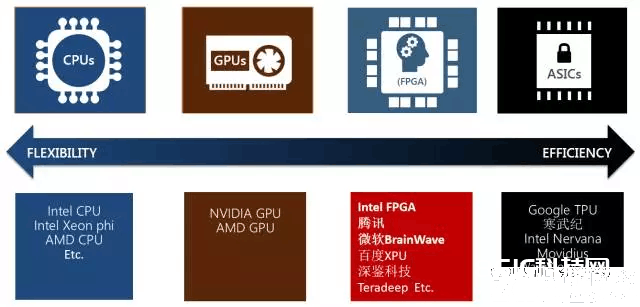

业界能够看到比如微软等巨子公司现已布置大批量的FPGA来做AI inference加快,FPGA相较于其他器材的优势是什么呢?

Flexibility:可编程性天然适配正在快速演进的ML算法

DNN、CNN、LSTM、MLP、reinforcement learning以及决策树等等

恣意精度动态支撑

模型紧缩、稀少网络、更快更好的网络

Performance:构建实时性AI服务才能

相较于GPU/CPU数量级进步的低延时猜测才能

相较于GPU/CPU数量级进步的单瓦特功能才能

Scale

板卡间高速互联IO

Intel CPU-FPGA构架

与此一起,FPGA的短板也非常的显着,FPGA运用HDL硬件描绘言语来进行开发,开发周期长,入门门槛高。以独自的经典模型如Alexnet以及Googlenet为例,针对一个模型进行定制的加快开发,往往需求数月的时刻。事务方以及FPGA加快团队需求统筹算法迭代以及适配FPGA硬件加快,非常苦楚。

一方面需求FPGA供给相较于CPU/GPU有满足竞争力的低延时高功能服务,一方面需求FPGA的开发周期跟上深度学习算法的迭代周期,依据这两点咱们规划开发了一款通用的CNN加快器。统筹干流模型算子的通用规划,以编译器发生指令的办法来驱动模型加快,能够短时刻内支撑模型切换;一起,关于新式的深度学习算法,在此通用根底版别进步行相关算子的快速开发迭代,模型加快开发时刻从之前的数月下降到现在的一到两周之内。

HOW?通用CNN FPGA架构

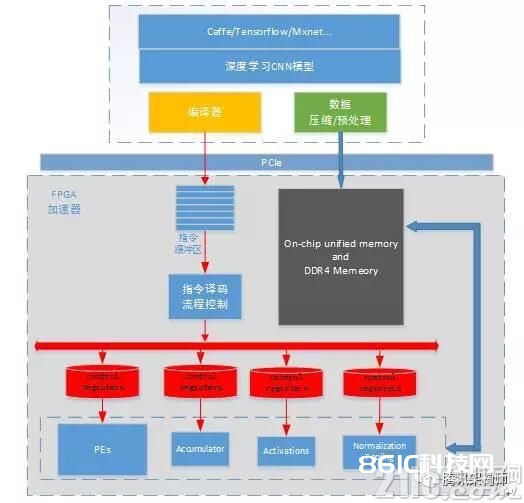

依据FPGA的通用CNN加快器全体结构如下,经过Caffe/Tensorflow/Mxnet等结构练习出来的CNN模型,经过编译器的一系列优化生成模型对应的指令;一起,图片数据和模型权重数据依照优化规矩进行预处理以及紧缩后经过PCIe下发到FPGA加快器中。FPGA加快器彻底依照指令缓冲区中的指令集驱动作业,加快器履行一遍完好指令缓冲区中的指令则完结一张图片深度模型的核算加快作业。每个功能模块各自相对独立,只对每一次独自的模块核算恳求担任。加快器与深度学习模型相抽离,各个layer的数据依靠以及前后履行联系均在指令会集进行操控。

简略而言,编译器的首要作业便是对模型结构进行剖析优化,然后生成FPGA高效履行的指令集。编译器优化的指导思想是:更高的MAC dsp核算功率以及更少的内存拜访需求。

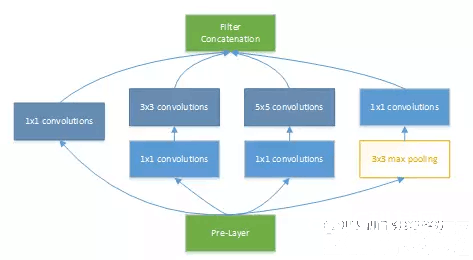

接下来咱们以Googlenet V1模型为例,对加快器的规划优化思路做简略的剖析。Inception v1的网络,将1×1、3×3、5×5的conv和3×3的pooling stack在一起,一方面增加了网络的width,另一方面增加了网络对规范的适应性。下图为模型中Inception的根本结构。

数据依靠联系剖析

此部分首要剖析发掘模型中可流水化以及可并行化的核算。流水化的规划能够进步加快器中的核算单元运用率,并行化的核算能够在同一时刻运用尽量多的核算单元。

关于流水,剖析部分包含数据从DDR加载到FPGA片上SRAM的操作与PE进行核算的流水,经过此项优化将内存拜访的时刻overlap;DSP核算整列的核算操控进程,确保DSP运用率的进步。

关于并行,需求要点剖析PE核算阵列与激活、pooling以及归一化等“后处理”模块之间的并行联系,怎么确认好数据依靠联系以及避免抵触是此处规划要害。在Inception中,能够从其网络结构中看到,branch a/b/c的1×1的卷积核算与branch d中的pooling是能够并行核算的,两者之间并不存在数据依靠联系。经过此处优化,3×3 max pooling layer的核算就能够被彻底overlap。

模型优化

在规划中首要考虑两个方面:寻觅模型结构优化以及支撑动态精度调整的定点化。

FPGA是支撑很多核算并行的器材,从模型结构上寻觅更高维度的并行性,关于核算功率以及削减内存拜访都非常有意义。在Inception V1中,咱们能够看到branch a branch b branch c的第一层1×1卷积层,其输入数据彻底共同,且卷积layer的stride以及pad均共同。那咱们是否能够在output feature map维度上对齐进行叠加?叠加后对input data的访存需求就下降到了本来的1/3。

另一方面,为了充分发挥FPGA硬件加快的特性,模型的Inference进程需求对模型进行定点化操作。在fpga中,int8的功能能够做到int16的2倍,可是为了使公司内以及腾讯云上的客户能够无感知的布置其练习的浮点模型,而不需求retrain int8模型来操控精度丢失,咱们采用了支撑动态精度调整的定点化int16计划。经过此种办法,用户练习好的模型能够直接经过编译器进行布置,而简直无任何精度丢失。

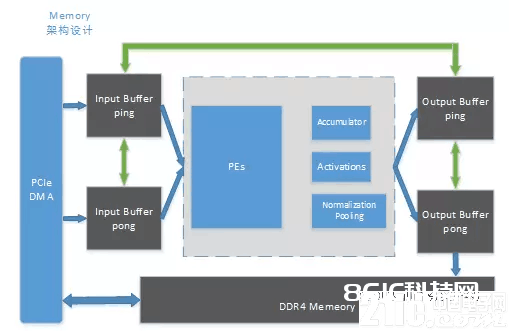

内存架构规划

带宽问题始终是核算机体系结构中限制功能的瓶颈之一,一起内存拜访直接影响加快器材功耗功率。

为了最大化的削减模型核算进程中的DDR访存,咱们规划了如下的内存架构:

Input buff以及output buffer ping-pong规划,最大化流水以及并行才能

支撑Input buff和output buffer本身之间的inner-copy操作

Input buff和output buffer之间的cross-copy操作

经过这种架构,关于大多数现在干流模型,加快器能够做到将中心数据悉数hold在FPGA片上,除了模型权重的加载外,中心无需耗费任何额定的内存操作。关于无法将中心层feature map彻底存储在片上的模型,咱们在规划上,在Channel维度上引入了slice分片的概念,在feature map维度上引入了part分片的概念。经过编译器将一次卷积或是poolingNorm操作进行合理的拆分,将DDR访存操作与FPGA加快核算进行流水化操作,在优先确保DSP核算功率的前提下尽量削减了DDR的访存需求。

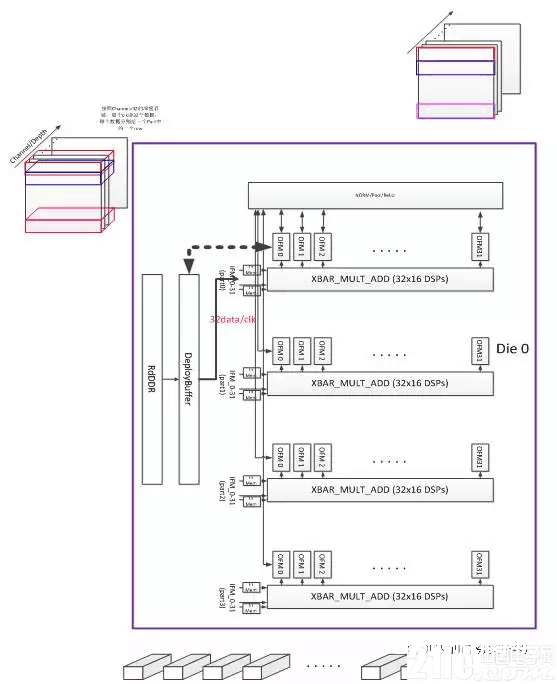

核算单元规划

依据FPGA的通用CNN加快器的中心是其核算单元,本加快器当时版别依据Xilinx Ku115芯片规划,PE核算单元由4096个作业在500MHz的MAC dsp中心构成,理论峰值核算才能4Tflops。其根本组织结构如下图所示。

KU115芯片由两个DIE对堆叠而成,加快器平行放置了两组处理单元PE。每个PE由4组32×16=512的MAC核算DSP中心组成的XBAR构成,规划的要害在于进步规划中的数据复用下降带宽,完结模型权重复用和各layer feature map的复用,进步核算功率。

运用场景及功能比照

当时深度学习干流运用GPU做深度学习中的Training进程,而线上Inference布置时需归纳考虑实时性、低本钱以及低功耗特性挑选加快渠道。按深度学习落地场景分类,广告引荐、语音辨认、图片/视频内容实时监测等归于实时性AI服务以及才智交通、智能音箱以及无人驾驶等终端实时低功耗的场景,FPGA相较于GPU能够为事务供给强有力的实时高功能的支撑。

关于运用者而言,渠道功能、开发周期以及易用性终究怎么呢?

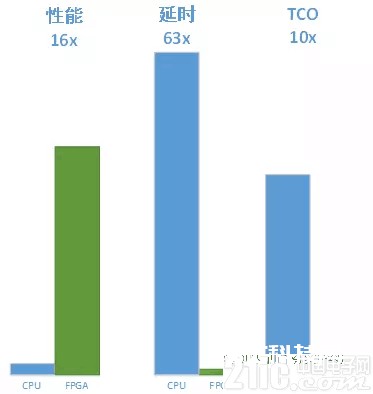

加快功能

以实践googlenet v1模型为例,CPU测验环境:2个6核CPU(E5-2620v3),64G内存。

将整机CPU打满,单张依据KU115的加快器相较于CPU功能进步16倍,单张图片检测延时从250ms下降到4ms,TCO本钱下降90%。

一起,FPGA猜测功能略强于Nvidia的GPU P4,但延时上有一个数量级的优化。

开发周期

通用的CNN FPGA加快架构,能够支撑事务快速迭代继续演进中的深度学习模型,包含Googlenet/VGG/Resnet/ShuffleNet/MobileNet等经典模型以及新的模型变种。

关于经典模型以及依据规范layer自研的算法变种,现有加快架构现已能够支撑,能够在一天内经过编译器完结模型对应指令集,完结布置上线。

关于自研的特别模型,例如不对称卷积算子和不对称pooling操作等,需求依据实践模型结构在本渠道进步行相关算子迭代开发,开发周期可缩短在一到两周之内进行支撑。

易用性

FPGA CNN加快器对底层加快进程进行封装,向上对加快渠道的事务方供给易用SDK。事务方调用简略的API函数即可完结加快操作,对事务本身逻辑简直无任何改动。

结语

依据FPGA的通用CNN加快规划,能够大大缩短FPGA开发周期,支撑事务深度学习算法快速迭代;供给与GPU相媲美的核算功能,但具有相较于GPU数量级的延时优势。通用的RNN/DNN渠道正在严重研制进程中,FPGA加快器为事务构建最微弱的实时AI服务才能。

在云端,2017年头,咱们在腾讯云首发了国内第一台FPGA公有云服务器,咱们将会逐渐把根底AI加快才能推出到公有云上。

AI异构加快的战场很大很精彩,为公司内及云上事务供给最优的处理计划是架平FPGA团队继续尽力的方向。

假如线上模型需求改动,只需调用模型初始化函数,将对应的模型指令集初始化FPGA即可,加快事务能够在几秒内进行切换。