作者 包海燕 孟欢 电子科技大学微电子与固体电子学院(四川 成都 610054)

包海燕(1993-),女,硕士生,研讨方向:数字IC规划;孟欢,女,硕士生,研讨方向:数字IC规划。

摘要:在数字体系互联规划中,高速串行I/O技能替代传统的并行I/O技能成为当时展开的趋势,与传统并行接口技能比较,串行计划供给了更大的带宽、更远的间隔、更低的本钱和更高的才能。以太网作为一种高速的串行传输办法,是当时最根本、最盛行的局域网组网技能,为了习惯各种新展开的事务如流视频等,其速率也在不断提高。GMII是规范的吉比特以太网接口,坐落MAC层和物理层之间。因而,能够依据FPGA渠道,完结GMII接口协议,完结数据在MAC和物理层间的通讯。

1 GMII接口协议简介

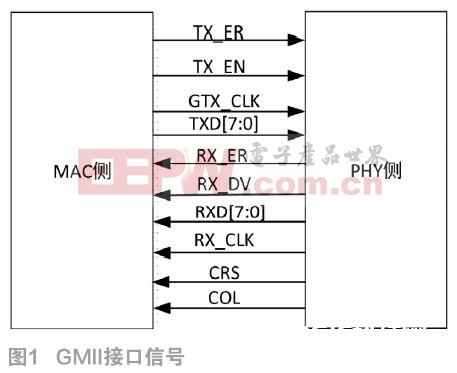

MII (Media Independent Interface(介质无关接口)或称为媒体独立接口,是IEEE-802.3界说的以太网行业规范。以太网中包含有一个数据接口以及一个MAC和PHY之间的办理接口[1]。数据接口包含两条独立的信道,这两条信道别离用于发送和接纳数据,它们都单独具有数据信号、时钟信号以及操控信号。GMII是千兆以太网的MII的接口,该数据接口一共需求16个信号,接口信号如图1所示。

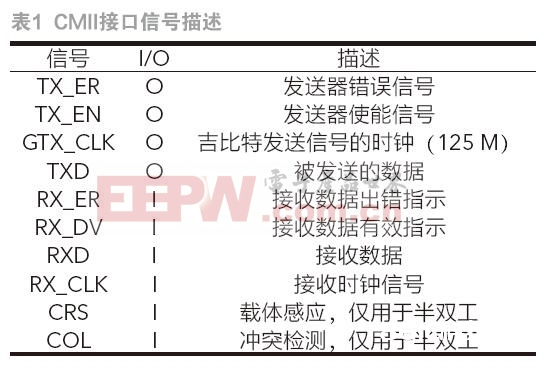

GMII选用8位接口数据,作业时钟125 MHz,因而传输速率可达1000 Mbps。一同兼容MII所规则的10/100 Mbps作业办法。MII接口首要分为四个部分,别离是MAC层到物理层的发送数据接口、物理层到MAC层的接纳数据接口、物理层到MAC层的状况指示接口、MAC层和物理层的操控和状况信息接口(MDIO)。具体的信号阐明如表1所示。

2 规划计划

Xilinx供给的千兆以太网开发套件为Virtex-5 ML505/ML506开发板,该开发板支撑10/100 M、1/10 G以太网,是学习和研制高速衔接设备的抱负渠道。Xilinx供给了可参数化的10/1 Gbps以太网物理层操控器功用的LogiCORE解决计划[2]。该核规划用来同最新的Virtex-5、Virtex-4和Virtex-II Pro渠道FPGA一同作业,并能够无缝集成到Xilinx规划流程中。

以太网体系的两个首要模块是媒体接入操控(MAC)和物理层PHY,MAC由数据拆装和媒体拜访办理两个模块组成,完结数据帧的封装、解封、发送和接纳功用。PHY对发送的数据依照物理层的编码规则将数据编码,再进行数模转化变成模拟信号把数据送出去。接纳数据则与之相反。

2.1 电路架构

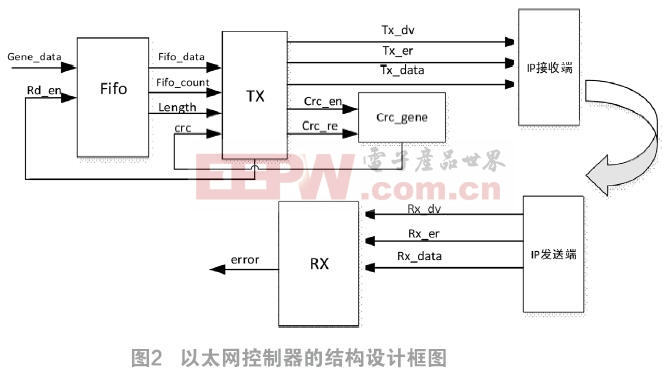

该以太网操控器首要进行MAC子层、MAC层与上层协议的接口以及MAC层与PHY接口的GMII的FPGA规划,整体结构框图如图2所示。整个体系分为待发送数据的发生模块、发送模块、CRC编码生成模块、物理层编解码模块、接纳及校验模块、GMII办理模块等部分。发送模块和接纳模块首要供给MAC帧的发送和接纳功用,其首要操作有MAC帧的封装与解包以及过错检测,它直接供给了到外部物理层芯片的并行数据接口[3]。在完结中物理层处理直接运用商用的千兆PHY芯片,在仿真进程中运用物理层IP_CORE来完结,所以本文重要重视在MAC操控器的开发上。

2.2 MAC协议介绍

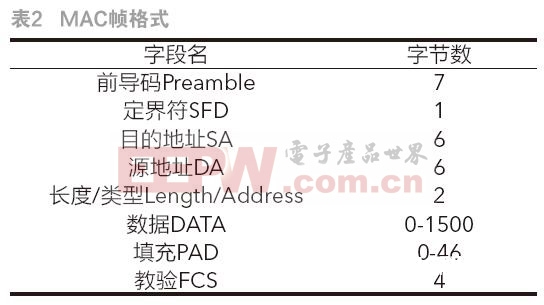

MAC操控模块是由数据拆装和媒体拜访办理两个模块组成,完结数据帧的封装、解封、发送和接纳功用。帧格局如表2所示。

前导码的作用是让物理层信号与接纳帧时序到达永久同步。长度类型标明后边发送数据的长度,当实践数据的长度不行时,需求补0填充。类型0X0800代表IP协议数据,16进制0x809b代表Appletalk协议数据等,本文发送的是IP协议数据。帧完毕的数据是依据CRC电路核算生成的校验码。

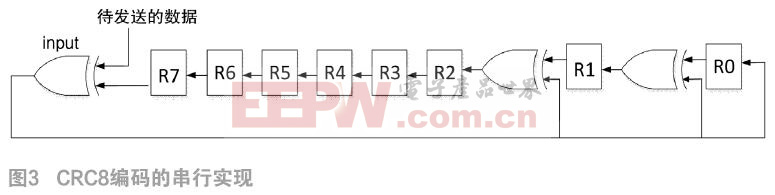

2.3 以太网的FCS处理

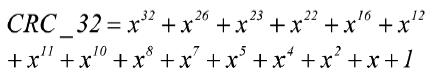

校验位的FCS即为循环冗余码CRC,它的编码具体进程是,依据数据流M的长度和特性,挑选长度为n次的特征多项式,在数据流M之后增加n个0,作为被除数除以由特征多项式构成的(n+1)bit的二进制数列P,得到商Q以及除数R,除数R为n bit,将R作为冗余码增加在M之后发送出去。Crc8编码的串行算法完结电路如图3所示[4]:

编码前先将一切寄存器初始化,之后将待发送的信息序列顺次在input端输入编码器,信息序列悉数输入之后,寄存器中的值就是所要求的余数,即CRC校验码。本文运用的是crc32多项式,多项式的表达式如下所示,需求编码的数据段从意图字段开端到数据字段完毕,运用相同的相似的电路,即可运用verilog完结冗余码编码。

3 电路完结与仿真

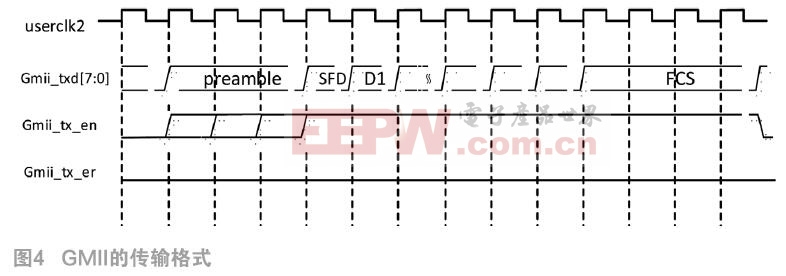

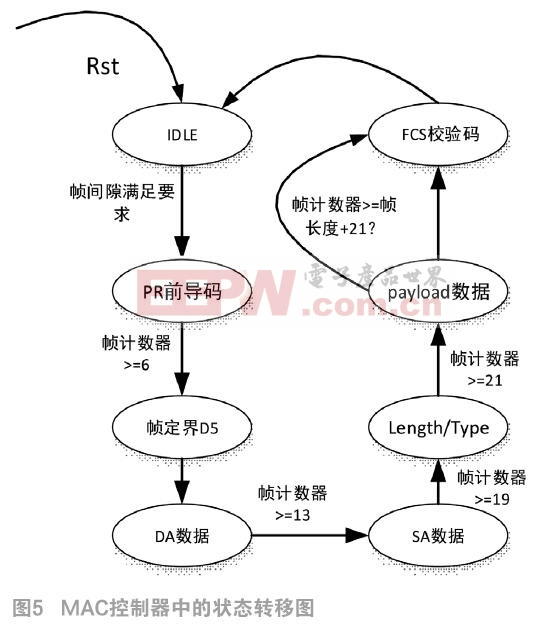

3.1 MAC发送端-数据成帧

以太网的发送办法是依照一个帧一个帧来发送的,网络设备和组件在接纳一个帧今后,需求一段时刻短的时刻来康复并为接纳下一帧做准备。帧空隙是帧与帧之间需求的时刻余量,以太网的最小帧空隙为96 bit(12 byte)。所以在开端发送时,要判别是否满意帧空隙。依据GMII接口的传输时序如图4,规划图5所示的状况机,经过对每个状况中,对字节进行计数完结状况的跳转。

在数据传输进程中,MAC发送模块将上层协议需求发送的数据经过以太网协议进行封装将数据发送给PHY层,发送模块还可将从主机接纳到的帧头以及帧尾标志信号,与主机接口从外部存储单元获取的发送数据依照规范协议进行封装,将数据以8位数据宽度的格局在信道空闲时发送给PHY层,再经过PHY芯片将数据进行数模转化发送到网络中去。

在物理层部分,运用ISE渠道生成Etherent 1000 BASE-X PCS/PMA IP CORE来接纳MAC层的数据,该核支撑内部或外部GMII,可完结与MAC或定制逻辑的链接。IP核内的首要组成部分为PMA和PCS,其间PMA为物理层的前言层,PCS为物理层编码模块,能够进行8 B/10 B编解码,64 B/66 B编解码,COMMA字符检测,将接纳的数据对齐到适宜的字鸿沟,伪随机序列的生成和检测,时钟修正和通道绑定等[5]。

3.2 MAC接纳端-数据提取

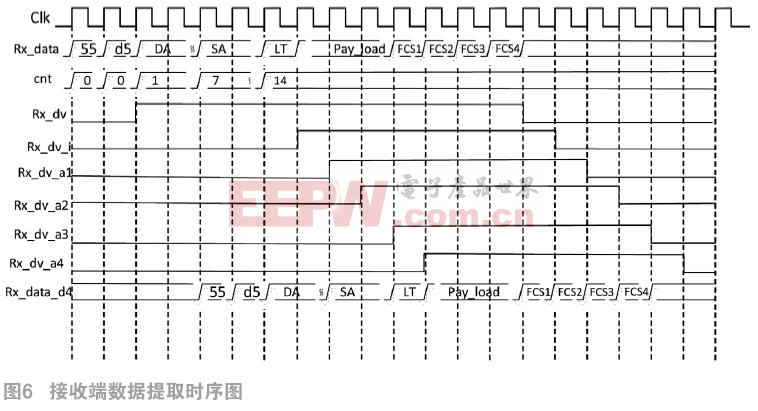

MAC端接纳到传回的数据后,需求对接纳到的数据进行检测,首要提取出pay_load数据和冗余检验码crc_cmp。当发送数据包的长度不确定时,不能经过计数器来提取对应的数据和校验码,可行的操作如图6的时序图所示。

在接纳端假如检测到前导码的第一个字节55时,计数器开端计数,当计数到14时,下一个时钟,就是发送来的实践数据,发生Rx_dv_i信号,直到接纳到四个字节的校验码时拉低,并将Rx_dv_i推迟四拍得到Rx_dv_a4信号,一同将Rx_data也推迟四拍,则在Rx_dv为高电平且Rx_dv_a4为高电平,取Rx_data_d4上的数据,即为pay_load数据,在Rx_dv为低电平,Rx_dv_a3为高电平时,Rx_data_a4为校验码。选用这种计划,在不确发送数据的个数情况下,能够别离提取出pay_load数据和fcs校验码数据。

3.3 电路功用仿真

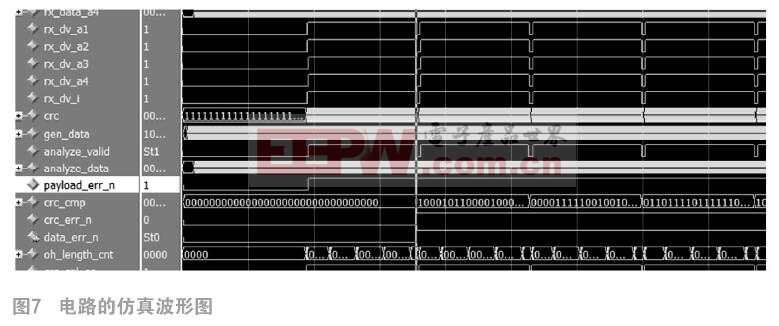

提取到相应的数据后,先将发送端的数据和接纳到的数据进行比较,假如不同,发生data_error信号的低电平,指示犯错,一同将接纳到的数据送入CRC编码电路,来发生校验码rx_crc,将发送端的校验码crc_cmp与rx_crc进行比较,假如不同,发生crc_error的低电平信号。终究电路的过错指示信号error由data_error和crc_error相与发生。

规划完结今后,运用modelsim软件对电路进行了仿真,仿真波形如图7所示:能够看到三个过错标志信号error,在开端作业后均为高电平,标明该电路成功完结了在MAC和PHY之间的数据传输。

4 定论

高速串行传输技能是FPGA未来的三大应用领域之一,本文从以太网传输的整体结构和根本协议动身,规划了千兆以太网传输体系的计划,以MAC+PHY为中心,完结了网络架构中物理层和数据链路层的根本功用。经过仿真验证了数据在数据链路层和物理层之间准确无误的传输,稳定性好,灵活性高,本体系还能够用来传输图画和大数据信息。

参考文献:

[1]曹云鹏.以太网MAC层协议研讨与FPGA完结[D].兰州:兰州大学,2011.

[2]王春华.Xilinx可编程逻辑器件规划与开发(根底篇).[M]北京:人民邮电出版社,2011.

[3]刘民.嵌入式千兆以太网络图画传输体系规划[D].大连:大连理工大学,2012.

[4]陈玉泉.一种并行CRC算法的完结办法[P].厦门:厦门大学,2005.

[5]王长清.依据FPGA的千兆以太网通讯板卡的规划与完结[D].河南:河南师范学报,2011.

本文来源于《电子产品世界》2018年第6期第67页,欢迎您写论文时引证,并注明出处。