跟着社会的开展,科学技能也在不断的前进。特别是计算机工业,能够说是一日千里,移位存放器作为计算机的一个重要部件,从从前的只能做简略的左移或右移功用的存放器到现在广泛运用的具有存放代码、完成数据的串行-并行转化、数据运算和数据处理功用的移位存放器。移位存放器正在向着功用强,体积小,重量轻等方向不断开展。

近年来,集成电路和计算机运用得到了高速开展,现代电子规划技能已迈入一个簇新的阶段,具体表现在:

(1)电子器材及其技能的开展将更多地趋向于为EDA服务;

(2)硬件电路与软件规划进程已高度浸透;

(3)电子规划技能将归结为愈加标准、标准的EDA东西和硬件描绘言语HDL的运用;

(4)数字体系的芯片化完成手法已成干流。

因而运用计算机和大规模杂乱可编程逻辑器材进行现代电子体系规划已成为电子工程类技能人员必不可少的根本技能之一。

跟着集成电路集成度的不断添加和作业速度的进步,功耗急剧添加。早在7年前,Alpha处理器21164的功耗已高达50W.这给集成电路的散热、封装和便携设备的运用等都带来极大的困难。因而,怎么下降功耗成为规划集成电路时要考虑的一个重要问题。

在CMOS电路的功耗中决议性的一项来自于电路中对给定结点的充放电与此相应的功耗可由下式标明:

P=0.5CL·V2DD·fCLK·ESW

式中,CL为该结点的物理电容,VDD为电源电压,fCLK为时钟频率,ESW(称为开关活动性)是每个时钟周期1?fCLK中的均匀输出跳变数。

在一个体系中时序电路常是功耗的首要贡献者,由于时序电路的输入信号之一便是时钟,而它正是仅有的一直在跳变的信号。此外,时钟信号的负荷总是最高的。为散布时钟以及操控住时钟偏移,就需求构建一个含有时钟缓冲器的遍及体系的时钟网络(一般称为时钟树)。一切这些均添加了时钟网络的结点电容的总和。近年来的研讨标明,在数字计算机中时钟信号耗费的功耗占了体系功耗的很大份额(15%~45%)。因而,经过削减时钟功耗将能够大幅度下降电路的总功耗。

在对触发器的内部结构的剖析中发现时钟信号有一半跳变是冗余的,仅有另一半跳变才引起触发器的状况改动。因而,当时国际上对一种新式的双边缘触发器提出了研讨。所谓双边缘触发器是指对时钟上下跳变灵敏的一种新式触发器。运用该类触发器,时钟信号的频率能够下降一半就能坚持本来的作业速度,然后使得对双边缘触发器的研讨成为低功耗规划的一个研讨热门。

注意到触发器是存储单个数字信号的存储单元,而用触发器串接而成的移位存放器能够认为是一种存储多位数字信号的存储元件。因而对双边缘触发器的研讨应可推行到对移位存放器的研讨中来。本文将从双边缘触发器的规划思维动身对双边缘移位存放器的规划思维、作业原理、低功耗特色及运用等方面打开深入研讨,以达成对该一新式低功耗器材的研讨完整性。

双边缘移位存放器的规划

锁存器(latch)是构成触发器的根本单元。锁存器的输入时钟信号clk用于将锁存器置于存贮状况或输入状况。若用D、Q和Q′别离来标明锁存器的输入信号、现态及次态,则高电平输入与低电平输入等两种锁存器的状况方程可标明如下:

Q′=D·clk+Q·clk,(1)

Q′=D·clk+Q·clk.(2)

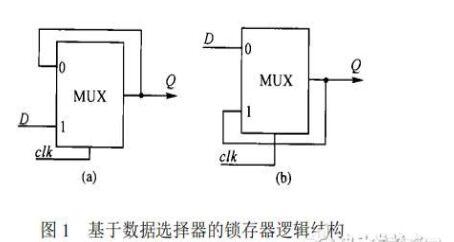

式(1)标明锁存器在clk=1时输入数据,clk=0时存贮数据;而相应式(2)为clk=0时输入数据,clk=1时存贮数据。图1(a)、(b)别离示出了依据式(1)、(2)运用数据挑选器MUX完成的时钟高电平时输入与低电平时输入的D型锁存器逻辑结构。

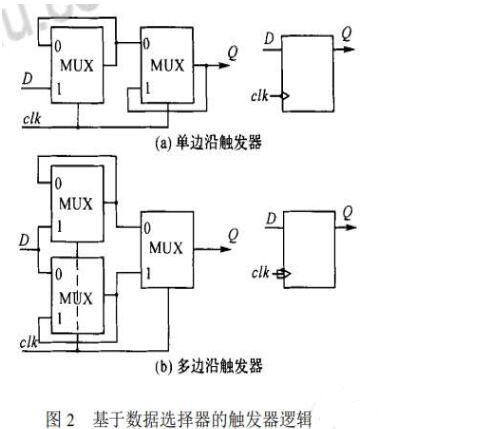

以图1(a)所示的时钟高电平时输入的D型锁存器为例,它的作业特色为在clk=0时输入信号无法影响锁存器的存贮状况,而当clk=1时,输入信号就能影响锁存器的存贮状况。这样,在clk=1期间输入信号的屡次改动将会导致锁存器产生屡次状况转化。为了完成一次状况转化,能够要求它的输入信号在clk=1时坚持不变。这一要求暗示了该锁存器的输入信号在clk=1时应处于一种存贮状况,因而也就需求别的一个反相操控的锁存器,由此便导出了传统的主从触发结构。图2(a)即为用图1(a)、(b)中两种用数据挑选器MUX组成的锁存器串联而构成的单边缘主从触发器。其间前级D型锁存器为主锁存器,后级D型锁存器为从锁存器。当clk=1时主锁存器处于输入状况,而从锁存器处于存贮状况;当clk=0时主锁存器处于存贮状况,而从锁存器处于输入状况,Q转化为Q′,即该主从触发器仅在clk下跳时进行状况转化,因而称为单边缘触发器(SETFF)。

一次状况转化的要求也能够从触发器的输出来考虑。只需挑选处于输入状况的锁存器与输出阻隔,则该锁存器即便在输入状况下产生屡次状况转化也不会影响输出状况。这暗示了能够把串联的主从触发器改成并联的方式。两个锁存器在时钟clk的效果下替换处于输入状况及存贮状况,而最终能够用另一个数据挑选器MUX使二者中处于存贮状况的锁存器接通输出端,如图2(b)所示。这样,该触发器在clk=0、1时都能够接纳输入信号,触发器的状况在时钟脉冲的上升沿和下降沿均能够改动,然后完成了时钟信号的双边缘触发,图2(b)中的图形符号已在时钟输入端标志了这一特性。

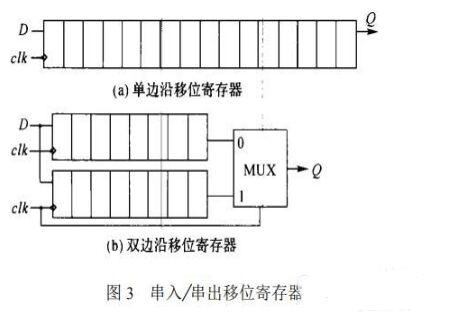

学习以上双边缘触发器的规划思维,能够规划出双边缘移位存放器。下面以规划16位的移位存放器为例进行评论。传统的移位存放器规划以16个单边缘触发器串行级联构成,如图3(a)所示。该移位存放器要存储或许输出162bit的数据需求有16个时钟周期,在此期间各个触发器均要遭到32个时钟跳变。假如将16个单边缘触发器分红两组,每组由8个反相触发的单边缘触发器串行级联构成单边缘移位存放器,再将两组触发器并联就构成了双边缘移位存放器。两组触发器在时钟的效果下替换处于输入状况及存储状况,而最终能够用一个数据挑选器MUX使处于存储状况的触发器组接通输出端,如图3(b)所示。这样,162bit数据顺次在一个时钟周期内别离由上下二组触发器轮番接纳、存储并输出到移位存放器的输出端,在此期间每个触发器只接纳到16次时钟信号的触发(8个时钟周期)。因而,假如坚持时钟频率不变,则移位存放器处理的数据流量在能耗不变的前提下添加近1倍;别的,假如时钟频率下降一半,则能在坚持不变的数据流量的一起下降移位存放器的功耗。

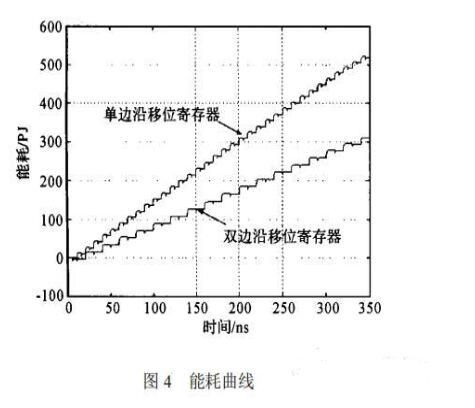

图4所示是在相同的数据流量的状况下单边缘移位存放器和双边缘移位存放器的能耗曲线。由图可知,双边缘移位存放器比单边缘移位存放器的功耗下降了38.5%.能够发现,尽管双边缘移位存放器比单边缘移位存放器添加了一个MUX,可是由于开关频率折半所导致的功耗下降仍是首要的。

运用双边缘移位存放器的时序电路规划

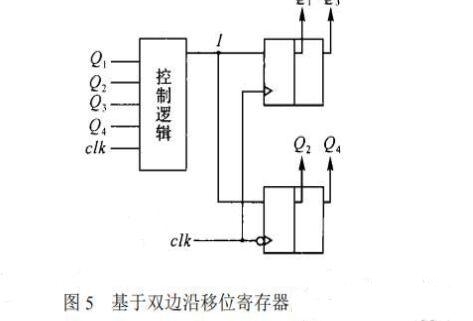

以上规划的双边缘移位存放器能够运用于各种时序体系,如数据的移位存放和规划移位型计数器。在数据流量不变的状况下,时钟频率能够折半。以下将以图5所示的2&TImes;2位双边缘移位存放器为例,评论选用该移位存放器规划移位计数器的规划进程及规划特色。

如图5所示,2&TImes;2位双边缘移位存放器的操控输入端接受操控逻辑I的输出,操控逻辑I的输入为状况变量Q1、Q2、Q3、Q4.这样只须规划操控逻辑I,就能够规划出双边缘移位计数器,故其规划比较简略。作者发现,将时钟信号clk作为状况变量能够规划出更多状况数的计数器并且使电路结构简略。由Q1、Q2、Q3、Q4、clk五位状况变量,能够规划出最大状况数为32的移位计数器。

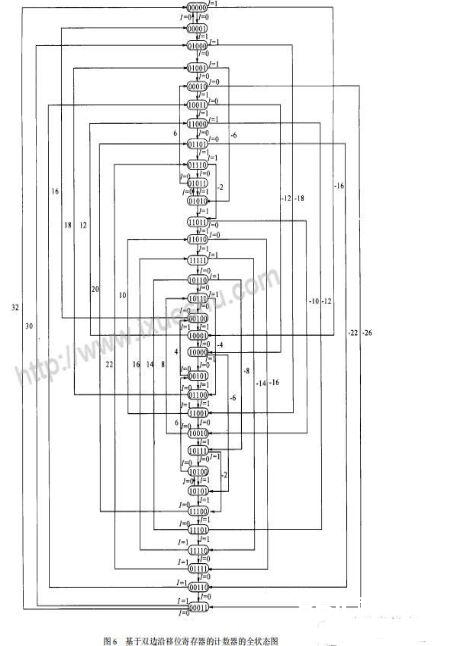

由于各触发器之间有必要坚持移位的联系,移位计数器状况搬迁遭到限制。这便是说,对任何一个现在状况来说,它只需两种或许的下一状况,由于只需首位触发器才有两种或许的取值供挑选,而其他各位已由现在状况所决议。由于状况搬迁遭到限制,能够将一个移位存放器的全状况图画出来,以便用它来挑选各种长度的移位计数器所运用的编码。五位移位计数器的全状况图如图6所示。图中I为首位触发器的输入,它只需两种取值0或1.在图6中,作者以一个最大计数环作为骨干,给出了全状况图。为了运用上的便利,在全状况图左面的回来线上用十进制数标明它所跨的状况数(包含起止状况),在全状况图右边的分枝线上用负数标明它所越过的状况数(不包含起止状况)。

独自运用回来线,能够取得某种循环长度的状况图及其编码。例如4号回来线指出,若开始状况为00100,在I为1时搬迁到状况10001,又在I为0时从10001迁到10000,再在I为0时迁到00101,最终在I为0时回来到开始状况00100.仅用回来线决议的循环长度有4、6、8、10、12、14、16、18、20、22、30、32十二种。

假如回来线和分枝线配合起来运用,能够取得从2到32的任何一种偶数循环长度。规划原则是:使一切选中的回来线和分枝线上的数字的代数和,等于所需的循环长度。例如,要求循环长度为28的计划有3种:

计划一:32-4=28,(32号回来线和-4号分枝线)。

编码为00000,00001,01000,01001,00010,10011,11000,01101,01110,01011,01010,11011,11010,11111,10110,00111,01100,11001,10010,10111,10100,10101,11100,11101,11110,01111,00110,00011

计划二:30-2=28,(30号回来线和图6中上部的-2号分枝线)

编码为01000,01001,00010,10011,11000,01101,01110,11011,11010,11111,10110,00111,00100,10001,10000,00101,01100,11001,10010,10111,10100,10101,11100,11101,11110,01111,00110,00011

计划三:30-2=28,(30号回来线和图6中下部的-2号分枝线)

编码为01000,01001,00010,10011,11000,01101,01110,01011,01010,11011,11010,11111,10110,00111,00100,10001,10000,00101,01100,11001,10010,10111,11100,11101,11110,01111,00110,00011

运用全状况图来规划移位计数器是非常便利的,只需给定循环长度后,就能从全状况图中查出所规划的计数器的状况图,有了状况图便能规划出电路来。并且由于关于给定的循环长度,其规划计划有很多种,所以能够归纳考虑各种规划计划,找到首级触发器的操控逻辑I最简略的一种计划,然后到达电路的最简。

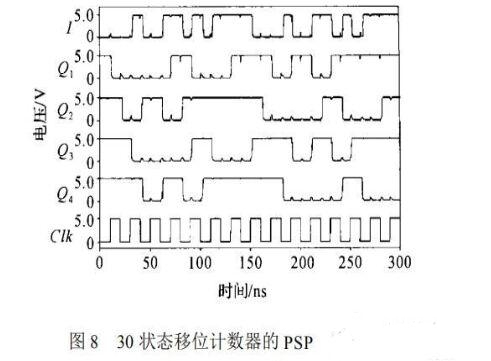

以规划30状况移位计数器为例,由图6能够看出循环长度为30的组成计划至少有3种,而选用独自运用30号回来线的计划,操控逻辑I最简略。由30号回来线构成的状况图能够得到操控逻辑I的卡诺图如图7所示,再由卡诺图能够得到操控逻辑I的表达式:I=Q3+Q4.因而,在图5中当操控逻辑部分的电路为Q3+Q4时,就得到了30状况移位计数器。作者对规划出的30状况移位计数器进行PSP%&&&&&%E模仿,其作业波形如图8所示。图中,开始状况为11110,间断状况为11101.其逻辑功用到达了规划的要求。

本文为了有用运用导致无效功耗的时钟信号一半的冗余跳变,学习双边缘触发器的规划思维,推演了双边缘移位存放器的规划,并进一步探讨了其在双边缘移位计数器中的运用。经过PSP%&&&&&%E模仿程序比较单边缘移位存放器和双边缘移位存放器,作者发现所规划出的双边缘移位存放器具有正确的逻辑功用,并且在时钟信号频率折半后,仍能坚持数据传输率不变,到达了下降功耗的意图。本文对30状况移位计数器的规划中发现,如运用双边缘移位存放器,则能够只用4个触发器来完成,这一节约一个触发器的成果与文献[9]的成果相吻合。本文对双边缘移位存放器的研讨实际上是对双边缘触发器的进一步研讨,达成了研讨的完整性。