本文规划依据FPGA 芯片EP3C16Q240C8N 的片上可编程体系,该体系可用于完结IFFT运算和接口模块,运用可嵌入到此FPGA 芯片的NiosII 软核处理器来完结数据传输和操控。功用电路中的ADI 的数字上变频芯片AD9957 和可控增益芯片AD8369 用于完结DAB 基带信号的上变频和信号扩大。这套DAB 发射机电路板尺度为100cm*160cm,经过测验,能很好的完结发射,具有较高的可靠性。

DAB 发射机是数字音频播送重要组成部分。DAB 技能是欧洲尤里卡项目之一,现在现已十分老练.DAB 选用先进的数字技能,正交分频复用技能(OFDM),能以极低的数据传输率及失真下传送CD 质量之立体声节目,可解决传统模仿播送接纳不良及搅扰问题.DAB 发射体系包含信源编码。信道编码。 时刻交错。频率交错.OFDM 调制和射频部分。射频部分包含上变频和增益扩大,用来把基带信号搬移到发射频率上并将其扩大。

FPGA 技能不断进步,本钱和功耗不断下降的一起功用和容量在大幅上升,FPGA 也替代MCU 越来越多的嵌入到体系中去。为了便于体系集成,本文规划FPGA 体系嵌入到DAB 发射体系中,使得开发变得便利灵敏,一起也降低了本钱。

FPGA 的SOPC 体系构成

该体系硬件框图如图1所示。体系中FPGA选用ALTERA 公司的CycloneIII 系列芯片EP3C16Q240C8N.FPGA 中的NiosII 软核处理器完结数据的操控和指令传送,还能够在FPGA 上完结OFDM 调制。装备芯片选用EPCS16,片外扩展存储器为IS42S16100-7T.框图中,功用电路是用来完结DAB 发射功用的,它包含数字上变频(其间现已包含A/D 和D/A 转化)。信号扩大.USB 传输等。

依据DAB 发射体系规划能够得出体系中各个单元所需的资源:逻辑单元。寄存器。引脚。内存。乘法器单元。锁相环分别为8839.4719.104.202752bits.6和1.这款芯片为QPFP 封装。

装备电路

FPGA 芯片按装备速度快慢依次为:

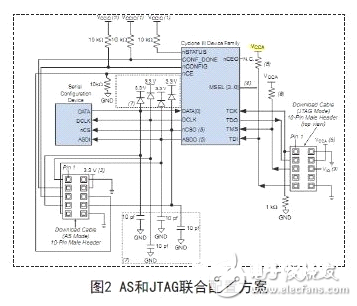

AcTIve parallel(AP)形式.Fast passiveparallel(FPP)形式.AcTIve serial(AS)形式.Passive serial(PS)形式。别的还有用于调试的Joint Test AcTIon Group(JTAG)形式。本文FPGA 一起装备AS 形式和JTAG 形式。依据cycloneIII 的数据手册,装备方案由MSEL 引脚决议。当运用AS 和JTAG 两种方法时,MSEL[3:0]为“010”。如图2所示为ATERA 给出的AS 和JTAG 装备电路。AS

AS 形式是指FPGA 的EPCS 操控器宣布读取数据的信号,从而把串行FLASH(EPCS系列芯片)的数据读入FPGA 中,完结对FPGA 的编程。装备数据经过FPGA 的DATA0引脚送入,数据被同步在DCLK 输入上,1个时钟周期传送1位数据。 本文中选取的装备芯片EPCS16SI8,有16Mbits 的存储空间,能够支撑DCLK 时钟作业在20MHz 和40MHz.JTAG 接口是一个业界标准接口,首要用于芯片测验等功用.ALTERA 的FPGA 基本上都能够支撑JTAG 指令来装备FPGA 的方法,并且JTAG 装备方法比其他任何方法优先级高.JTAG 形式是将装备数据存储在SRAM,掉电后需从头下载。它与FPGA 的接口有4个必需的信号TDI,TDO,TMS 和TCK 以及1个可选信号TRST 构成。