跟着社会经济的开展和日子物质水平的进步,人们关于精神世界的寻求也越来越高。该规划理念源于进步人们的日子夸姣指数。在传统意义上,人们往往用冲印出来的相片来记载日子中的夸姣瞬间。可是随同电子职业的开展,包含数码相机,高像素智能内的许多电子产品大行其道,足以用数码方法将其代替。据统计,世界上那个70%以上相片都是数码相片,年青一族更是喜爱以数码方法记载他们的日子,而且共享在网络上。数码相框一起还能够将静态图片提升为动态的相册,携带便当,贮存时刻久远,满意于人们的需求,一起也会是一种节约型,环保低碳型的设想。

FPGA 作业原理

一个典型的FPGA 是有几个部分构成的,首要是逻辑块(LogicBlock),Altera 公司将其称之为逻辑阵列快(LAB)Xilinx 公司将其称为可装备逻辑块(CLB)。LAB 由称之为LE(Logic Element)的根本单元构成,CLB 由称之为LC(Logic Cell)的根本单元构成。这些便是FPGA 的逻辑资源,还有一部分是散落在各个逻辑块之间地内部连线,它们好比是PCB 板上的导线,将FPGA 内部地各个逻辑相衔接,起点和结尾都是IOB(I/O Block)。另一部分便是IOB 了,IOB 是FPGA的外部物理接口,相似IC 的各引脚,当然这儿是依据用户需求自己能够恣意界说的。现在的FPGA 的IOB 现已很强壮, 从根本的LVTTL/LVCOMS 接口到PCI/LVDS/RSDS 乃至各式各样的差分接口,FPGA内部的I/O 实际上是分组的,可是每一组都能够灵敏装备,改动上拉下拉电阻,调停驱动电流巨细,兼容5V,3.3V,2.5V,1.8V 乃至1.5V,能够满意不同的电器特性,不同的I/O 接口物理特性以及外部硬件电路对输入输出信号的各种匹配要求。现在I/O 能够到达的频率也愈来愈高,经过特定的技能数据读取速率乃至能够到达2Gbps 现在越来越多的工程师喜爱FPGA,强壮的I/O 特性也是一种原因吧。

图2-1 典型的FPGA内部结构图

I/O 兼容恐怕是大势所趋。规划IOB 的概念和技能还有许多,这儿不做介绍了。还有一部分便是FPGA 内部的功用模块,是制作商依据实际需求放置在FPGA 内部的。比方数字时钟办理模块即DCM,Xilinx 公司的FPGA 全都具有这种功用。比方相位环路确定。PLL 需求一个外部时钟输入(晶振),经过内部处理后(包含分频和倍频)能够供给在频率和相位上都比较稳定的必定范围内的时钟。还有不得不提的内部不占用逻辑资源的块RAM。RAM 块可用作为单口RAM、双口RAM、内容地址存储器以及FIFO(first in first out)等常用存储器乃至ROM,移位寄存器。这关于小量数据缓存很有用,强化了FPGA的运用性。在挑选FPGA 时,芯片内部块RAM 的资源多少也是衡量的一个重要因素。独自块RAM 的容量为18kbit 宽为18Bit、深度为1024,能够依据实际需求改动其位宽和深度,但有两点束缚:首要便是修改后块RAM 的容量(位宽深度)不能大于单片块RAM 容量;而且位宽最大不能超过36Bit,能够将多片块RAM 联起来构成内存更大的RAM,此刻只受限于芯片内块RAM 的数量,而不再受上面两条准则束缚。不过在Quartus 中,具体操作起来很便当。还有底层内嵌功用单元包含内嵌专用硬核如乘法器等。它关于数字信号的运算处理供给极大的便当。

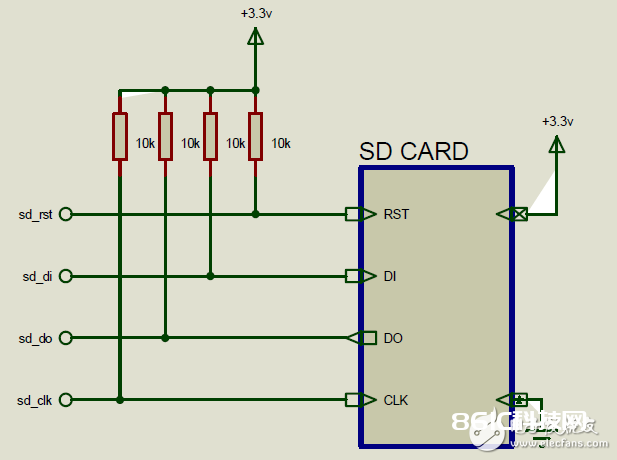

SPI 接口操控电路

图4-1 SPI形式衔接图

该工程模块的SPI 接口四条信号线别离定spi_cs_n,spi_clk,spi_miso 和spi_mosi。其间spi_cs_n 是数据操控使能信号,当要对芯片进行操作时,此信号低电平有用。也便是说在同一条主线上能够衔接多个SPI。spi_clk是SPI 同步时钟信号,数据信号在该时钟的操控下进行逐位传输。spi_miso 和spi_mosi 是主从机进行通讯的数据信号,spi_miso即主机的输入或许说是从机的输出spi_mosi 即主机的输出或许说是从机的输入。

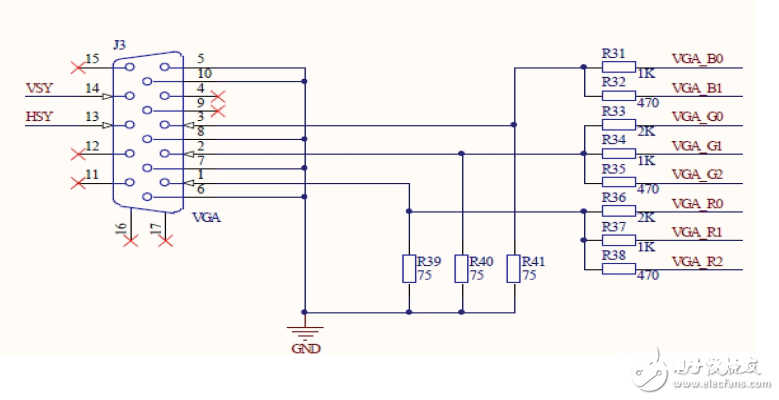

VGA 显现驱动模块

规范VGA 一共有15 针,真实用到的接口不多,只要5 个,场同步信号和列同步信号是为了让VGA 接纳部分知道过来的数据是对应哪一行哪那一列。还有三原色信号,本课题硬件三原色信号经过衔接不同的电阻后直接与I/O 接口相连(可理解为简易的DA 转化),这样就能够显现256 色了。内部VGA 与FPGA 接口如图7-1 所示。

图7-1 VGA 内部简化DA

本站网技能修改点评剖析:

FPGA 器材运用是继单片机之后,当今地嵌入式系统开发运用中最最抢手的关键技能之一,而且跟着制作工艺水平的不断进步,本钱的不断下降,FPGA 乃至大有代替专用AS%&&&&&% 的趋势。FPGA 运用Verilog 或VHDL 等硬件描绘言语编程。系统工程一切功用悉数运用FPGA 来完结,内容包含SD 卡的读取操控,图片解码,VGA 驱动显现等等,选用的是SF—EP1开发板,该板FPGA 运用EP1C3T144C8,装备PLL 电源电路,SD 接口,1 个256 色的VGA 通用接口,SDRAM 等。支撑AS 及JTAG 装备方法,软件渠道运用Quartus Ⅱ 9.1,然后完结10 幅800*600 的BMP 图片循环显现。

我们如有问题,欢迎在评论处评论。

——本站网收拾,转载请注明出处!

—————————————-

以衔接器材料集锦——观察衔接器现状与趋势!