本文以TLV3501滞回比较器电路规划为示例,简略为您解说滞回比较器电路规划的办法与思路,期望对您规划比较器电路有所协助。

什么是滞回比较器?

滞回比较器:又称施密特触发器,其抗搅扰能力强,假如输入电压遭到 搅扰或噪声的影响,在门限电平上下动摇,而输出电压不会在高、低两个电平间重复的跳动。

滞回比较器电路图:

滞回比较器电路规划理论剖析及核算:

输入电压UI经电阻R1加在集成运放的反向输入端,参阅电压UREF经电阻R2接在同向输入端,此外从输入端经过电阻RF引回同向输入端。电阻R和背靠背稳压管VDZ的作用是限幅,将输出电压的起伏约束在±UZ。

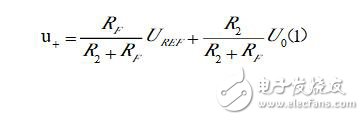

使用叠加原理可求得同向输入端的电位为:

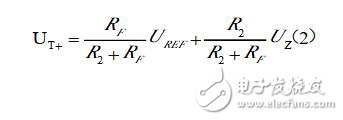

若本来U0=+UZ,当UI逐步增大时,使U0从+UZ跳变为-UZ所需的门限电平用UT+表明,由上式知

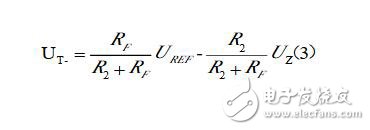

若本来的U0=-UZ,当UI逐步减小,使U0从-UZ跳变为+UZ所需的门限电平用UT-表明,则

由R=30kOhm,R2=20kOhm,UREF=6V,带入以上公式能够得到,UT+=5V,UT-=2V,即当UI增大时,在UI=5V时U0产生跳变,而当UI减小时,则在U0=2V时产生跳变。输出波形为矩形波。

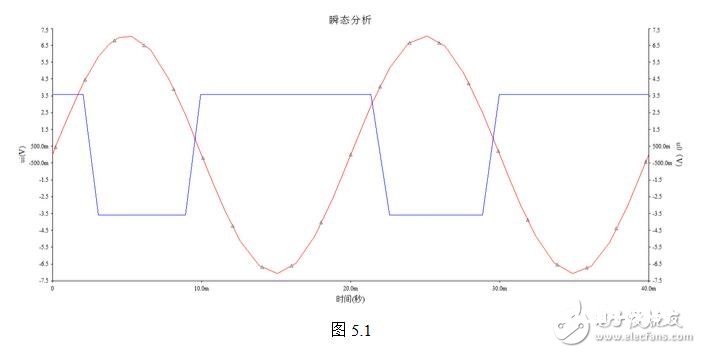

滞回比较器规划仿真成果剖析,如下所示:

仿真剖析:由RF=30kOhm,R2=20kOhm,UREF=6V,带入公式(1)(2)(3)能够得到,UT+ =5V,UT- =2V,即当UI增大时,在UI=5V时U0产生跳变,而当UI减小时,则在U0=2V时产生跳变。输出波形为矩形波

得出结论:滞回比较器效果显著,所测得数值与理论核算数值差错在试验规模之内,是有用的试验。