摘要:提出了一种根据ARM和FPGA的嵌入式数控体系规划计划。具体介绍了ARM体系的软硬件规划,根据FPGA的硬件精插补完结办法以及数控体系的加减速操控战略。该体系将ARM运转速度快、核算精度高的长处和FPGA内部逻辑的在线可重构性等特色相结合,提高了资源利用率和实时性,增强了数控体系的灵活性。仿真和实践成果表明,整个操控体系具有实时性好、低本钱、高功用等长处。

0 导言

现有的数控体系中多选用工控机加运动操控卡的核算机数控体系计划进行运动操控器的规划。跟着工控机全体功用日趋杂乱,对运动操控体系的体积、本钱、功耗等方面的要求越来越严苛。现有核算机数控体系在运动操控方面逐步出现出资源糟蹋严峻、实时性差的下风。此外,数控体系的敞开性、模块化和可重构规划是现在数控技能领域研讨的热门,意图是为了习惯技能开展和便于用户开发自己的功用。本文根据ARM和FPGA的硬件渠道,选用战略和机制相别离的规划思维,规划了一种具有高敞开性特征的嵌入式数控体系。该数控体系不只具有了以往大型数控体系的首要功用,还具有了更好的操作性和切开功用,并且在敞开性方面优势更为杰出,使数控体系使用软件具有可移植性和互换性。

1 根据ARM和FPGA的嵌入式数控体系全体计划

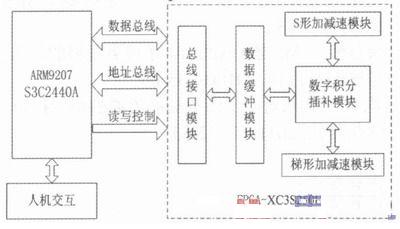

根据ARM和FPGA的嵌入式数控体系结构如图1所示。依照模块区分的思维,本文将操控器分为人机交互、插补算法和通讯三部分。体系中 ARM选用三星公司推出的16/32位RISC微处理器S3C2440A,它选用了ARM920T内核,中心频率高达400MHz。FPGA选用 Xilinx公司Spartan 3E系列的XC3S250E。

图1 根据ARM+FPGA的嵌入式数控体系结构

2 S3C2440A操控体系

ARM作为数控体系的操控中心首要担任对从数据存储器中读取或直接从上位PC或网络取得的零件加工代码和操控信息进行译码、运算、逻辑处理,完结加工数据的粗插补以及人机界面和数据通讯。ARM体系是整个数控体系的操控中心,在嵌入式操作体系的办理下,选用分时处理的办法完结整个体系的信息处理和粗插补运算,经过键盘、触摸屏等输入设备输入各种操控指令,对数控体系的实时运转状况经过LCD、指示灯等显现,完结人机友爱交互。根据 S3C2440A操控器有各种通讯接口,包含RS232、RS485、以太网口、USB等接口模块。经过这些接口完结文件传输和网络操控。

嵌入式数控的软件体系整体结构如图2所示。体系的软件结构首要分为两部分:操作体系软件和数控使用软件。因为数控体系是个实时多使命体系,实时性要求很高,为确保各个使命的和谐履行,本体系选用了μC/OS-II实时操作体系作为软件渠道。

图2 嵌入式数控的软件体系整体构图

要完结该操作体系在S3C2440A微处理器渠道上的正常运转,需求修正与处理器类型有关部分的代码,操作体系移植需求完结的作业是改写三个文件,即改写文件0S_CPU.H、0S_CPU_A.ASM和OS_CPU_C.C。其间0S_CPU.H包含了用#define句子界说的,与处理器相关的变数、宏和类型。0S_CPU_A.ASM中界说了几个汇编言语函数,包含中止服务程序的中止向量地址等。假如某些C编译器答应在C言语中直接插入汇编言句子子,就不必定需求,用户能够把所需的汇编言语代码直接放到OS_CPU_C.C文件中。

3 ARM和FPGA的接口规划

为使体系能够依照预期规划杰出作业,首要要从硬件上完结ARM和FPGA之间的牢靠通讯。本文选用的计划是在FPGA上完结SRAM时序,将FPGA作为一块特别的内存设备挂接到ARM的内存地址空间。这样在ARM端只需求编写SRAM的驱动程序就能够完结对FPGA端的数据写入和读取。

3.1 SRAM时序

SRAM时序分为读时序和写时序两种。当CPU对SRAM进行读操作时,首要会在地址线上写入正确的地址信号,接着是对SRAM芯片的片选信号,然后是对芯片的读信号,之后经过必定的振荡期后CPU在数据线上读到安稳的有用数据。

当CPU对SRAM进行写操作时,首要会在地址线上写入正确的地址线号,接着是对SRAM芯片的片选信号,然后是对芯片的写信号,在写信号上升沿之前CPU会在数据线上准备好有用数据,以供SRAM芯片在写信号上升沿将数据写入相应的地址单元。

3.2 FPGA端SRAM完结

ARM和FPGA的通讯需求的接口信号有地址线A0-A15、数据线D0-D15、片选信号nCS,读信号nRD和写信号new,每次需求完结16位数据的读写。用Verilog硬件言语描绘SRAM时序如下:

可知只要在片选信号、读信号都拉低而写信号仍为高的情况下,才在data线上输出地址线上对应单元的数值,其他情况下FPGA都将data线置为高阻态,抛弃对data线的操控。

4 根据FPGA的DDA精插补器规划

跟着FPGA器材及其开发技能的日臻老练,选用FPGA完结运动操控的计划显现出巨大的潜力。因为FPGA的规划是并行的、多线程,并且具有在线可编程才能,兼备了速度快和本钱低的长处,一起克服了专用处理器灵活性方面的缺乏。根据FPGA的DDA精插补器相对传统的软件插补具有强壮的优势。

4.1 数字积分插补算法

现在比较老练的数控插补算法有逐点比较法、最小差错法和数字积分法等,数字积分法又称数字微分分析器(Digital Differential Analyzer,DDA)。选用该办法进行插补,具有运算速度快、逻辑功用强、脉冲分配均匀等特色,可完结一次、二次甚至高次曲线插补,易于完结多轴联动。

数字积分插补算法是将函数的积分运算转换成变量的求和运算。假如所挑选的脉冲当量满足小,则用求和运算替代积分所引起的差错能够不超越答应的数值。选用两个寄存器(函数寄存器和累加寄存器)和一个全加器构成数字积分器,将单位周期选得满足小,每单位周期都向累加器累加函数寄存器中的数值,假如累加器溢出,就向外发送脉冲,实时地改动函数寄存器的值,就能够完结步进电机的调速。DDA插补操控器规划的硬件描绘言语程序的流程图如图3所示。

图3 DDA插补操控器规划的硬件描绘言语程序的流程图

4.2 数字积分插补的FPGA完结

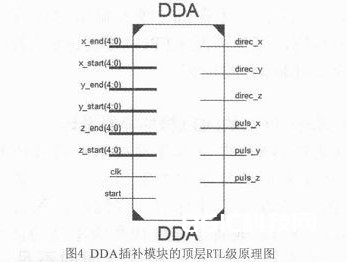

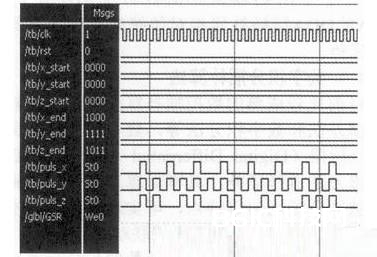

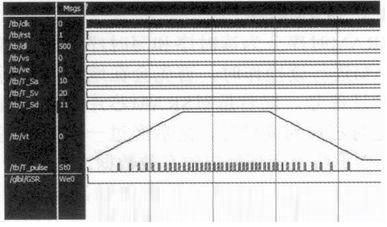

选用有限状况机的规划办法,每个轴的数字积分插补均由一个三状况机的积分累加器完结。本体系的FPGA开发环境为Xilinx公司的 Xil inx ISE,并结合ModelSim仿真软件对整个体系进行了全面的功用验证。如图4所示为DDA插补模块的顶层RTL级原理图,由图5可知DDA插补模块的输入信号为各轴的开始坐标以及时钟信号和发动信号,输出信号为各轴的脉冲信号和方向信号。

图5 DDA插补模块仿真波形

运用ModelSim仿真软件对DDA插补模块进行仿真验证。测试数据的起点坐标为(0,0,0)结尾坐标为(8,15,11),仿真成果如图5所示,显现体系很好的完结了三轴的脉冲分配。

4.3 加减速操控模块

加减速操控是数控体系的关键技能之一,也是完结数控体系高实时性的瓶颈。数控体系中,为了确保机床在发动或中止时不发生冲击、失步、超程或振荡,有必要对进给电机的脉冲频率或电压进行加减速操控。即当机床加快发动时,确保加在电机上的脉冲频率逐步添加;而当机床减速中止时,确保加在电机上的脉冲频率逐步减小。现在,电机加减速的常用操控办法是梯形加减速操控和S形加减速操控。本次规划选用两种操控计划以习惯不同作业场合的要求。

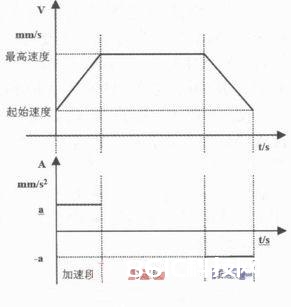

4.3.1 梯形加减速

梯形加减速是指在加减速进程中加快度为常数,速度曲线为梯形的加减速进程。梯形加减速操控算法简略、易于完结,但在加减速进程中加快度曲线不接连会导致驱动组织的振荡和冲击。正常情况下梯形加减速运动进程如图6所示分为加快段、匀速段和减速段三个阶段。

图6 正常情况下梯形加减速运动进程

图7所示为ModelSim对梯形加减速模块的仿真成果,能够看到插补器输出的脉冲速度曲线出现梯形,输出脉冲的频率的巨细随速度的改变而改变,完结了电机的梯形调速。

图7 ModelSim对梯形加减速模块的仿真成果

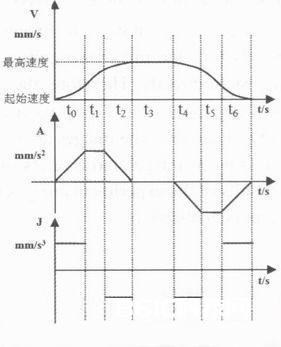

4.3.2 S形加减速

S形加减速是指在加减速时,加快度导数为常数,速度曲线为S形曲线的加减速进程。经过操控加快度导数来防止加快度骤变,减小加工进程中因为加快度骤变引起的机械体系振荡。S形曲线速度操控能够得到滑润的速度曲线,但算法杂乱,运算时间长。

图8 S形加减速曲线图

S形加减速中加快度相对加快度导数的改变规则相当于直线加减速中速度相对加快度的改变规则。如图8所示为S形曲线加减速的曲线图,图中从上到下依次为速度曲线、加快度曲线以及减速度曲线。从图中能够看出,正常情况下S形加减速分为:加加快段、匀加快段、减加快段、匀速段、加减速段、匀减速段和减减速段七个阶段。加快度接连,调速润滑,不会导致驱动组织的振荡和冲击。

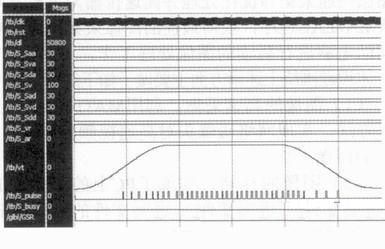

图9 ModelSim对S形加减速模块的仿真成果

图9所示为ModelSim对S形加减速模块的仿真成果,能够看到插补器输出的脉冲速度曲线出现梯形,输出脉冲的频率的巨细随速度的改变而改变,完结了电机的S形调速。

5 结束语

本文给出了一种根据ARM和FPGA的敞开性的嵌入式数控体系,突破了传统的核算机数控体系架构,选用ARM处理器S3C2440A和 FPGA器材XC3S25 0E和μC/OS-II嵌入式实时操作体系组成的数控体系软硬件渠道,充分利用了ARM微处理器的高速运算才能与FPGA的快速装备才能,大大减少了体系的外围接口器材,并具有杰出的安稳性、模块化、可扩展性、可移植性等特色,有利于完结数控体系的敞开化和网络化,有用地降低了体系本钱,合适我国数控体系开展的需求,具有宽广的使用远景。