槽要吐,文章仍是要写的。咱们知道,做一些layout guide是信号完整性工程师的根本作业之一,layout guide能够说是一些SI规矩的物理表现。

抽丝剥茧系列——一次解谜阅历

抽丝剥茧系列文章之关于时序

抽丝剥茧系列文章之过孔挑选

前两天,跟某友商沟通,是一位测验范畴的大牛,他们也运营着一个自媒体。每到咱们激起一些火花,大牛就会说“看,又是一篇好文章了吧”。看来大牛他们写文章的压力也很大啊,想到这儿,小陈不由潸然泪下,手一抖,把抽丝剥茧打成了愁死脖间•••

槽要吐,文章仍是要写的。咱们知道,做一些layout guide是信号完整性工程师的根本作业之一,layout guide能够说是一些SI规矩的物理表现。某同学发现了一份这样的layout guide:

拓扑是这姿态的

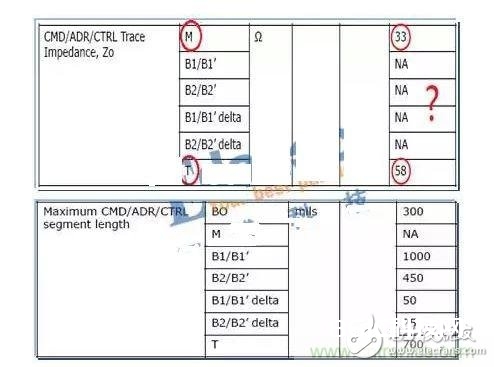

要求是这姿态的

能够看到,骨干段M只需阻抗要求,没有长度要求。而分支B1/B1’/B2/’B2’只需长度要求没有阻抗要求,这是为啥?

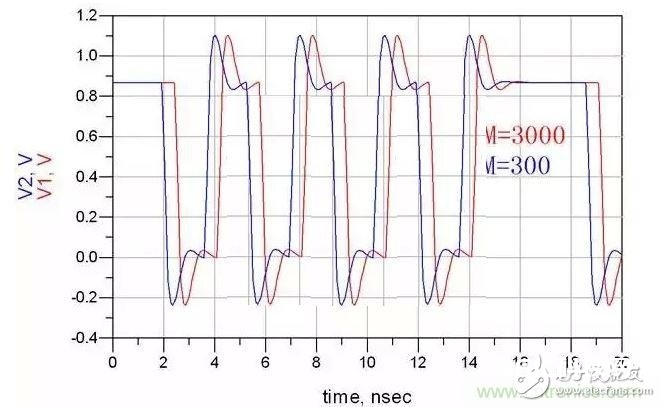

首要,咱们知道大部分器材的驱动阻抗是较低的,这样减小驱动器自身的分压,尽管这样会形成较大的源端反射。而速率越来越高时,需要在功耗和信号完整性做一个平衡,驱动阻抗逐渐的高了起来,而上拓扑为DDR2,驱动阻抗通常在33欧姆左右,将M段的阻抗操控在33欧姆,则意味着源端反射十分小,这样一切进入M段往驱动端走的反射信号悉数有去无回。M段的长度,也就不会对接纳端信号形成什么影响了,如下图:

3

而在M与B/T接壤的节点处,反射是不可避免的。最重要的是第一次从M过来在这个点的反射,以及第一次从接纳端反射回来的能量,之后的反射波因为分压以及反射系数等原因能量是十分小的,能够忽略不计。

先来看第一次从M过来在这个点的反射。咱们知道几个电阻的并联阻抗必定小于其间恣意电阻的阻抗,传输线同理。假设B段阻抗为60欧姆,从M往接纳端看的阻抗为58//60//60≈20欧姆,反射系数24%;假设B段阻抗为40,从M往接纳端看的阻抗为58//40//40≈15欧姆,反射系数37%。不同看起来不是特别大,所以B并没有清晰的阻抗要求,但其实layout guide里还有一句话,便是B段走线走越细越好。

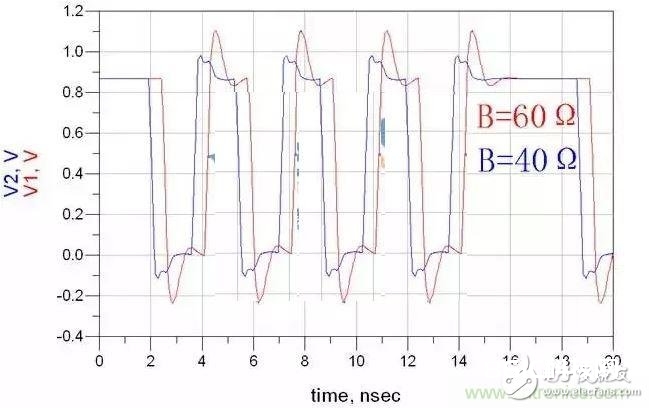

再来看看第一次从接纳端反射回来的能量,这可就剪不断理还乱了。不过咱们知道,影响反射的除了阻抗还有走线长度,走线较短的话,反射将会吞没在上升时间之中。咱们来看一下线长符合要求时阻抗改变的状况:

看来只需分支长度确保了,其实阻抗影响并不大。关于各种拓扑,能够变的戏法仍是十分多的,layout guide可不是只需“x/x/x/x信号阻抗操控50Ω”的哦。