规划人员挑选具有优异调试才能的FPGA器材,能够缩短开发周期并降低成本,一同明显加速上市速度。FPGA和SoC规划人员要战胜许多应战,才能够把产品投入出产。

一般说来,他们首要要为自己的规划评价适宜器材;然后,运用硬件描绘言语(HDL)规划,布局布线器材,终究,在投入出产之前,还要对整个FPGA进行调试。

关于许多规划,特别是工业和嵌入式商场的规划来说,能够挑选的FPGA真实多不胜数。在大多数情况下,决议挑选哪家FPGA供货商取决于其相关的软件开发经历。虽然软件开发经历也应该是考虑要素,可是,更重要的要素应该是调试才能及为加速出产供给的支撑。现在,阿尔特拉(Altera)、莱迪思(LatTIce)、美高森美(Microsemi)和赛灵思(Xilinx)等供货商都供给许多FPGA调试东西,可是,规划人员对未来的FPGA规划战略进行评价时,应该考虑选用一种更智能的调试东西。

根底调试 – 逻辑剖析仪

每个首要的FPGA供货商都供给逻辑剖析仪作为调试东西。这是一种运用内部FPGA逻辑单元和嵌入式块存储器来施行功用的技能。规划人员能够规则监测哪种信号,并设置触发器来告知逻辑剖析仪何时开端收集数据。逻辑剖析仪设置好后,规划人员有必要从头按次序运转归纳和布局布线,将功用归入到规划中。规划从头编译和从头编程后,规划人员便能够开端调查逻辑剖析仪收集的逻辑信号。

需求留意的是,因为这些信号需求采样,它们收集的并非数据的实时功用。逻辑剖析仪只能以答应其收集数据的速度运转,并将数据保存在内部存储器内。因为规划有必要从头编译以刺进逻辑剖析仪,因而,这一进程实践上或许消除正在寻觅的缝隙。虽然这看起来好像不错,可是,不了解原问题是什么,意味着后边再履行组成和布局布线操作时,问题或许会再次产生和从头呈现。

虽然如此,规划人员能够依据触发条件来查看信号状况,这样做的确能够协助调试规划问题。选用逻辑剖析仪是一个不断迭代的进程。规划人员查找产生的问题,进行更新,然后对规划进行从头编译,再查看新的成果,然后重复这个进程,直到发现缝隙。每个迭代和处理每个详细缝隙所需的时刻都不同,因为逻辑剖析仪的采样速度,因而不一定能够找到一切问题。

下一代调试东西

因为逻辑剖析仪在调试方面的约束,业界规划了新一代调试东西,以加速FPGA和板的验证。有些EDA供货商在归纳东西内集成了逻辑剖析仪功用,缩短了缝隙查找迭代的时刻,能够查看规划和使触发设置更简略。规划人员还能够更改规划,使其主动映射回到寄存器传送级(RTL)代码。为了节省内部FPGA资源,有些EDA东西能够收集多组信号,并将它们多路复用。在调试进程初期,咱们不知道问题的实践源头时,这样做很有协助。新思科技(Synopsys)在其idenTIfy逻辑剖析仪和Synplify归纳东西中现已施行了这些特色。虽然他们为调试进程供给了这些改进,可是,这些办法因需求从头编译,因而影响原始规划和减慢信号收集,所以遭到约束。

实践上,对工程师有协助的,除了逻辑剖析仪,还有示波器。这种功用答应实时显现器材内部信号。用探头实时勘探FPGA内的节点,强制赋予内部信号不同值,调查对规划的即时影响,也是十分抱负的。此外,勘探内部存储器的才能以及SERDES收发器勘探点也是十分有用的。假如能够供给一切这些才能而不影响FPGA规划,将明显简化调试进程。

这种办法的一个实例是美高森美Libero SoC软件中的SmartDebug东西箱,该东西箱与公司的SmartFusion2、IGLOO2和RTG4 FPGA一同运用。这个东西箱使规划人员能够调试FPGA结构、存储块和SERDES,就好象它们正在运用示波器相同。选用这种智能调试,能够运用内置在FPGA结构中的专用勘探点,明显加速和简化调试进程。不需求对规划进行从头编译就能够挑选不同的勘探点。增强的调试特色可拜访任何逻辑元件,使规划人员能够实时查看输入和输出状况,不影响用户的FPGA规划。这些特色包含:

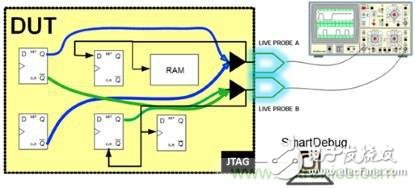

-现场探头:答应选用两个专用探头,经装备用于调查逻辑元件中任何输入或输出的勘探点(图1)。然后,探头数据可发送到示波器或乃至从头引导回到FPGA结构,驱动内部逻辑剖析仪。这些勘探点是实时动态的。勘探点能够经过软件在运转中更改,不需求把FPGA从头编译或从头编程。

-有源探头:这种特色答应动态异步读取或写入触发器或勘探点。这种才能运用户能够快速从内部调查逻辑输出或经过写入勘探点,快速试验逻辑将遭到怎样的影响。可将任何数量的信号强制赋予到规则值,正如现场探头相同,不需求把FPGA从头编译或从头编程。

探头刺进:这用于在规划中刺进其它探头,将信号输出到FPGA封装引脚,以对规划进行评价和调试。这种特色的确需求添加布局布线,从而在I/O添加信号,但并不一定需求完好的从头编译。

图1 现场探头运用实例(来历:美高森美)

FPGA规划人员把30%或更多的时刻一般花在调试上。依据项目的规划和状况,乃至需求更多的调试时刻。因为调试触及许多迭代周期,可调查性和可控性有限,常常要从头运转布局布线,时序收敛和从头编程,因而调试是十分苦楚的作业。与仅运用传统刺进逻辑剖析仪比较,智能调试东西使得工程师能够更快地对他们的FPGA规划进行验证。这些东西使得规划人员在整个规划中能够实时调查信号和操控信号状况,明显提高了调试速度。

最近,据一名客户陈述,他们选用内部逻辑剖析仪花了一周时刻来企图调试一个问题。但在选用智能调试东西替代后,工程师仅仅在两个小时内就找出了问题。终究追寻到,这个问题来自与工程师选用逻辑剖析仪时调查的一个彻底不同的规划模块。然后工程师运用有源探头特色强制赋予不同的数值,保证电路恰当呼应的方法,进一步改进了规划。

对FPGA规划人员来说,增强调试才能是影响严重。最新的解决方案能够明显缩短调试验证时刻,为FPGA供给无与伦比的可调查性和可控性。成果使得,在挑选器材时更注重FPGA调试才能的规划人员,能够缩短开发周期,降低成本,一同明显加速上市速度。