有人以为比如图形处理器(GPU)和TIlera处理器等多核处理器在某些使用中正逐渐代替现场可编程门陈设(FPGA)。理由是这些多核处理器的处理功能要高许多,例如,因为GPU起先首要担任图形制作,因而,其特别长于处理单精度(SP)及(某种状况下)双精度(DP)浮点(FP)运算。TIlera的TILE设备当时不支持硬件FP运算,但要求进行软件模仿,且功能价值昂扬。一般来说,FPGA亦是如此,设备经过使用多种资源来处理FP运算问题。到达可接受功能要求IP区块需耗费多个门并要求深流水线技能。例如:当时Tesla级GPU每秒最高可履行1012次浮点运算或1TFLOPS,而Xilinx Virtex-6设备则为150 GFLOPS。

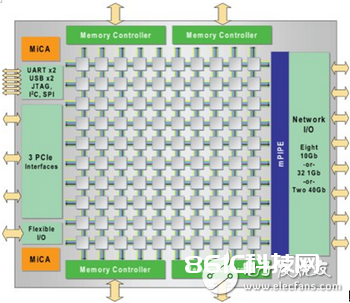

当考虑到定点运算时,状况有所不同。新一代GPU在浮点速率相同的状况下可履行整数运算,例如:当Virtex-6设备进步至500GOPS时,GPU每秒可履行1012次运算或1TOPS。整数功能是TILE处理器的优势地点:8位数据时,TILE-Gx(图1)最高履行才能为750GOPS,32位数据时为188GOPS。

FPGA可以使用其并行及习惯多种算法的特性来取得愈加挨近理论最大值的功能。可是,FPGA需求更大的硅片空间和更长的开发时刻来挨近这些理论最大值。关于习惯于GPU硬件并行形式的算法,GPU现已可以到达峰值的20~30%。它们相同具有合理的硅密度(40nm工艺,32nm研制中)和开发时刻(一般只稀有周,而FPGA则需几个月)。TILEPro64处理器可提供FPGA相类似的习惯性和GPU相类似的可编程性,可是,因为其粗糙的使命级问题分化特色使得其无法像FPGA和GPU那样完成细粒度并行。