在ECM中,会涉及到FPGA、RT以及主机,那么三者之间是怎么进行数据流的传输呢?本文将以cRIO-9068为例,带咱们了解整个编程以及完结进程。

一、FPGA、RT以及主机数据流之间的通讯概览

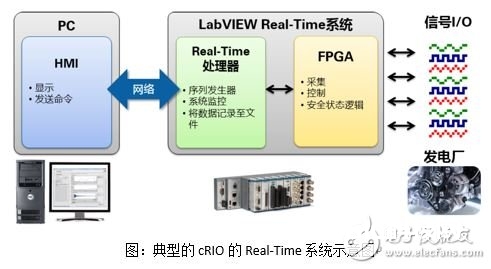

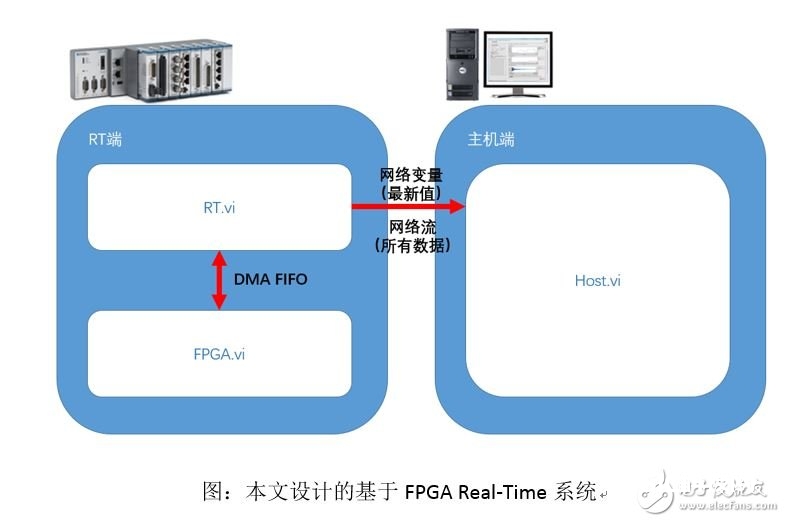

在一个含FPGA的Real-TIme体系中,FPGA担任收集信号,然后将收集的数据传输至RT端进行监控、处理,一起在主机进行数据的显现、记载或许发送指令。典型的根据cRIO的Real-TIme体系如下图所示:

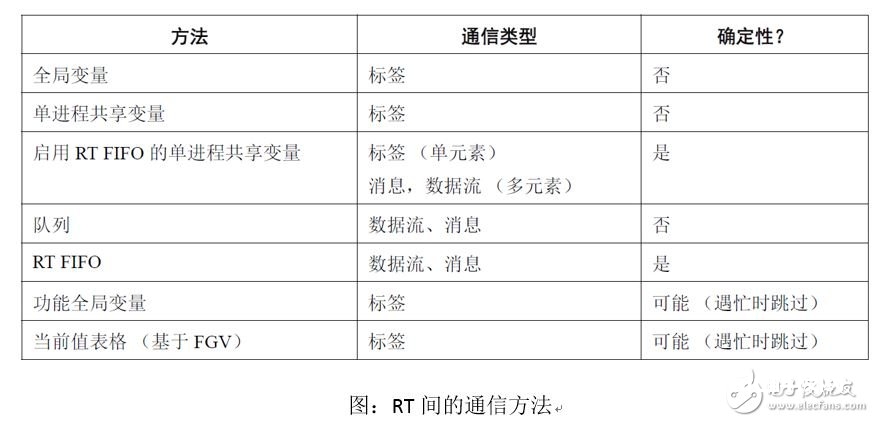

数据在Real-TIme体系中首要分为两种,一种是比方音讯,指令等等,此类数据咱们只重视其最新的值,首要经过标签、音讯进行数据的传递;别的一种是数据流,咱们需求获取一切的数据信息,而不仅仅是最新值,首要经过网络流、FIFO进行传递。

关于收集卡收集到的数据,咱们有时分是期望对其进行记载,并在Host端进行显现观测。一般,FPGA与RT是经过FIFO进行数据流的传输,而RT则选用网络流与主机传输数据。本文将以cRIO-9068为例,展现从信号收集到上位机显现的整个进程,协助咱们更好地了解Real-TIme体系的数据处理方法

二、硬件软件

数采卡:NI 9263

设备:cRIO-9068;RIGOL示波器

软件:LabVIEW; LabVIEW Real-Time;LabVIEW FPGA;CompactRIO

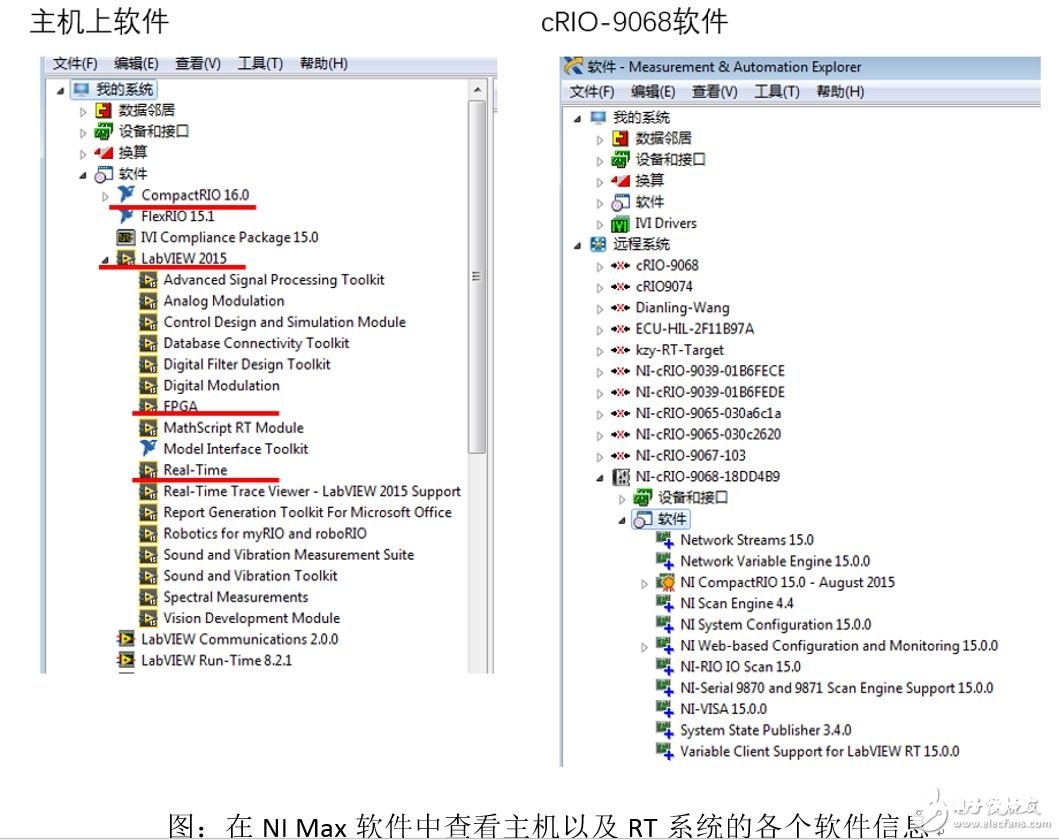

(能够在NI Max中检查自己所装置的软件、驱动以及模块的版别,坚持cRIO-9068中的软件版别正确)

终究,硬件衔接如图。

三、规划进程

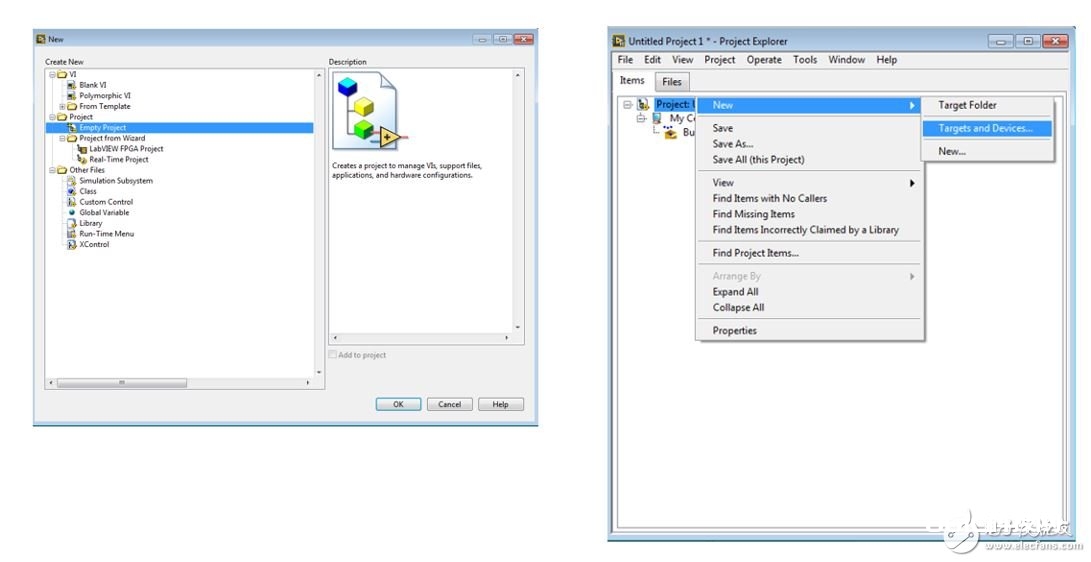

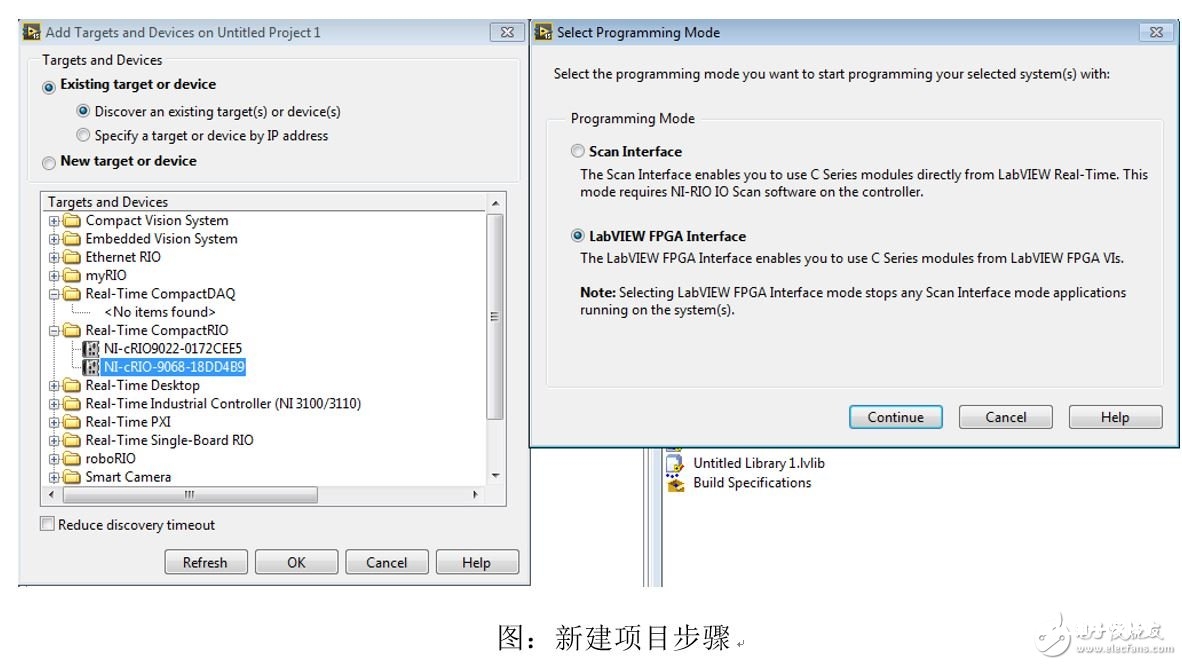

1)新建项目

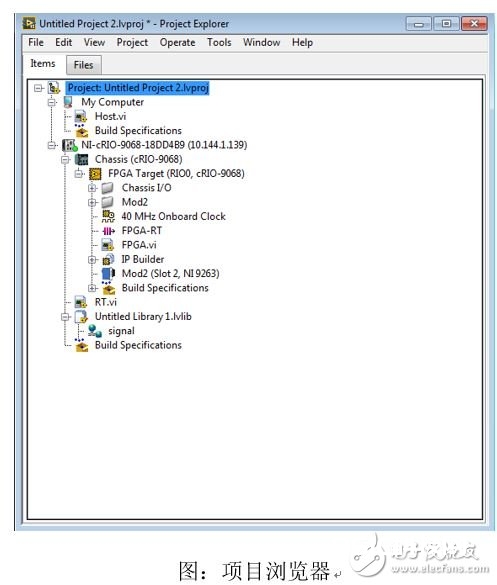

翻开LabVIEW,新建项目,在项目浏览器中,右键我的项目,挑选增加方针设备,将硬件cRIO-9068以及NI 9263同时增参加新建的项目。

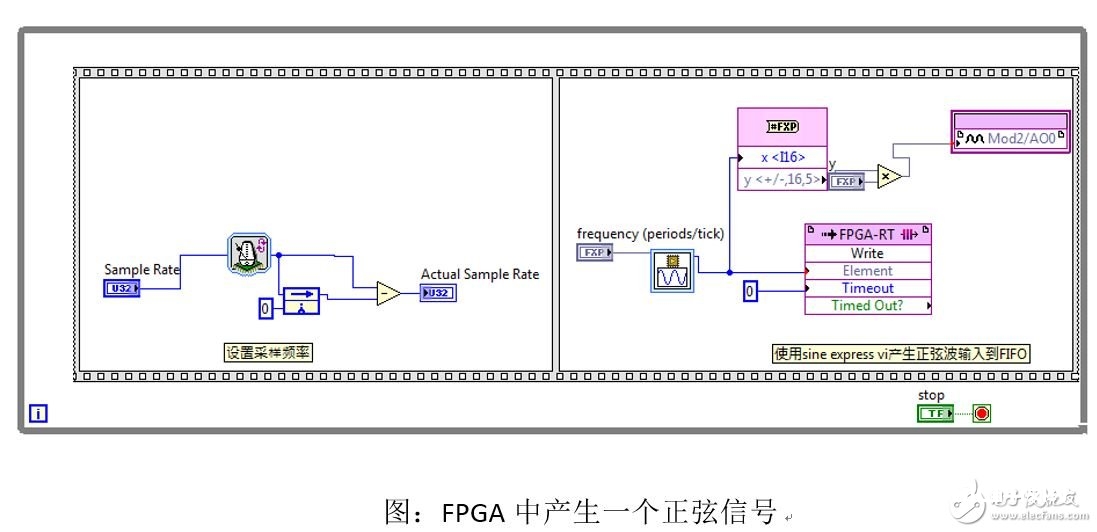

2)FPGA.vi的规划

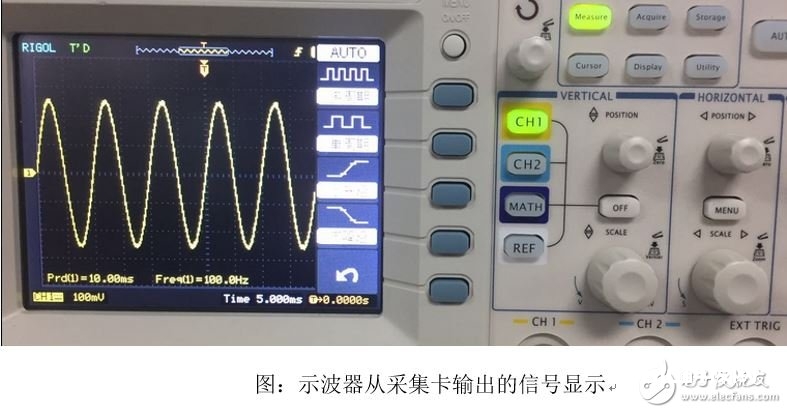

首要咱们需求在FPGA中发生一个正弦信号,经由NI 9263的模仿端口输出。

留意:此处不能运用单周期守时循环,因为该vi无法在一个时钟滴答内完结履行。关于单周期守时循环参阅链接:

因为要将FPGA发生的正弦波信号传到RT端进行显现等处理,归于数据流的传输,因而咱们在此处运用DMA FIFO()。

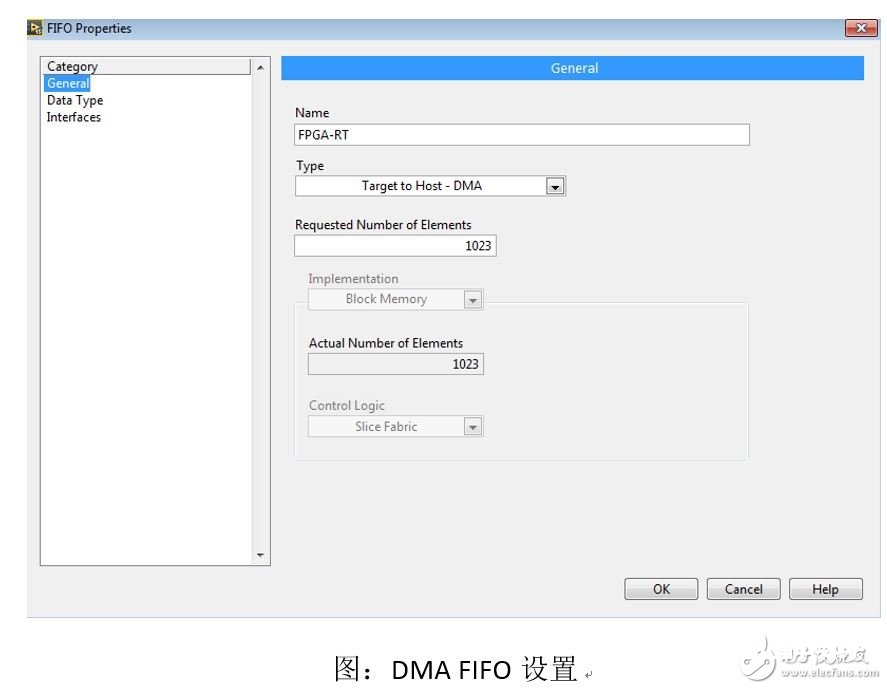

在项目浏览器中FPGA下右键新建一个FIFO,其FIFO设置如下:

其间在Type处挑选类型:Target to Host-DMA,巨细运用默许的即可。在Data Type中挑选数据的类型,此处咱们传输的是无符号的32位数据,因而挑选U32即可。

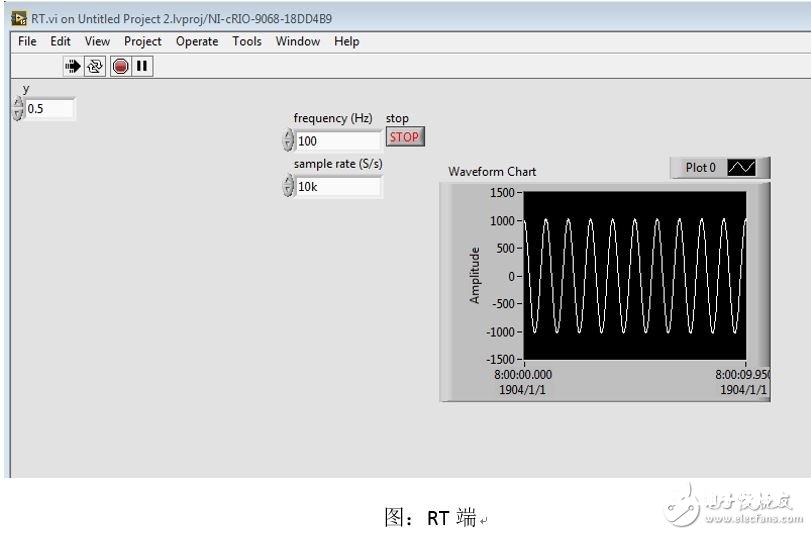

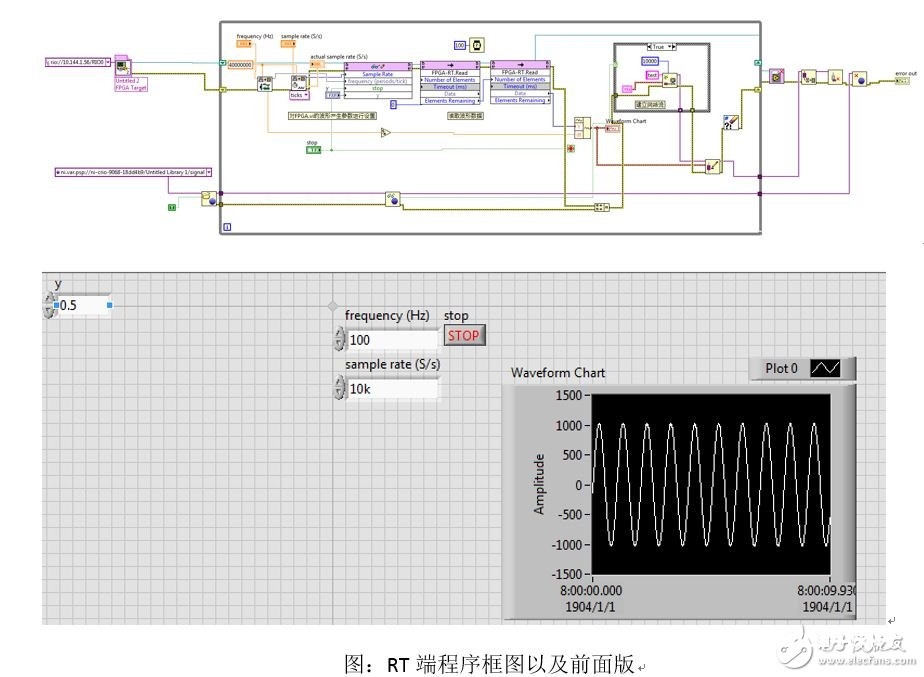

3)RT.vi的规划

RT端的vi首要由两部分组成,一部分是从FIFO中读取从FPGA传来的数据,一部分是树立网络流,将数据传给主机进行检测。这儿要留意的是,因为咱们需求的是翻开主机随时读取数据,主机程序运转时分。

RT端的vi首要由两部分组成,一部分是从FIFO中读取从FPGA传来的数据,一部分是树立网络流,将数据传给主机进行检测。这儿要留意的是,因为咱们需求的是翻开主机随时读取数据,主机程序运转时分,会发生一个信号,使RT端的网络流端树立而且写入数据。因而,咱们新建一个布尔变量,作为这个传递信号。

因而,在RT端,咱们对主机的数据传递首要运用了两种方法,一种是网络流,用于每一个数据传递;另一个是网络变量,获取布尔控件的最新值。

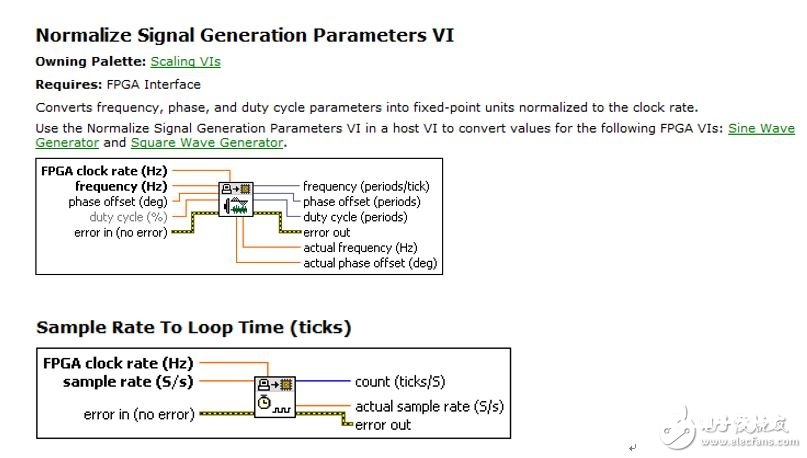

在FIFO波形的传递进程中,常常运用到以下两个数,这儿做多一些的介绍。

Normalize Signal Generation Parameters Sample Rate To Loop Time

这两个会常常调配运用,首要是对FPGA部分发生波形的波形参数进行设置,其间首要是对波形的频率以及采样频率(在FPGA端则需求运用Loop Time函数),后面会衔接运用“Write/Read Control”节点。

在网络流的设置中,依照惯例:树立写端-写入-封闭的次序,其间留意的是,主机在树立的时分设置超时(Time out)默许是-1,会无限时刻的等候下去。且写入端的姓名不能和读取端的姓名有重合部分,否则会报错的。

至此,咱们完结了RT端以及FPGA的程序编写。可是,在有些情况下,咱们会期望cRIO里边的程序固定,上电即可运转(比方上电即可收集或许发生波形),而咱们能够随意的不守时的运用主机经过局域网随机抓取一段cRIO数据,因而咱们需求在主机上(host端)新建一个vi完结此功用。

为了便利起见,此处新建的主机vi和RT等程序放在一个项目内,实践使用中新建一个项目,在新的项目中编写主机的代码。

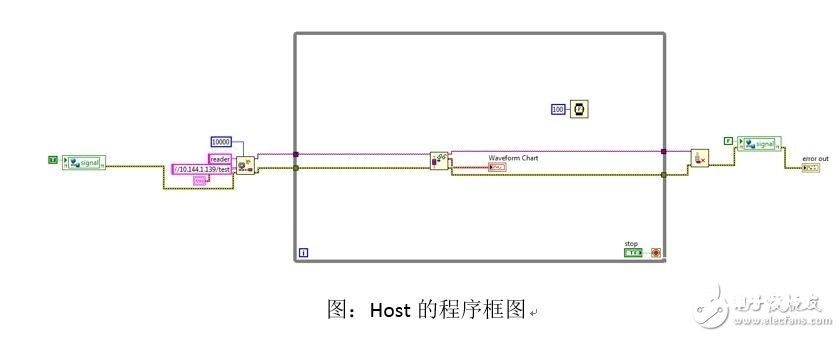

4)Host.vi的规划

在主机上,咱们这儿简略的仅仅读取,首要会赋值给同享变量在从而在RT端树立网络流写入端写入数据。

5)整个体系显现如下