跟着电子技能的开展,运用体系向小型化,快速化,大容量,重量轻的方向开展,电子规划主动化EDA(Electronics Dcsign Automation)技能应运而生,他是电子产品及体系开发范畴中一场革命性革新,也是高科技化开展的必定产品。EDA首要运用于数字电路的规划,现在他在我国的运用多数是用在FPGA/CPLD/EPLD的规划中。EDA体系为电子产品的开发,电子体系的规划,电子体系工程供给了高度集成的软件环境,具有完好而主动的完结流程,直观的没计环境,巨大的模仿库,简略而优秀的仿真功用等优势。

1 导言

抢答器在各种常识、智力竞赛中有很大的用途,他能精确、公平、直观地判别出榜首抢答者,并通过抢答器的指示灯显现和警示蜂鸣等手法指示出榜首抢答者。现在在许多的综艺节目中,更多的选用大屏幕显现抢答者,烘托出愈加剧烈的竞赛气氛,并且合作演播厅的全体作用,就要求抢答器也能供给多种接口,并扔掉传统的长长的蜘蛛网似的开关引线。本文所介绍的是一种依据EDA技能的有用无线抢答器体系的规划计划,他选用超大规模逻辑器材CPLD来处理抢答器的逻辑,通过上位微机来完结声响和动画等作用。该计划的长处在于:反响快、装置简略、掩盖规模广、可扩展性强、运用作用更漂亮等。

2体系构成

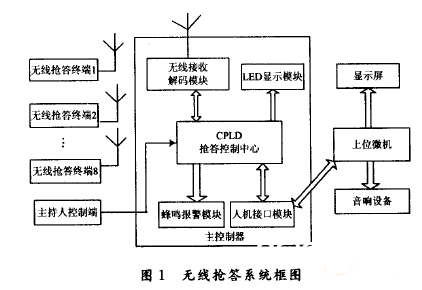

依据CPLD和无线编解码发射接纳技能的无线抢答器体系的原理框图如图1所示,由8路无线抢答终端、主操控器以及上位微机体系组成。

2.1无线抢答终端

在本规划中,无线抢答终端首要包含编码模块、无线发射模块和功率放大模块,其内部结构框图如图2所示。

其间编码模块选用的是专用红外遥控编码芯片PT2262-IR,在主操控器端的无线解码模块选用的与其配对运用的解码芯片PT2272,他们都是台湾普城公司出产的一种CMOS工艺制造的低功耗低价位通用编解码电路,最多可有12位三态地址端管脚,恣意组合可供给531441地址码。PT2262最多可有6位(DO ~D5)数据端管脚,设定的地址码和数据码从17脚串行输出,十分合适用于无线遥控发射电路,其有用发射接纳间隔为80 m,发射电路电源规模为2-12 V,接纳电路电源规模为4. 8~5. 0 V,发射电路有用发射反响时间≤0. 2 ms.

无线发射承受模块选用通用系列产品9912,在主操控器端的无线接纳模块选用的是9921,这样不只能够加速制造进程,并且还能够添加电路的安稳与可靠性。

2. 2 CPLD主控芯片

体系中心操控芯片选用的是Altera公司MAX7000S系列新一代CPLD器材EPM7128SLC84-15。该芯片选用CMOS E2PROM工艺,传输推迟仅为5 ns;内部具有丰厚的资源-128个触发器、2500个用户可编程门;并且具有68个用户可编程的I/O接口,为体系界说输人、输出和双向口供给了极大的便利;为了比较合适混合电压体系,通过装备,输人引脚能够兼容3.3V/5V逻辑电平,输出能够装备为3. 3 V/5 V逻辑电平输出。EPM7128一起还供给了JTAG接口,可进行ISP编程,极大地便利了用户。

新的CPLD芯片技能除了大大削减集成芯片的数目,便于对体系进行扩展,还能够缩短开发周期。下降开发本钱,一起提高了技能保密性。与FPGA技能比较,CPLD有掉电不易失的长处,运用愈加便利。

2. 3人机接口电路

本体系中,主操控器与上位微机的通讯选用RS 232串行异步通讯办法。因为CPLD主控芯片的输出电平与RS 232的电平不匹配,所以主操控器与上位微机的人机接口电路,首要选用选用Max232芯片的进行电平转化。Max232是MAXIM公司出产的,包含两路驱动器和接纳器的RS 232转化芯片。芯片内部有一个电压转化器,能够把输入的+5V电压转化为RS232接口所需的±10V电压。

3软件规划

本规划中的软件由CPLD操控程序和土位机PC端的动态作用演示程序2部分组成。CPLD操控程序完结与无线接纳解码模块的衔接及完结与外围模块之间的数据转化和通讯。上位机PC端的动态作用演示程序重点是完结依据VB的交互界面的规划。

3. 1依据CPLD的中心操控程序

CPLD操控程序是本体系软件规划的中心,他选用的是在美国Altera公司的Max+Plus II 10.0平台上用VHDI高档言语输人规划办法。他有专用的东西来完结将言语描绘过的电路功用转化为实践的电路,具有很好的通用性和灵活性。他的首要功用:接纳并保存无线接纳解码模块传送的抢答成功的终端的编码并封闭接纳模块,直至操控端复位;一起蜂鸣器奏响并在LED显现抢答成功的终端编号;并完结CPLD与串行接口芯片的数据交换.

该操控程序首要包含4个功用子模块:分频模块、抢答终端编码接纳模块、串行发送模块、串行接纳模块。在Max-f-Plus II 10. 0中规划输人各个模块的VHDL的程序后,生成库器材并组成体系原理图如图3所示。以下扼要介绍抢答终端编码接纳模块和串行发送模块的程序规划。

图4为生成的该模块原理图,其VHDL源程序如下:

3.1.2串行发送模块

如图4所示,该模块将抢答终端编码接纳模块输出的抢答终端的编码依照串行异步通讯规矩发送给人机接口电路。在串口通讯中,咱们约好的帧格局为1位开端位+8位数据位+1位中止位,没有校验位,通讯波特率为9600。依据约好,该模块输出数据为10位,在发送完10位后,就中止发送,并使发送端电平处于逻辑1,然后等候下次的发送。其VHDL源程序如下:

3. 2上位机PC端的演示程序

本软件是在VB 6.0环境下开发的,并使用其数据办理功用,树立竞赛题库并供给办理界面。其与主操控器之间的串行口通讯规划部分充分使用了Mscomm串行口通讯控件。因为该控件供给通过串口发送和接纳数据的串行通讯才能,包含了悉数Windows API中关于串行通讯的16个函数所完结的功用,并且开辟了更多运用户规划便利的目标特色来满意不同用户不同事务的需求,因而给编程带来极大的便利。

本软件在PC环境下运转,包含以下几个功用:依据设定主动抽出竞赛标题、操控主操控器的作业、声光作用显现抢答终端编号并倒数计时、现场作用烘托等。具体程序在此不再赘述。

4结语

通过重复实验,该体系运转安稳,操作便利,达到了预期的规划作用,具有可操作性强、现场作用好的特色,已经在常识竟赛等相关活动中实践运用。