导言

关于码分多址的扩频通讯办法而言,只要当接纳端本地伪码与发端伪码处于相同相位状况时,有用的信息才干被解出。因而,扩频序列相位的捕获与盯梢是扩频通讯体系的要害,而伪码序列相位的捕获尤为重要。滑动相关法是常用的办法之一。扩频通讯体系要求实时性,以及较高的数据处理速度,这正是FPGA的优势。所以在扩频通讯体系中,很多运用FPGA芯片作为前级处理芯片。

完结原理

原理剖析

接纳机端接纳到的扩频信号能够表明为:

其间,P_{r}为接纳信号功率,τ_{d}为传输时延,D(t)为信息码, PN(t)为伪码, n(t)为传输进程的加性噪声。扩频接纳机要完结的使命便是去掉PN(T-τ_{d}) 伪码项和cos(ω_{0}t+φ) 载波项,然后得到信息数据DZ(t)。

VCO输出I、Q两路信号:

经过同相正交相乘器得到:

运用PN码的相关特性,即相位对齐时,相关成果最大。当载波和码相位都对按时,经过累加清洗(低通滤波)输出为:

经过平方相加可去掉载波对相关成果的影响,得到相关峰。

完结框图

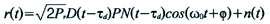

在直接序列扩频体系中,伪码的捕获是构成码同步体系的重要结构,也是直扩体系中必不可少的部分。接纳机若要把伪码扩展的信号解出,接纳方就有必要能发生一个与发方相同的伪码序列(确保最大相关值),并且,该本地伪码速率、相位要与接纳到的伪码坚持共同。关于约定好的收、发方用同一个伪码很简略办到,可是,假如要从解扩相关器得到传送的信息,只是确保相同的码型是远远不够的。因为即便相同的伪随机码,当相位差大于一个码片时,它们的相关峰就彻底消失。在实践通讯中,因为收、发信机时钟的不安稳性,接纳、发射时刻的不确认性,信道传输推迟及搅扰等要素的影响,收、发伪码序列的相位差是随机的。因而解扩的第一步便是要在接纳信号的伪码相位中捕获到一个与本地伪码共同的相位状况。当这种状况出现时相关器就会有一个相关峰值输出,峰值与门限比较,若超出则确认相位已捕捉到,当即中止捕捉动作,转入相位盯梢状况;若小于门限则改动本地码相位,继续进行捕获。体系完结原理如图1所示。

完结办法

依据相位捕获的办法可分为:接连相位滑动相关法和在此思路上改善的不接连相位相关法。

接连相位滑动相关法

此办法是经过改动本地伪码时钟速率,与发端伪码时钟速率坚持一个适宜偏移量,使接纳信号中伪码相位与本地伪码相位在相关器内进行相对滑动。这种办法的相位捕获是接连进行的,所以相关峰值是一个接连量。相关值一旦超越捕获门限,标志正确相位已被查找到,接纳机当即康复本地伪码时钟速率(收、发信机都运用安稳度很高的振动源,所以它们的码速率能够根本坚持共同),中止相位滑动,发动盯梢电路,使相位差进一步缩小(意味着相关性增大),取得更高解扩信噪比,满意这以后解调门限要求。此种捕获办法捕获时刻和检测概率彼此对立。例如,关于一个N=215位的PN码,两伪码之间最大相对滑动速率约为5kc/ps,遍历其所有相关状况需求的时刻为6.55S。在实践通讯进程中,因为搅扰及其它原因形成伪码相位失锁需求从头捕捉时,这么长的捕捉时刻会严重影响通讯质量,因而是不可取的。由以上剖析可知,这种捕捉办法相位查找精度高但一起导致了过长的捕捉时刻,在实践中很少运用,但其思路值得学习。不接连滑动相关法便是在此基础上的改善。

不接连相位滑动相关法

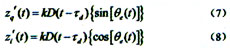

所谓接连与不接连的区别是对查找中相位的滑动改动量而言,后一种办法是把接连的相位查找改为跳动式的查找,即两个码之间的相位滑动量不再是接连地以必定的步进量发生相位滑动。不接连滑动相关法是运用一个相位查找电路,在捕获进程中使本地伪码相位以必定的步进值跳动改动,这样遍历整个伪码时刻大大削减。与前一种办法比较,它的收、发伪码时钟速率坚持共同,然后不会形成码片宽度不共同,导致相关峰值下降。本地伪码与接纳伪码相位的相对改动是靠查找电路对伪码发生器时钟的超前、滞后操控来完结的,因而相位查找电路(如图2所示)是不同于前者的要害所在。下面要点评论完结半码片滑动的完结办法。

捕获办法1 (滑动步进为TC/2)

时钟取反法:

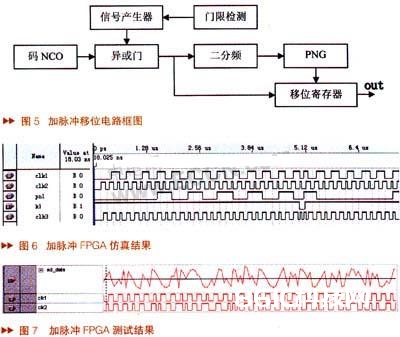

如图1所示,当信号包络的平方小于门限时,输出操控信号,对图2中CLK取反,取反的成果相当于运用原CLK时钟下降沿进行触发。经过二分频后作为伪码发生器的时钟,一起把CLK作为移位寄存器的时钟,三位移位寄存器的输出相当于移动了半个码片。FPGA仿真成果如图3所示。

图中data1,data2,data3,分别为三位移位寄存器的输出,01表明+1,11表明1,clk1为码NCO的输出,clk2为它的二分频。此办法在整个体系中要屡次对时钟进行取反操作,会带来比较严重的时序问题,使体系作业时序满意不了。为了处理此问题,可选用改善的办法。

捕获办法2 (滑动步进为TC/2)

时钟取反法改善:

此办法选用触发器结构,把2倍的CLK作为输入,CLK作为使能端,运用FPGA自带的IP核–锁相环使CLK相位超前,包住2倍CLK的上升沿,触发器的输出即为CLK,FPGA仿真成果如图4所示。图中,co为输入端,pn为锁相环的输出作为使能端。对使能端取反操作,经过图2的电路结构即可完结半码片的移动。可是,一起要对二分之一CLK进行锁相操作,假如完结多路,因为FPGA内部只要2个锁相环,所以,有用性受到限制。

捕获办法3 (滑动步进为TC/2)

加脉冲移位法:

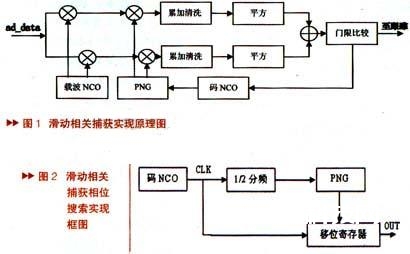

此办法是选用一个异或门,如图5所示,使码NCO的输出CLK与一个信号异或输出,此信号往常一向为高(或低)电平,一旦收到低于门限值时,输出一个低(或高)脉冲,与CLK异或后,相当于在原CLK时钟上加了一个脉冲,经过图示的电路后,伪码发生器前进了半个相位,经过移位寄存器后,即可完结半个码相位的移动(超前半个码片)。

FPGA仿真成果如图6所示。图中CLK1为码NCO的输出,CLK2为它的二分频作为伪码发生器的时钟,pn1为伪码发生器输出,k1为信号,往常输出高电平,当门限检测成果为低时,输出一个低脉冲与CLK1异或输出,成果为CLK3。从仿真图中能够看出CLK3相关于CLK2在k1为低脉冲时,增加了一个脉冲。

下载到FPGA中,运用SIGNALTAP,测验成果如图7所示。图中CLK1为码NCO输出时钟,CLK2为异或门的输出,从图中能够看出,在门限检测为低时,CLK2比CLK1多增加了一个脉冲,测验成果与仿真成果共同。

完结成果

经过以上的剖析,再结合扩频通讯的有关理论,能够知道要完结信号的捕获,有必要经过载波和伪码相位的二维查找。首要,对接纳的信号进行数字下变频,变为零中频I、Q两路信号,再与本地PN码进行解扩运算。成果与门限值比较,假如小于门限则依照前面剖析的办法次序移动半个码片,直到包络的平方大于门限转入盯梢状况。捕获电路如图1所示。

选用上述办法,在实践中对某一扩频信号进行捕获

信号参数

中频40MHz ;

调制款式为DS-BPSK;

伪码长度为1024;

数据率5Kb/s;

采样时钟60MHz;

各个模块功用描绘

数字下变频:

载波NCO的输出与输入信号在乘法器中进行数字下变频,功用是去除输入信号载频而保留了用于基带相关的码。

数字相关器:

累加铲除器的作用是对经过数字正交下变频后的I、Q两路信号与本地再生伪码相乘的成果进行积分累加。选用的是一个累加器对数字混频后输入信号与本地码相乘的每一位成果进行累加。经过必定时刻(本方案为12000次)的积分累积后,得到一个数据位的相关值。此相关值与预设门限比较,进行捕获判定。假如小于门限,则以为捕获失利,铲除累加结,滑动半个码片后,从头进行累加积分。累加清洗器进行一个码周期的数据累加,输出一次相关累加值。最大的捕获时刻为0.4094秒(0.2mS*2047)。

载波NCO:

载波NCO是载波盯梢环的重要组成部分,它的主要功用是发生本地仿制载波信号。载波NCO模块设置有频率操控字输入接口,模块内部经过32位相位累加其对输入操控字进行累加,取得相位值的映射地址,经过查表取得正余弦两路信号。载波环路经过不断调整载波NCO的频率字来坚持对接纳信号载波频率和相位的盯梢。

码NCO:

码NCO是码盯梢环的中心。它的主要功用是为再生伪码发生器供给准确的时钟信号,确保完结对接纳信号的码捕获和盯梢。码NCO设置有频率操控字,频率操控字担任码率的调整和码相位延时。

完结成果

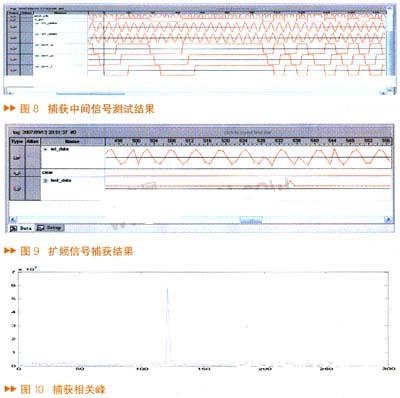

A/D选用AD9288-100,是8位的转化成果,最高作业频率可到达100M,数字下变频和捕获电路在EP1C12Q240C8(Cyclong)中完结,运算的中心测验成果如图8所示,图中pn2_clk为NCO输出时钟,x_pn为伪码,c1_data和s1_data为载波NCO发生的用于下变频的I、Q路载波信号。pn_e、pn_p、pn_l分别为移位寄存器输出的超前、即时和滞后码,它们相差半个码片。

最终的捕获成果如图9所示。图中ad_data为接纳的数字中频信号,last_data为最终捕获的成果。

保存数据,在Matlab中的相关成果如图10所示。

结束语

加脉冲法能够使本地码相位超前半个码片相位,完结非接连相位滑动相关,电路结构简略,在FPGA中简略完结,是一种简略有用的办法,在实践体系规划中已被选用并取得了抱负的成果。