第二章 FPGA根本教程

第一节 FPGA的根本开发流程

PLD是可编程逻辑器材(Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field Programable Gate Array)的简称,两者的功用根本相同,仅仅完结原理略有不同,所以咱们有时能够疏忽这两者的差异,统称为可编程逻辑器材或PLD/FPGA。

PLD是电子规划范畴中最具生机和开展前途的一项技能,它的影响一点点不亚于70年代单片机的创造和运用。

PLD能做什么呢?能够毫不夸大的讲,PLD能完结任何数字器材的功用,上至高性能CPU,下至简略的74电路,都能够用PLD来完结。PLD好像一张白纸或是一堆积木,工程师能够通过传统的原理图输入法,或是硬件描绘言语自在的规划一个数字体系。通过软件仿真,咱们能够事前验证规划的正确性。在PCB完结今后,还能够运用PLD的在线修正才干,随时修正规划而不必改动硬件电路。运用PLD来开发数字电路,能够大大缩短规划时刻,削减PCB面积,前进体系的可靠性。 PLD的这些长处使得PLD技能在90年代今后得到飞速的开展,一起也大大推动了EDA软件和硬件描绘言语(HDL)的前进。

怎么运用PLD呢?其实PLD的运用很简略,学习PLD比学习单片机要简略的多,有数字电路根底,会运用计算机,就能够进行PLD的开发。

开发PLD需求了解两个部分:1.PLD开发软件 2.PLD自身

因为PLD软件现已开展的适当完善,用户乃至能够不必详细了解PLD的内部结构,也能够用自己了解的办法:如原理图输入或HDL言语来完结适当优异的PLD规划。所以对初学者,首先应了解PLD开发软件和开发流程。了解PLD的内部结构,将有助于前进咱们规划的功率和可靠性。

下面咱们以依据Altera公司的QuantusII软件来简略阐明一下FPGA的开发流程。

下图是一个典型的依据QuantusII的FPGA开发流程。

(1)树立工程是每个开发进程的开端,QuantusII(以下简称Q2)以工程为单元对规划进程进行办理。

(2)树立顶层图。能够这样了解,顶层图是一个容器,将整个工程的各个模块容纳在里边,编译的时分就将这些模块整合在一起。也能够了解为它是一个大元件,包括各个模块,编译的时分便是生成一个这样的大元件。

(3)选用ALTERA公司供给的LPM功用模块。Q2软件环境里包括了很多的常用功用模块,例如计数器、累加器、比较器、译码器等等;假如不懂得在工程中选用这些现有的功用模块真是太浪费了。以自己的经历,一个规划中一般只要很少部分的模块需求自己从零规划。

(4)自己树立功用模块。当然,有些规划中现有的模块功用不能满意详细规划的要求,那就只能自己规划啦。能够用硬件描绘言语也能够用原理图的输入办法。能够把它们独立地当作一个工程来规划,并生成模块符号(Symbol),然后在顶层图中运用这个模块的符号,并将源文件(完结该模块的原理图或HDL文件)拷到顶层图地点的工程目录下。这个进程比方你要做一个电路,现在市面上没有你想要的某个芯片,你就只能自己做一块这样的一块芯片,然后增加到你的电路板上。

(5)将顶层图的各个功用模块用连线连起来。这个进程相似电路图规划,把各个芯片连接起来,组成电路体系。

(6)体系的功用原理图至此现已根本出炉了,下一步要为该规划挑选芯片载体,才干真正在物理上完结体系的功用。这一步的首要作业是:(1)挑选芯片类型;(2)为顶层图的各个输入输出信号分配芯片的管脚;(3)设置编译选项,意图是让编译器知道更多的信息。

(7)编译。这个进程相似软件开发里的编译,但实践上这个进程比软件的编译要杂乱得多,因为它究竟终究要完结硬件里的物理结构,包括了优化逻辑的组合、归纳逻辑以及布线等进程。在相似Q2这样的集成环境里边,这些进程都能够趁热打铁,集成环境帮你主动完结了几个进程的作业。当然,你也能够用其它东西来完结各个进程的作业,这些内容超出了本教程陈说的规模。

(8)编译后会生成*.sof或*.pof文件,前者能够通过JTAG下载到FPGA内部,规划无误的话即能完结预期的功用,但断电后FPGA里的这些信息会丢掉;后者能够下载到FPGA的装备芯片(EEPROM或FLASH芯片),掉电后这些装备信息不会丢掉,从头上电今后通过该装备芯片对FPGA的内部RAM进行装备。

(9)关于杂乱的规划,工程编译了今后能够选用Q2的仿真功用或其它仿真软件(如ModelSim)对规划重复进行仿真和验证,直到满意要求。

第二节 依据QuartusII的实例

试验一 试验板上的KEY1按钮操控FPGA中心板上的第一个LED灯。

本试验比较简略,运用本站FPGA开发板或许CPLD开发板以及其它FPGA开发板都可进行试验。

意图:通过该实例学习,能够了解FPGA的根本开发流程,熟识quartusII软件根本功用的运用。

原理:运用一个常开按钮(试验板上的KEY1)作为输入(常开时输入1,闭合时输入0),通过一个反相器后输出到中心板的第一个LED。KEY1常开时,LED亮,按下(闭合)试验板上的KEY1,该LED平息。

1. 树立工程

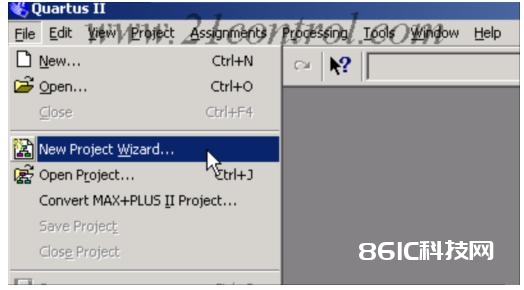

运转QuatrusII软件(以下简称Q2),树立工程,FileàNew Project Wizad如

点击New Project Wizard 后弹出指定工程名的对话框,在Diectory, Name, Top-Level Entity中如下图填写:

按Next按钮,呈现增加工程文件的对话框:

在这儿咱们先不必管它,直接按Next进行下一步,挑选FPGA器材的类型:

在Family下拉筐中,咱们挑选Cyclone系列FPGA,然后在“Available devices:”中依据中心板的FPGA类型挑选FPGA类型,留意在Filters一栏选上“Show Advanced Devices”以显现一切的器材类型。履行下一步呈现对话框:

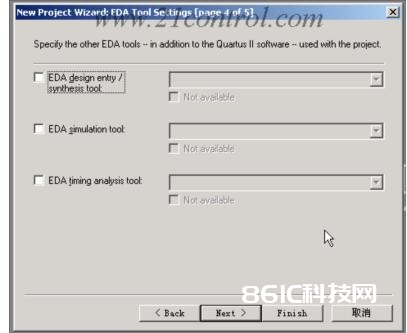

这儿是挑选其它EDA东西的对话框,咱们用Q2的集成环境进行开发,因而这儿不作任何改动。按Next进入工程的信息总概对话框:

按Finish按钮即树立一个空项目。

2. 树立顶层图

履行FileàNew,弹出新建文件对话框:

挑选“Block Diagram Schematic File”按OK即树立一个空的顶层图,缺省名为“Block1.bdf”,咱们把它另存为(FileàSave as),承受默许的文件名,并将“Add file to current project”选项选上,以使该文件增加到工程中去。如图所示:

3. 增加逻辑元件(Symbol)

双击顶层图图纸的空白处,弹出增加元件的对话筐:

在Libraries里寻觅所需求的逻辑元件,假如知道逻辑元件的称号的话,也能够直接在Name一栏敲入姓名,右边的预览图即可显现元件的外观,按OK后鼠标周围即拖着一个元件符号,在图纸上点击左键,元件即安放在图纸上。

在图纸上别离增加非门(not)、输入(input)、输出(output)三个symbol,如图所示:

连线,将鼠标移到symbol连线端口的那里,鼠标变成图示容貌: ,按下左键拖动鼠标到另一个symbol的连线端。本例中,这三个symbol的连线如下图所示:

别离双击input和output symbol的姓名“pin_name”、“pin_name1”,将它们的姓名改为Key1,LED1:

4. 分配管脚

为芯片分配管脚能够用QuartusII软件里的“AssignmentsàPins”菜单,也能够用tcl脚本文件。用Tcl文件进行装备可重用性好,易于办理,因而本文介绍用tcl的办法。关于另一种办法,能够参阅QuartusII软件的协助文档。

在工程目录下树立一个name为Setup.tcl的file。FileàNew,挑选other files页面:

有关tcl文件的更翔实内容可参阅QuartusII的协助文档,关于咱们所选用的FPGA开发板SOPC开发板来说,因为不同类型的FPGA中心板的管脚与试验板上的引脚也不同,因而不同的中心板对应的.tcl文件也不同(关于中心板引脚与试验板引脚对应的详细情况请参照“CT-SOPCx学习套件用户手册”或相关电路原理图)。在实践项目中,该文件也能够依据详细管脚分配要求来改写。

对应于EP1C6 FPGA开发板,EP1C12 FPGA开发板:

#Setup.tcl

# Setup pin setting

set_global_assignment -name RESERVE_ALL_UNUSED_PINS AS INPUT TRI-STATED

set_global_assignment -name ENABLE_INIT_DONE_OUTPUT OFF

set_location_assignment PIN_1 -to led1

set_location_assignment PIN_122 -to key1

保存到工程目录下,并留意在保存对话框选上“Add file to current project”选项。然后翻开Tools -> Tcl Scripts,选中方才修改的Script文件:Setup,并点击Run,如下图:

留意:树立工程时假如路径名有中文字符或许路径名有空格字符,则tcl Script文件将运转不了。比方,本例树立的工程“FPGA_led_test”目录是: C:alteraquartus51myq2projectsFPGA_led_test

假如是:

C:alteraquartus51my q2projectsFPGA_led_test

在该目录下运转工程里的setup.tcl就会犯错。

假如运用Tools -> Tcl Scripts 后没有弹出“tcl Script”对话框能够试一下关了QII,再从头翻开。运用TCL文件分配管脚是很便利的,用户能够直接从相关比如工程中仿制需求管脚分配表到自己的工程中,省时又便利。