导言

本文从实践运用的视点动身,选用FPGA作为主控芯片,规划了一款数字视频接口转化设备,该设备针对于MT9M111这款数字图画传感器发生的ITU-R BT.656格局数据进行收集、颜色空间改换、分辨率转化等操作,完结了从ITU-R BT.656格局数据到DVI格局数据的转化,使得MT9M111数字图画传感器的BT656数据格局图画可以以1280×960(60Hz)和1280×1024(60Hz)两种显现格局在DVI-I接口的显现器上显现,而且还具有图画停止功用,在体系空闲时的待机状况完结了整机的低功耗,适用于运用移动设备的工业现场。

全体计划规划

实际景象的收集与显现进程如图1所示。图画传感器MT9M111收集到实际景象后,将生成的ITU-R BT.656数据流由ITU数据输出端口发送给视频转化接口。视频转化接口将ITU数据输入端口送来的ITU-R BT.656数据流转化成TMDS数据流发送,经过DVI-I端口发送给显现终端显现。本规划计划中,MT9M111输出图画的分辨率为1280×960。

图1 体系收集与显现进程

在实际景象的收集与显现进程中,视频转化接口功用的完结经过以下进程来完结:

1) 对收到的ITU-R BT.ITU656数据流解交错;

2) 对解交错后的数据流进行颜色空间转化;

3) 将转化后的每个像素的RGB值写入存储器中;

4) 从存储器中读出像素的RGB值,并将其转化成TMDS码元序列;

5) 从存储器中读出像素的RGB值,并将其转化成VGA模仿信号值。

硬件构架规划

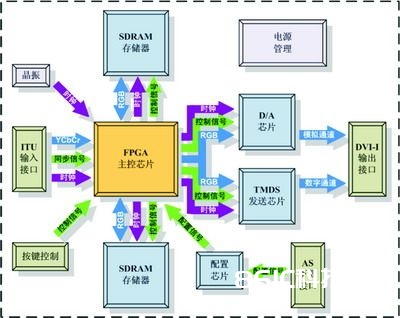

体系的硬件构架框图如图2所示。图画传感器输出的ITU信号(包含YCbCr数据流、行场同步信号和像素时钟)经ITU输入接口送入FPGA主控芯片。FPGA主控芯片对ITU信号进行解交错和颜色空间转化,再将转化后的每个像素的RGB值写入SDRAM存储器。再由FPGA主控芯片依照输出分辨率的要求从SDRAM存储器中读出像素的RGB值,并依照VGA的时序规范,将像素的RGB值发送给TMDS发送芯片和D/A芯片,由TMDS发送芯片供给视频数据的数字通道,由D/A芯片供给视频数据的模仿通道,一起聚集到DVI-I输出接口,传送到数字显现器或模仿显现器上显现。

图2 硬件构架框图

输出图画的分辨率要求FPGA与TMDS发送芯片之间传送数据的带宽在100M(像素/秒)以上,因而要求FPGA的速度足够快。一起因为FPGA与外围器材之间的互联比较多,因而要求FPGA的引脚数足够多。一起因为晶振供给的时钟频率为50MHz,满意不了100M以上的传输速度,因而需求FPGA内部带有锁相环。别的,为了完结体系脱机作业,要求FPGA支撑装备芯片。终究,考虑到体系占用的面积和今后版别的晋级,要求FPGA的内部资源尽量丰厚。为此,体系终究选用了Altera公司Cyclone系列FPGA。

考虑到视频数据的存储和显现是一起进行的,而SDRAM存储器是单端口器材,数据的写入和读出不能一起进行,故需求两块SDRAM一起进行乒乓操作来完结数据的接连读写。终究选用了MICron公司的类型为MT48LC2M32B2TG-6的SDRAM存储器;TMDS发送芯片选用的是Silicon Image公司的SiI164CT64类型。因为输出图画的分辨率要求FPGA与TMDS发送芯片之间传送数据的带宽在100M以上,这一数据流一起又要送入D/A芯片完结数模转化,因而要求D/A芯片的转化速率在100MHz以上。一起因为R、G、B的数据宽度都为8位,因而需求选用专用的图画D/A芯片,它需求具有R、G、B三路数据通道,每路的宽度至少为8位。依据以上要求,体系终究选定CSEM%&&&&&%公司的CSV7123类型的图画D/A芯片。

FPGA功用规划

FPGA作为体系的主控芯片,是软件规划的中心。依据全体计划的规划思路,FPGA主控芯片的作业进程为:首要接纳由图画传感器送来的ITU-R BT.656格局的视频数据流,经过解交错操作,将像素数据流中交错在一起的串行YCbCr值解成独立的并行YCbCr值。然后对解交错的YCbCr值进行颜色空间转化,转化成对应的RGB值。接着将此RGB值存入一块SDRAM存储器。与此一起,从另一块SDRAM存储器中读出像素的RGB值,并发送给TMDS发送芯片和D/A芯片,经过数字通道和模仿通道后,传送到DVI显现器或VGA显现器上显现。依据FPGA主控芯片的作业进程,规划的软件功用框图如图3所示。

图3 软件功用框图

图3中FPGA内部的作业时钟有两个,以图中的虚线为界,虚线左边部分运用的时钟为图画传感器的54MHz像素时钟;虚线右侧运用的时钟是经过锁相环将晶振的50MHz时钟倍频成108MHz今后的时钟,其间108MHz的时钟是由输出图画的分辨率所决议的。两个时钟域经过异步FIFO相连。整个体系共分红6个模块:解交错模块、YCbCr转RGB模块、异步FIFO模块、乒乓操作模块、SDRAM控制器模块和VGA发送模块。此外,体系还可完结图画停止、体系待机、形式挑选等功用。

图画显现作用

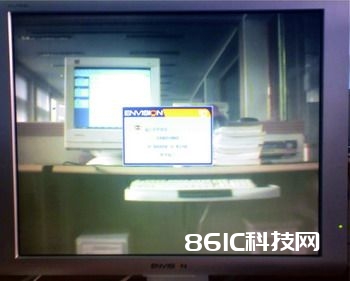

图4是输出图画分辨率为1280×960形式下的显现作用,图中显现器检测到的视频图画分辨率为1280×960

图4 1280×960形式下的显现作用