跟着集成电路规划和工艺技能的开展,嵌入式体系已经在PDA、机顶盒、手机等信息终端中被广泛运用。嵌入式体系具有电路尺度小、本钱低价、可靠性高、功耗低一级长处,是未来集成电路开展的方向。而作为嵌入式体系中心的微处理器,其功用直接影响整个体系的功用。为了进步CPU的功率和指令履行的并行性,现代微处理器广泛选用流水线规划,所以,CPU流水线的规划成为决议其功用的要害。

MIPS(Microprocessor without Interlocked Pipeline STages)是一种典型的RISC(Reduced InstructiON Set Computer)微处理器,在嵌入式体系领域中得到广泛的运用。MIPS32TM指令集敞开,指令格局规整,易于流水线规划,很多运用寄存器操作。与CISC(Complex Instruction Set Computer)微处理器比较,RISC具有规划更简略、规划周期更短等长处,并能够运用更多先进的技能,开发更快的下一代处理器。

1 依据MIPS指令集的CPU流水线结构

1.1 指令集的选取

规划完结了指令兼容MIPS系列RISC处理器的指令集。因为MIPS32TM指令集是敞开的指令集,指令格局十分简略,依照指令格局可分为寄存器类型(R-type)指令、当即数类型(I-type)指令和跳转类型(J-type)指令。这三类指令均为32 bit,并且指令操作码在固定的方位上。这种特色易于指令代码的拆分,易于流水线CPU的规划。

指令类型参阅MIPS处理器的指令集规划准则。一切指令的运算都在寄存器中进行,当需求与内存交流数据时,通过内存拜访指令进行内存和寄存器的数据交流。规划完结程序中常常运用的34条指令,完结指令集依照功用分红5种类型:算术运算类指令、逻辑运算类指令、数据传送指令、条件搬运和无条件跳转类指令、特别指令等。

1.2 流水线的规划

在根本的MIPS处理器中有5个流水级,其间各流水级界说与首要功用为:IF为核算下一条指令的地址PC,并从指令存储器读取指令;ID为对指令进行译码,从寄存器堆中取出源操作数;EX为当指令是运算类指令时履行运算,当指令是搬运类指令时进行有用地址核算;MEM为从数据存储器读写数据;WB为将数据写回到寄存器堆。依照这一流水线结构,本文规划完结一种较为通用的MIPS CPU,通过VHDL言语完结,各模块之的联系如图1所示。

2 嵌入式CPU流水线中的相关性

因为指令以流水线方法并行处理,必产生指令相关性问题,一般存在三种相关:结构相关、数据相关和操控相关,引起流水线竞赛。

结构相关问题是指因为硬件资源缺乏而导致流水线不疏通,例如只要一个存储器模块时,就不能对存储器一起取指令和数据。数据相关问题是指一条指令的后续指令要运用该条指令的成果。而操控相关问题是指搬运指令从取指到转向方针地址要花几个时钟周期,但流水线CPU在每个周期都取指令。

处理结构相关问题的办法是尽量添加硬件电路资源,本规划选用哈佛架构,运用指令存储器和数据存储器防止结构竞赛。关于寄存器组存在的结构竞赛,选用由D-FF构建寄存器予以防止,当写入地址和读出地址相一起,直接用写入数据驱动读出总线。数据相关问题能够用数据前推技能得到缓解。数据前推技能关于ALU核算指令十分有用,但关于存储器读数据指令,假如下面的指令想当即运用其成果,则有必要暂停流水线一个周期。至于操控相关,能够运用指令重组优化及推迟搬运技能等软件编译办法处理。

3 要害模块的完结

3.1 ALU的完结

ALU是数据通路中的重要部件,担任完结各种运算功用。依据CPU要完结的指令集,确认出ALU的操作操控信号数据宽度为5 bit,运算的数据位数为32 bit。操作操控信号(ALU_OP)和ALU的源数据挑选信号依据不同指令的译码由操控逻辑产生。

3.2 操控单元的规划

操控单元要依据输入的指令码产生一系列的操控信号,用于操控数据通路上的多路挑选器和各功用部件,确保每一条指令都能够正确履行。

操控单元的输入信号有必要规划为32 bit的指令码,而输出信号则要依据需求进行规划。

在IF阶段,操控单元需求依据指令的译码状况,决议PC的更新值,假如是次序履行的指令,则PC主动加4,关于分支和跳转指令,需求宣布跳转指令信号和分支指令信号,然后决议PC的更新值。

在ID阶段,操控单元对指令进行译码,依据指令的操作码和功用部分,宣布相应的操控信号;依据指令中的操作数字段,操控单元给出寄存器号,从寄存器堆中读出操作数送入ID与EXE之间的流水线寄存器。假如产生数据相关,数据前置逻辑产生前置操控信号。

在EXE阶段,操控单元给出ALU数据来历的挑选信号,以及ALU的运算挑选信号,

在MEM阶段,操控单元需求给出数据存储器的读写信号,片选信号等。存储器需求向操控单元回来呼应信号。

在WB阶段,操控单元首要操控数据的流向,给出多路挑选器的挑选信号,挑选将存储器读出的数据或ALU的运算成果写回寄存器组。

3.3 数据前推技能的规划

关于数据竞赛的检测,通过比较接连3条指令的寄存器标号,把本条指令的rs和rt及前面2条指令的操作数成果寄存器别离进行比较,比较器的输出信号传递到EXE阶段用于挑选ALU操作数的来历。

而关于LOAD指令产生的数据相关,有必要比及MEM阶段完结之后才干得到有用的数据,因而产生数据相关的下一条指令,只能通过推迟一个周期才干运用数据前置技能,假如合作MIPS编译器,通过运用推迟槽技能能够处理LOAD类型的数据相关。

3.4 指令cache的完结

体系完结了一个容量为2 KB指令Cache,每个Cache行为16 B数据,这样能够运用存储器的16 B的突发式传送。选用2路组相联方法,支撑通写(Write Through)形式。由同步SRAM完结。

数据Cache由操控模块、射中与缺失比较模块、拜访内存模块、替换模块、输出模块组成。其间操控模块是整个Cache的主控部件,它操控存储器和cache和谐作业:当履行单元有取指恳求时,以指令的物理地址作为索引看是否射中,假如不射中则操控逻辑发动访存逻辑到内存中去取指,当指令取回时操控逻辑发动替换逻辑对指令Cache进行替换并将指令输出;假如射中,则将指令输出。

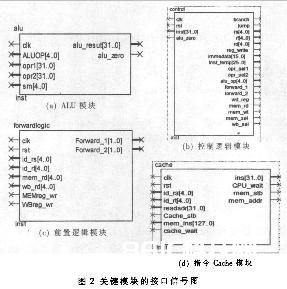

运用VHDL来规划和完结上述各要害模块。归纳后的接口信号图如图2所示。

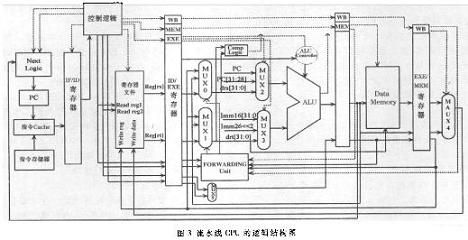

对要害模块和其他模块进行交融,最终得到的CPU流水线结构图如3所示。

4 体系的仿真与验证

运用VHDL完结对各功用模块的规划,并完结功用仿真后,将规划的操控单元和数据通路的各模块进行兼并,构成一个完好的嵌入式RISC CPU核,进行体系级仿真。依据体系完结的指令集编写了一个简略的测验程序。

add $5.$0,$0

addi $7,$0,1

sw $7,10($5)

lw $8,10($5)

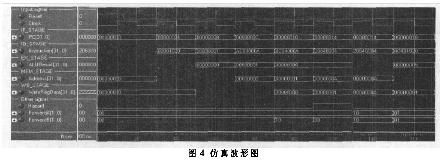

将指令码写入指令存储器的仿真文件,测验程序运转得到的仿真波形图如图4所示。

每个时钟周期为10 ns,第一个时钟周期T1从10 ns处开端,依据仿真波形能够看出,在T5周期,指令sw $7,10($5)处于EXE阶段,第二条指令addi $7,$0,1处于MEM阶段,需求进行数据前推,Forward_2的值为”10”,通过对测验成果剖析能够看出,数据前推成功。通过剖析仿真波形图中各个输出信号的波形,依据程序的运转进程,能够判别信号波形正确,到达规划要求。

本文给出了流水线CPU的要害模块的VHDL完结,通过逻辑归纳和仿真,仿真成果表明在时序上规划的嵌入式CPU很好地满意了流水线的要求。生成位流数据文件对FPGA进行器材编程,FPGA芯片能够在50 MHz的时钟频率下安稳的运转。