导言

跟着核算机、微电子和嵌入式体系技能的开展,数据收集技能现已在生物医学、图画处理、雷达体系等许多范畴得到广泛运用。本文规划的高速数据收集体系是运用于芯片现场测验的实时数据收集体系,因为被测验芯片为250 MHz 8 bit的高速AD输出, 因而, 该数据收集体系的数据收集率是2 Gbps。为了到达实时、高速、海量的数据收集, 该体系运用DDR2 SDRAM的高速数据传输才能和海量存储才能做为收集数据的缓存,然后经过具有即插即用、易扩展、传输速率较高级特色的USB2.0接口来将DDR2 SDRAM中的数据传输到核算机中进行存储和剖析。

1 数据收集体系架构

该数据收集体系的整体架构由硬件部分、固件部分和核算机上的USB驱动及运用程序等几大部分组成, 本文完结了硬件和固件部分的规划。

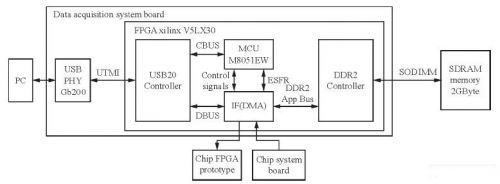

该体系的硬件部分首要由USB2.0、DDR2SDRAM、MCU以及IF等中心模块组成, 图1所示是其体系架构图。

图1 体系整体架构图

USB2.0由操控器和物理传输层组成, 其间操控器是在FPGA上完结的Faraday公司的IP核,物理层可选用SMSC公司的GT3200芯片, 操控器与物理层芯片之间可经过规范的UTMI接口相连。

DDR2 SDRAM操控器是依据Xilinx公司供给的IP核, 作业频率是125~266 MHz, 与SDRAM之间的接口是64 bit SODIMM笔记本内存条接口。作为数据存储的SDRAM 是Samsung 公司的M470T5663QZ3-CE6 2GB 内存条。体系的操控中心MCU选用Mentor Graphics公司的增强型8051 IP核M8051EW,该8051核选用两个时钟周期为一个机器周期的高功用架构, 一起支撑MWAIT信号来操控程序总线,然后可以支撑慢速的外部程序和数据存储器。IF模块是该体系规划的要害, 它相当于DMA的功用,首要担任USB与DDR2、外部数据接口与DDR2之间的数据传输。

2 数据收集体系规划

本文中的数据收集体系选用USB2.0和DDR2SDRAM相结合的规划思路,然后打破了传统数据收集体系在实时数据收集中大容量和高速率不行兼得的瓶颈。在图1所示的体系架构的四个部分中,因为USB2.0和DDR2操控器都是IP核, 因而, 该体系规划的要害在于MCU和IF模块。

2.1 MCU的规划

MCU是数据收集体系的操控中心, 首要用于对USB2.0操控器进行装备、查询和处理USB业务, 以及解析USB设备恳求, 一起,还需装备IF模块, 处理与IF模块之间的操控信号等, 因而,MCU的规划包含数据接口及操控信号的规划以及固件规划两个部分。

MCU数据总线接口包含与USB2.0操控器和与IF模块的接口,这儿的USB2.0操控器和IF模块相当于外部设备挂在MCU的外部存储器总线和ESFR(外部特别功用寄存器) 总线上。操控信号首要用于核算机上的操控台操控IF模块数据传输的开端与完毕, 一般包含在USB的设备恳求中。

整个固件的开发可在Keil C下完结, 并可经过JTAG进行调试。开发一般包含三部分: 一是帮忙USB操控器完结总线罗列进程,让核算机辨认USB设备; 二是经过解析自定义USB设备恳求,来对收集形式、深度等进行装备, 然后操控收集的开端与完毕;三是查询和处理IN、OUT业务中止, 并操控USB数据传输。

2.2 IF模块规划

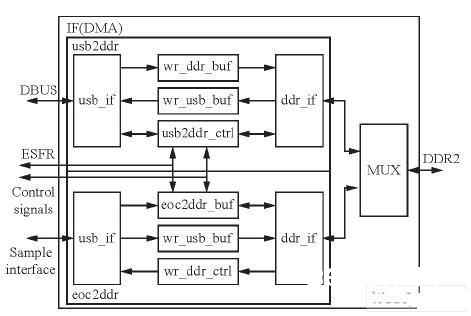

IF模块担任接口的转化和数据传输的操控,其结构如图2所示。其间, usb2ddr和eoc2ddr子模块别离操控USB2.0与DDR2 SDRAM、外部收集接口与DDR2 SDRAM之间数据的上下行传输。

上下行数据传输别离由usb2ddr_ctrl 和eoc2ddr_ctrl模块中的状况机进行操控和办理。其间收集形式和深度由MCU的ESFR总线装备,而传输开端信号则运用MCU的PORT0 [0]、PORT0[1], 完毕信号连接在MCU的外部中止NINT0和NINT1上,这样可使MCU可以及时呼应。上行收集开端后, 首要使eoc2ddr_ctrl中的操控状况机处于写状况,并不断地比较DDR2的地址与装备深度, 直到收集完结。然后再使usb2ddr_ctrl中的操控状况机处于读状况,相同也比较地址与深度,直到数据读取完结。下行传输进程则与之相反。

图2 IF模块结构框图。

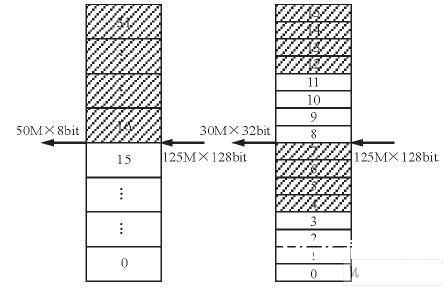

因为各个接口上数据传输的速率不同, 因而, 数据传输时, 要异步FIFO或许缓存。在本规划中, 因为各接口速率固定, 因而,可选用双端口RAM作乒乓缓存办法以进步功率并确保数据接连, 图3所示是乒乓缓存原理图。

图3 乒乓缓存原理图。

当下行宣布数据时, 从DDR2的125 M×128bit到50 M×8 bit所需求的最小深度为32×8 bit,因为从SDRAM中读数据的最大推迟是26个DDR2时钟周期(即208 ns), 而将DDR2读出的128 bit宣布则需求16个时钟周期(即320 ns), 因而, 为了确保宣布的数据可接连进行乒乓操作, 需求2×128bit的深度。同理,在上行数据从DDR2的125 M×128 bit到USB的30 M×32 bit则需求4×128 bit深度,因为USB时钟读完128 bit数据需求133.2 ns, 小于SDRAM 读数据推迟的208 ns, 因而, 每次从SDRAM中读2×128 bit数据时,其乒乓操作就至少需求4×128 bit深度。

3 体系的改善

本数据收集体系对传统的数据收集体系做了创新式改善。改善首要是三个方面: 一是对数据收集的深度实施可装备形式;二是在功用上不只作为数据收集体系, 还能作为数据发生器, 行将收集到核算机上的数据经过数据收集体系发送出来;三是该数据收集体系有两种作业形式, 即一般收集形式和触发收集形式。

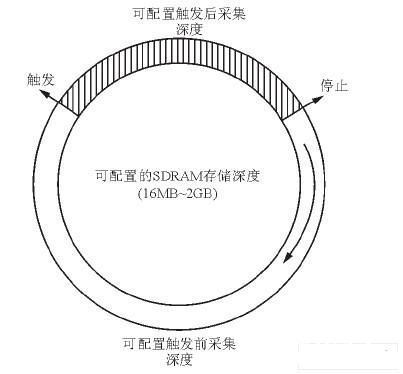

深度可装备添加了体系在运用进程中的灵活性。该体系除了收集数据外, 还能将数据宣布来用于芯片的FPGA原型验证,然后避免了缓慢的大数据量仿真, 更增强了体系的实用性。经过ESFR装备8 bit的深度寄存器可完结以16 MByte为单位的深度调理。触发是数据收集体系不行短少的功用, 因而,该数据收集体系分为一般收集形式和触发收集形式。触发收集形式的原理如图4所示。在触发形式中, 可将SDRAM看做一个圆形的循环存储器,触发前后的收集深度相同也可以经过ESFR装备, 然后完结触发前后的收集深度份额可调。

图4 触发完结机制原理图。

4 FPGA完结

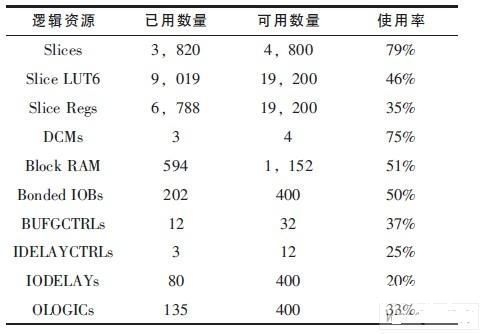

FPGA在体系规划中具有很好的灵活性和可扩展性, 因而, FPGA是一个十分好的体系完结渠道。经过对数据收集体系的资源*估,可得出如表1所列的资源占用成果。

表1 FPGA的资源占用状况。

本体系终究挑选了Xilinx 公司的FPGA器材Virtex5 LX30。因为DDR2 SDRAM操控器是Xilinx公司的IP核, 故在体系的集成和完结进程中不行避免的要对原IP核进行改动, 一起,在ISE中布局布线时, 相应地要对原有UCF文件中的束缚进行修正, 以满意时序要求。本体系除USB2.0的PHY和SDRAM外,其余部分均由FPGA完结, 图5所示是体系在核算机上的操作界面和实物图。

图5 操作界面和FPGA实物图。

5 完毕语

本文结合USB2.0与DDR2 SDRAM的特色, 给出了可打破一般数据收集体系在实时、高速和大容量数据收集上的瓶颈的办法,而且在实用性方面进行了改善。该体系终究可在FPGA上完结,因为用FPGA完结具有极大的灵活性和可扩展性,而且在体系规划本钱和快速完结上具有很好的竞赛优势。现在,该数据收集体系在实践运用中作用杰出。实践上, 若对收集接口稍加改善, 并将IF模块中的乒乓缓存改为异步FIFO,就能广泛地运用于各类高速体系的实时数据收集。

须留意的是,时钟速率与传输延时并没有什么关系,乃至一般的100bps时钟也会呈现颤动问题。这意味着尽管FPGA供货商声称他们的芯片具有较短的传输时刻和很高的时钟速率,但颤动问题或许会严峻,乃至那些没有运转在最高速率上的规划也是如此。

好在FPGA供货商现已认识到时钟颤动的影响,并在他们的芯片中供给低颤动的布线资源。这些特别的布线可以在芯片中一个给定范围内的任何两个触发器之间供给一个确认的最大颤动。部分产品的低颤动资源覆盖了整个芯片,而其它的则或许只覆盖了FPGA逻辑块中的一个特定的行或列。关于一个需求许多不一起钟源的规划,这些低颤动FPGA是比较抱负的挑选。

多时钟规划的最严峻问题之一是用异步时钟将两级逻辑结合在一起。因为异步时钟会发生亚稳态,然后严峻下降规划功用,或彻底损坏规划所能完结的功用。在触发器的时序要求发生抵触时(设置时刻和坚持时刻)将发生亚稳态,触发器的终究输出是不知道的,并使整个规划处于不确认状况。假如有一级逻辑要将数据异步地发送到另一级,图3所示的景象将不能满意触发器的设置和坚持时刻要求。切当地说,假如规划中含有异步逻辑将有或许会发生亚稳态。在处置异步资源时必需十分当心,因为这或许发生一些很严峻的问题。

多时钟规划

本文以电信运用中的E3多路复用/解复用规划为例。如图4所示,多路复用器接纳来自一组独立线路接口芯片的16个独立E1信道,每一个信道都作业于2.048MHz;经复用后,这些E1流组合成4个E2流,别离作业在8.0448MHz;4个E2流终究组合成一个E3流,以34.368Mbps的速率串行发送出去。在接纳端履行相反的操作:解复用器从E3流提取4个E2数据流,然后从E2流提取16个E1流,终究将E1流发送到接纳端的线路接口芯片。

这些E1线路接口在发送和接纳时都独立作业,因而2.048MHz的时钟速率可以有+/- 20ppm的误差。相同,因为大多数体系一起发送和接纳数据,分立的多路复用器和多路解复用器将供给2个独立的E3流(发送和接纳)。因而,两个34.368MHz的时钟可以存在纤细的差异。

因为E2流是在芯片上发生的,这些E2多路复用器可以同享同一个8.448MHz时钟。可是,因为接纳的数据速率与咱们所规划的板无关(且不能假定一切E2多路复用器运用相一起钟),所以E2解复用器时钟有必要能作业在略为不同的速率下。

此外,假定规划中需求一个由作业频率为1MHz的处理器操控的独立SPI(串行外围接口)总线接口,该接口用于状况和操控。这样一来,规划中一共用了32个2.048MHz时钟,5个8.448MHz时钟,2个34.368MHz时钟和一个1MHz时钟,一共多达40个时钟。

本规划中最快时钟是34.368MHz E3时钟。FPGA的最大时钟速率的确认很重要,因为规划的差异将影响到该最大值。可是,在芯片商的材料手册中常常可以看到“大局时钟设置及坚持时刻”和“至CLB输出的时钟”两个参数,将这两个参数的最大值相加,再添加25%就能可以得到最小时钟周期的初略值,在最大时钟速率条件下答应10%的余量,以确保过热条件下能正常作业。因而,咱们设置的最小速率为40MHz,许多较新的FPGA都可以很简略地支撑该频率。事实上,FPGA供货商现已推出了超越300MHz的器材。

在确认了能满意最大频率要求的FPGA后,就需求确保有满意的空间来完结你的规划。假如所选的FPGA没有满意的余量,就不能供给满意的布线资源来满意规划的时序束缚。一般芯片供货商声称的速率是最佳条件下的速率,FPGA供货商一般主张FPGA逻辑在布线功用开端显着变差曾经可以用到80%。在挑选FPGA器材时,主张在新的规划时最好使FPGA逻辑用到50%左右,这样就答应核算开始规划巨细呈现超差,以及为在规划起动后发生不行避免的规划变更留出空间。假如终究的规划只占用低于50%的资源,则可以运用同一系列中较小的FPGA以下降本钱。

经过时序束缚来规则慢时钟速率,然后可以改善规划中最快时钟的布线。在多路复用器比如中,假如设置FPGA布线东西SPI总线时钟为1MHz,而E3时钟为40MHz,布线东西将尽量使E3时钟的逻辑电路模块相邻布局。假如因为空间的约束而不能将悉数电路布局在一起,则首要应将SPI逻辑别的布局,因为SPI逻辑可以处理更长传输推迟。一切FPGA供货商的布线东西都能规则这些较慢时钟速率。

削减时钟数量

依据市场调查,现在还没有哪个FPGA器材可以支撑这种多路复用器/解复用器规划所需的40个时钟。所以,咱们有必要削减所需求的时钟数。

首要了解E2和E3多路复用器的时钟。前面现已剖析了4个E2多路复用器作业在相一起钟下的可接受度,E3多路复用器运转于比E2时钟高得多的速率,必需运用一个不同的时钟。可是,假如咱们从E3时钟中引出E2时钟是否可行呢?因为E3多路复用器要从每个E2支路得到数据,咱们可以在需求E2多路复用器给咱们数据时,简略地将脉冲送给每个多路复用器。咱们没有去掉任何时钟,但E2时钟现在是依据E3时钟。

假如在一切的多路复用器中也运用相同的时钟,而且只运用一个使能信号来告知E2多路复用器什么时候作业,这时会发生什么问题呢?假如E3多路复用器用34.368MHz时钟发生使能信号,在这些使能信号上的颤动不会比用在FPGA中任何其它同步逻辑更大。所以,使能信号可以运用正常(高颤动)布线资源,这样就不需求独自的8.448MHz多路复用器时钟,读取E1数据缓冲器的数据时也是相同。换言之,假如E2多路复用器需求数据,它可以激活到特定缓冲器的使能信号。到缓冲器的时钟自身可以坚持E3多路复用器所用的34.368MHz时钟,如图5所示。

终究,咱们查看16个从线路接口芯片输入到FPGA的E1时钟。这些时钟有会发生下面几个问题:首要,16个时钟将占用太多可用芯片时钟布线资源;其次,在同一个FPGA中运用16个异步时钟来驱动彼此附近的触发器,因为地弹、串扰和其它效应将发生噪声问题。例如,因为噪声的原因,一个正边缘触发器会在下降边缘时改动输出状况,此类问题将难以处理。