运用SOPC强壮的IP核和简单装备的优势简化规划流程。充分发挥NiosⅡ强壮的并行处理才干。该体系首要触及多个下位机与FPGA的通讯问题。

1. 功用描绘

1.1 全体规划思路

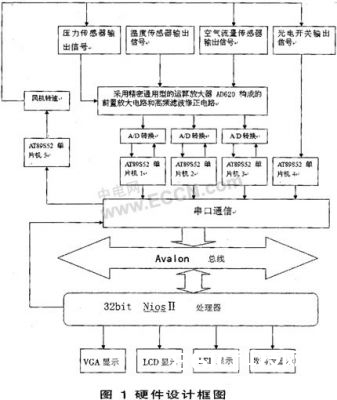

运用SOPC强壮的IP核和简单装备的优势简化规划流程。充分发挥NiosⅡ强壮的并行处理才干。该体系首要触及多个下位机与FPGA的通讯问题。通过SOPC规划技能能够很简单的结构多个UART接口,下降体系的规划本钱。在Quartus中能够用VHDL/Verilog言语写入总线复用模块,处理SRAM、SDRAM、FLASH之间存在的总线抵触问题。

显现和操作部分的硬件首要在Altera的CycloneⅡEPSC35板上由SOPC Builder装备完结。传感检测和信号处理部分则通过体系扩展来完结。特别是扩大和A/D转化部分,有必要由专门的模块来处理。

1.2 体系的首要功用

旋风预热器仿真首要完结对水泥回转窑模型在模仿作业状况下的参数检测和操控。由传感器收集的数据通过扩大和批改送入A/D转化芯片,转化后的数据送入作为下位机的AT89S52系列单片机中,通过串口通讯的办法将数据流送入作为上位机的DE2开发板中,运用NiosⅡ软核的VGA视频显现功用将收集的数据显现为状况曲线。

一起,运用FPGA快速反应的长处,完结对下位机部分的操控,然后对模型的模仿作业状况进行调整和监控。整个旋风筒模型由通明的有机玻璃构成,具有很强的观赏性。LED灯的提示和LCD的数字显现愈加提高了全体的实用性。因为体系的各个单元之间存在独立性,因而,本体系能够做为教育上的演示模型。传感器的用法,A/D的用法,扩大的原理以及通讯和FPGA的运用都能够独立的用来作为教育模型。在旋风筒模型上预留了各成120度的三维丈量孔,装入传感器后能够一起在X、Y、Z三维场中检测,完结同一参数的三维丈量。因而,该体系在科研方面也具有很大的实用性。

2. 体系模块概述

本体系首要由检测单元、信号扩大批改单元、串口通讯单元、显现单元组成。各个部分通过单片机和FPGA之间的通讯联系在一起。构成一个完好的集检测、通讯、显现、操控为一体的体系。本体系只丈量模仿作业下一维场中的状况参数。风机的操控运用专用的晶闸管智能操控模块,直接由0~5V电压操控输出0~220V的风机电源电压。

计划的硬件规划框图如图1所示。

3. 模块功用描绘

3.1 显现单元

整个处理进程便是对四路传感器所收集的实时数据进行分时显现。通过按键操作VGA,让四路参数状况的曲线能够分屏显现。显现屏选用一般的PC机显现器,显现像素为480640。当榜首路数据流通过串口通讯送入上位机后,软核处理器将该组数据流敏捷进行暂存,按键操作VGA显现函数挑选屏数并调用这部分数据在显现屏上顺次点亮对应的像素点,然后能够将整个数据流所对应的状况曲线动态的显现在屏幕上,到达可视化的监控作用。

在榜首屏进行画线显现的一起,处理器将持续对各路参数的数据流进行接纳和缓存。按键操作进入第二屏后,开端对第二个参数状况进行画线和实时数值描绘,四路状况曲线悉数画完完毕回来。 在这个进程中,处理器一起调用字符液晶显现和数码管的显现函数,对当时数据的平均值和瞬时值进行精确的数值描绘。LED用于提示当时分屏显现的屏数,即提示现在收集的参数类型。按键用于操控风机转速。显现单元的体系软件规划框图如图2

3.2 检测单元

因为传感器的输出电压改变都是在毫伏级,因而有必要由安稳的扩大和滤波电路将收集信号进行扩大和批改,到达能够满意数据传输的电平要求和线性要求。通过扩大的信号送入A/D转化芯片中,将模仿信号转化成数字信号后再由单片机送入NiosⅡ中。

旋风筒模仿作业时,分别由传感器将温度、风机转速、气压、气体流量等参数值进行收集。温度选用高精度的铂热敏电阻丈量。气压和空气流量选用由Honeywell公司出产的专用检测传感器进行丈量。风机转速通过单片机对光电开关开合发生的脉冲进行计数然后予以确认。传感器将收集的信号通过扩大批改单元的处理后直接送给单片机。四路信号选用一起收集,分时传送的办法发送给上位机。在NiosⅡ对榜首路送入的数据开端进行显现处理,一起将第二路数据送入。

3.3 通讯单元

选用串口多机通讯的办法。在多路数据传送办法上,能够挑选485通讯的办法。多路下位机一起挂在485的通讯输出端,分时的传送数据。可是这种办法如果有传送速度上的要求则有很大的坏处,传送速度会比较慢。本体系充分发挥CycloneⅡ处理器能够定制多个UART的强壮功用,完结上位机对多路数据的一起接纳和处理。在速度上要比485的办法要快。然后完结对模仿环境的敏捷监控。下位机选用AT89S52系列单片机,相同支撑串行通讯。因为通讯间隔比较近,为了防止资源的糟蹋,不主张选用RS232或485的串行通讯办法。在往后的体系扩展上能够将232通讯增加进去。

检测和通讯单元的体系软件规划流程如图3

4. 软件规划

4.1 根据Nios IDE的软件规划

由SOPC Builder构建成的硬件体系首要有必要下载到FPGA中,在FPGA上生成对应外设的引脚,然后才干够通过IDE烧程序给外设,使外设能够正常的运转。也便是说对主程序部分有必要要在IDE形式下进行调试,这是整个进程中感觉功率比较低的当地,每次修正的程序都有必要通过再次运转Run As Hardware从头编译才干写入硬件中,形成调试进展很慢。程序能够在SRAM或SDRAM上运转。

为了确保断电后数据不丢掉,选用FLASH Programmer把数据写入FLASH,然后把CPU的ResetAddress地址指向FLASH。通电后体系会主动对FPGA进行装备,并运转内部程序。该部分的程序首要是设置多个串口通讯的时序以及VGA显现的内容。程序流程图如图4所示。

5. 成果剖析

通过检测和调试,体系的全体功用完全能够正常完结。体系选用Nios软核结合可编程逻辑阵列对旋风预热器的仿真模型的模仿作业状况进行检测和操控。完结了多线程的串口通讯和VGA的显现,充分发挥了FPGA快速呼应的实用性特色和支撑CPU操作的强壮功用。运用SOPC Builder能够便利的对体系的扩展部分和自定义部分进行增加和删去,根据需要开发自己的IP核优化体系。充分运用SOPC的特色来缩短规划和开发周期。

运用SOPC Builder装备了四个串口来完结这一要求,而这一特别用法却是其它处理器如单片机,ARAM等无法完结的。