本文介绍了一种选用PLD和数据通路(datapath)来解放微操控器体系中CPU使命的计划。在大多数微操控器结构中,智能的CPU身边总会环绕着一系列不行编程的外设。外设的功用有限,一般它们只担任数据方式的转化。例如,I2C外设仅仅完结串行和并行数据格式之间的转化,而ADC则完结模仿到数字信号的转化。CPU因而不得不完结一切的数据处理工作,实际上它还能做些更有用的工作。此外,办理外设将会导致CPU固件反常杂乱,并或许需求一个快速高效的CPU在实时的时序约束下履行这些固件。这又会导致更多的潜在程序缝隙,然后需求运用更杂乱和贵重的调试设备等。

可是假如外设具有满足的杂乱度、灵敏度与智能,是否能有用地减轻CPU的许多使命呢?杂乱的规划能够经过结构重建,变为一组散布在CPU和外设中心的简略规划。CPU将能够履行更少的使命,或进行更少的中止处理,然后使程序缝隙更简略被发现和批改。全体规划将使体系具有更好的安稳性,而且便于复用部分规划。CPU处理使命削减就能够运转在较低的速度,然后下降功耗,或许这些额定可用带宽可用来完结市场部规划的下一代产品。可是,外设规划仍需具本钱效益,不然整个微操控器或许变得太贵。本文将展现怎么把智能、灵敏、低本钱、可定制的数字外围设备规划到微操控器并装备,以协助完结安稳的散布式体系规划。

智能逻辑挑选—PLD仍是数据通路?

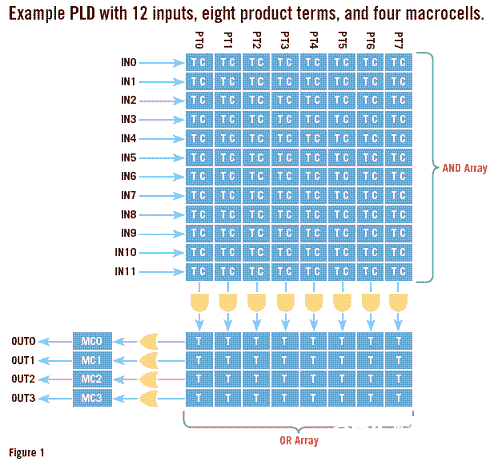

一般有两种办法构建一个智能的可装备外设。首先是运用PLD。如图1所示,PLD有一个驱动若干宏单元的积和(sum of products)逻辑门阵列。“T”和“C”符号标明每一个乘积项都能发生一个真值或补数(反向)输出,这样无论是正、负逻辑都能够支撑。

图1:一个PLD实例(包含12个输出项、8个乘积项、4个宏单元)。

图1显现了一个简略的PLD比如。PLD能够有成百上千的宏单元,每个宏单元最高由16个乘积项驱动。乘积项里的与门和或门能够互联构成高度灵敏的定制逻辑功用。宏单元是典型的时钟架构,它们的输出能够反应到乘积项阵列,因而答应创立状况机。

大规模PLD能够用来构成杂乱的逻辑功用,乃至是彻底的CPU,因而PLD当然能够用来完结智能数字外设。可是,许多门或许仅仅完结比如计数器或加法器等简略的逻辑功用,但关于更杂乱功用的完结,依据PLD的计划就会变得很贵。从某种程度上说,运用真实的CPU会更合理。

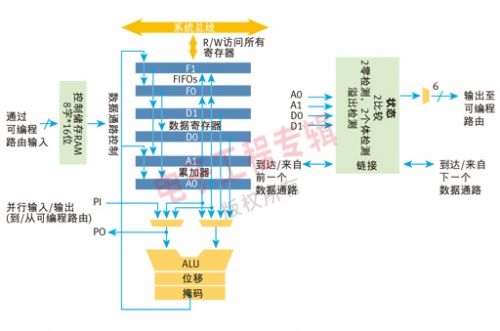

CPU的一个十分简略的方式是依据算术逻辑单元(ALU)的数据通路,也称为纳米处理器(nano-processor)。数据通路仅仅完结几个常用函数,但会比运用PLD完结的功率更高。图2:显现了一个依据ALU的简略的数据通路。典型的ALU能够进行各种操作,一般是8位操作:向上计数(递加)、向下计数(递减)、加、减、逻辑与、逻辑或、逻辑异或,左位移、右位移。这里有两个8位累加器,它们能够为ALU输出充任输入数据寄存器或存储器。一个输入时钟信号沿发生一次操作。函数挑选寄存器用来操控:

图2:依据ALU的数据通路。

* 发生什么操作。

* 该操作的源寄存器。

* 输出的意图寄存器。

依据数据通路的详细规划,其或许会做一系列杂乱操作,如表1显现。

表1:数据通路函数的完结举例。

这个函数挑选模块实际上能够是一个小容量的SRAM,预加载所需的函数挑选位,SRAM的地址线能够用来挑选运转哪个操作。最终,多数据通路能够用进位和移位信号链在一起,以便能够进行多字节操作数。

由于数据通路只要少量特定功用函数,很简略优化规划,因而其创立本钱较低。可是,关于完结杂乱的逻辑,数据通路远远没有PLD那么灵敏。那么,关于创立智能、灵敏、低本钱的数字外设来说,哪一种办法是更好的呢?是PLD仍是数据通路?答案是,将两者相结合。下面是一个实例,来看看是怎么完结的。

通用数字模块

一起运用PLD和数据通路的体系实例是赛普拉斯半导体的PSoC3和PSoC5芯片。每个别系包含最高24个通用数字逻辑子体系,称为通用数字模块(UDB),其结构如图3所示。一个UDB包含两个图1所示的PLD,一个数据通路以及状况机和操控寄存器。有两个链路途径,一个用于PLD,一个用于数据通路。由一个路由通道来衔接各UDB子块之间以及UDB之间的信号。PLD装备、数据通路和路由经过写入UDB装备寄存器来完结。

UDB的PLD规划在图1中进行了描绘。如图4,UDB数据通路类似于图2所示的根本的数据通路,可是它更精细杂乱,由于具有更多寄存器和更多的功用。

图4:UDB数据通路框图。

* 8位ALU能够完结一切的七个根本函数—递加、递减、加、减、与、或以及异或,而且它有独自的位移和位掩码模块来进行ALU成果后处理(8位ALU传输功用只需经过ALU传送一个值到位移和位掩码模块)。位移模块能够做左位移、右位移、半字节交流和传输。掩码模块能够和独自的掩码寄存器里的内容逐位相与(图中未显现)。

* 操作能够运用两个累加器(A0,A1)和两个数据寄存器(D0,D1)来完结。两个FIFO寄存器(F0、F1)可用来在数据通路和CPU之间传输数据。FIFO深度可达4字节。这一结构能够使多使命处理变得简略;在不同的时刻,独立操作能够在寄存器子集完结。例如,A0、D0、F0能够用于一个使命,而A1、D1、F1则可用于不同的使命。

* 广泛的状况条件(例如:比较、零检测、一切个别检测、溢出检测)能够运用到累加器,数据寄存器,以及路由到器材其它当地。

灵敏的路由

尽管UDB在PLD和数据通路两个子体系都有许多特征,但广泛的数字路由让它们如虎添翼。信号能够在PLD和数据通路之间路由,广泛整个UDB和器材的其它当地,构成了杂乱的数字体系互连(DSI)结构。

实例

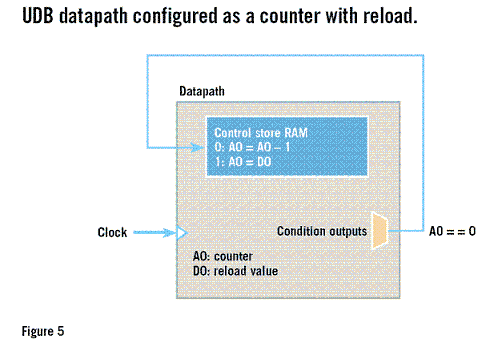

本例中,用一个UDB数据通路来创立一个带重载(reload)功用的8位数字计数器。为了完结这点,衔接一个状况条件回到操控存贮SRAM地址线,如图5所示。

图5:用UDB数据通路创立带重载功用的计数器。

在这个规划中,A0是计数寄存器,D0是重载寄存器。需求两个函数,一个用来递减计数,一个从周期寄存器重载计数器;这些函数在操控贮存RAM里预载了。

逻辑如下:当A0不为0时,状况输出将会变低,在地址0会履行递减操作。当A0为0时,状况输出将为高,在地址1会履行重载操作。

一切操作都发生在时钟输入的上升沿,能够记载时钟沿数量。时钟输入能够来自各种时钟源。状况输出能够经过DSI路由,包含到DMA和中止请求输入。运用数据通路链和掩码模块,该计数器的巨细能够是任何位数,不受限于8的倍数。

图5所示为减法计数器。它能够很简略的转化成加法计数器,能够经过运用不同的状况输出(A0= =D0)和操控存储SRAM里的不同函数:A0=A0+1和A0=A0A0。异或任何值的成果永远为0。

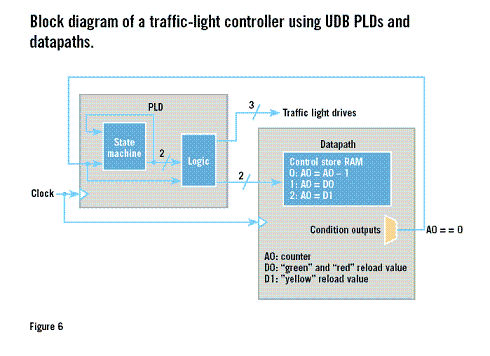

经过运用PLD这个简略的规划能够发明更杂乱的运用。以一个红绿灯操控器为例,红绿灯操控器周期由绿、黄、红三种状况构成,因而需求一个状况机。每个状况改动到下一个状况之前会继续必定时刻,所以必需有一个计数器。为了简略起见,假定“绿灯”时刻和“红灯”是相同,但“黄灯”时刻不同。

只需求运用3个数据通路寄存器(假定为8位计数值)就能够完结这个时序结构。A0为计数寄存器,D0为“绿”和“红”状况坚持计数器重载值,D1为“黄”状况坚持计数器重载值。模块框图如图6显现。

图6:选用UDB PLD和数据通路构建的红绿灯操控器框图

要保存在操控存储RAM里的操作是:

A0 = A0 – 1 // 计数

A0 = D0 // 重载“绿”或“红”

// 计数值

A0 = D1 //重载“黄”值

状况机在PLD里完结。数据通路条件输出反应到PLD,以标明需求改动状况了。PLD也有这样的逻辑,依据当时的状况和从数据通路反应的信号,操控履行哪个数据通路操作和哪个灯要点亮。

逾越根底

红绿灯操控器是一种简略的运用类型,一般运用CPU编程。可是,咱们现已看到,除了初始化代码,这个功用能够彻底和CPU不要紧而能够由智能的可装备外设完结。这个功用能够很简略地扩展以支撑附加需求,例如转化信号、行人行走信号、车辆检测传感器、流量/紧急事件转发器。

CPU需求做什么

经过运用PLD和数据通路的有用组合,能够创立智能的、灵敏的、低本钱的外设,以减轻CPU的担负。可是,假如这么多的功用都由外设处理了,那还藏着CPU做什么呢?在许多情况下,CPU不需求做许多事,在某些情况下体系初始化后,CPU就能够关掉了。不过,更有用的计划是运用CPU做CPU能做得最好的工作,例如:

* 杂乱的核算

* 字符串和文本处理

* 数据库办理

* 通讯办理

* 体系办理

例如,在咱们的红绿灯运用中,CPU能够用于以下几个方面:

* 检测车辆闯红灯

* 运用相机拍照车牌

* 从相片上提取车牌文字信息

* 从国家数据库中查阅车主信息,以及向车主发送罚单

经过由智能外设完结许多使命,CPU能够轻松地去做更有价值的使命。