跟着现代军事通讯技能的前进,数字化短波电台逐渐往嵌入式、模块化的方向开展。CPCI总线作为一种新式的总线技能,在短波电台的模块化规划上具有重要的运用价值,能够较大程度地进步数字化短波电台的牢靠性和保证性。

CPCI总线架构

CPCI标准是由PICMG(PCI Industrial Computer Manufacturer’s Group,PCI工业计算机制造商联盟)拟定的一种新的敞开工业计算机标准,用于工业和嵌入式运用。它界说了愈加坚固耐用的PCI版别,在电气、逻辑和软件功用等方面,与PCI标准彻底兼容。

CPCI全称Compact PCI,简略的说便是PCI specification(PCI电气标准)加上rugged Eurocard packaging(欧式卡)结构。CPCI模块以插卡的方法安装在机箱内的支架上,并选用笔直方向通风散热,具有更好的散热性和抗轰动性。这样,在CPCI体系中就可选用在台式机中广泛运用的高功用PCI技能,降低了新技能的运用本钱,体系的全体功用得以进步。而且,依据PCI技能的丰厚软件东西,也使得用户在运用中愈加快捷。一起,欧式卡结构使得体系的牢靠性进一步进步。别的选用IEEE 1101.11后端输出方法,使得对体系的保护愈加方便快捷,大大缩短了体系的均匀保护时刻。

CPCI体系背板和CPCI板卡选用的是标准2mm高密度气密性针孔衔接器,板卡的尺度分3U(100mm×160mm)和6U(160mm×233mm)两种,3U的体系只供给32位/64位的PCI体系总线,6U的体系除了供给32位/64位的PCI体系总线外,还有多达315线的用户界说输入/输出线,十分适用于数字化短波电台的模块化规划运用。CPCI总线具有极高的功用,其主要特色是:

(1)具有地址数据多路复用的高功用32位或64位的同步总线。总线引脚数目和部件数量少(关于总线方针设备只要47根信号线,关于主设备最多只要49根信号线),降低了本钱及布线杂乱度。

(2)CPCI部分总线在33MHz总线时钟、32位数据通路时,可到达峰值132Mb/s的带宽;在33MHz总线时钟,64位数据通路时可到达峰值264Mb/s的带宽;在66MHz主频时,关于32位数据通路和64位数据通路带宽的峰值,可别离到达264Mb/s或528Mb/s的带宽;CPCI总线还有线性突发传输功用,保证了满载的高速传输。

(3)荫蔽的总线裁定,减小了裁定开支。

(4)极小的存取延时,选用总线多主控和异步数据搬运操作。

(5)CPCI供给的数据和地址奇偶校验功用,保证数据完整性和准确性。

(6)CPCI总线与CPU和时钟频率无关,它能支撑多个外设,设备间通过部分总线能够完结数据快速传递,然后很好地处理数据传输的瓶颈问题。

(7)对CPCI扩展卡及元件,能够主动装备,完结设备的即插即用。

从结构上看,CPCI总线的特色标明它是一种抱负的体系交流渠道的载体,能供给高传输带宽,一起能够保证数据完整性和准确性;能够支撑多外设,很好地习惯了体系可扩展性的要求;选用的是PCI总线操作规程,很好地习惯了一般的PCI扩展元件,降低了开发难度;共同的引脚及外围电路规划集衔接严密结实、抗搅扰、易替换、热插拔等长处于一身。背板是CPCI总线架构的根底,它为CPCI总线交流供给物理衔接、电路保证。CPCI背板有8个插槽,其间一个为体系板插槽(system slot),其他7个为外设板插槽(peripheral slot),像这样一个体系插槽外带7个外设插槽的单元称为一个CPCI段(CPCI segment)。体系插槽供给总线裁定、时钟分配和整个CPCI段的重新启动等功用,体系插槽要通过办理每块外设插槽上板卡的IDSEL信号来完结整个体系的初始化;外设插槽上能够安放简略的接口板、智能隶属设备(intelligence slave)或PCI总线操控设备(PCI master)。

CPCI总线接口规划

为了进步数字化短波电台的数据处理才能,能够为其装备ETX嵌入式计算机模块。虽然ETX嵌入式计算机模块界说了契合PCI标准的CPCI总线,但由于如上所述的电气负载的原因,关于PCI/CPCI总线而言,假如总线上衔接过多的电气负载或设备,总线将不能正常作业。在不扩大总线的情况下,标准PCI总线的驱动才能是驱动4个PCI插槽,而CPCI操控器模块要求驱动7个仪器模块。因而,即便选用PCI插卡到CPCI插座的物理结构转化后,嵌入式计算机模块的PCI总线主桥路依然不能直接驱动CPCI总线。所以在规划数字化短波电台的CPCI总线时,需求在ETX嵌入式计算机的CPCI总线和CPCI机箱底板的CPCI总线之间引入了PCI-PCI桥接设备。

1 桥接芯片的挑选

PCI桥接芯片虽然能够运用FPGA通过硬件编程言语来完结,但由于PCI总线标准本身的杂乱性,要想在短期内做到功用优化和操作安稳,难度很大。而现在商场上有许多厂家供给了许多老练的产品,依据体系集成的特性,咱们挑选TI公司的PCI-to-PCI桥接芯片PCI2050。

PCI2050归于通明PCI-to-PCI桥,供给了两条PCI总线间的高功用衔接,完结一条PCI总线的主设备和别的一条PCI总线的从设备间的传输,兼容Intel 21150。PCI2050桥契合PCI部分总线标准2.2,并可用于PCI总线的扩展,供给支撑9个设备的可编程2优先级总线裁定器;一次侧和二次侧都支撑33MHz时钟、32位扩展信号。PCI2050供给CPCI热插拔才能,可完美处理多功用CPCI卡和单功用CPCI的热插拔问题。PCI2050桥契合PCI-to-PCI Bridge Specification1.1,契合PCI电源办理标准1.0/1.1。

2 电源和地的衔接

PCI2050运用的中心作业电压为+3.3V,CPCI标准机箱的底板上通过J1衔接器供给满意要求的+3.3V电压,在运用时无须DC/DC转化。但依据标准规划标准,在PCI2050的电源引脚邻近需求设置旁路电容。所以在印制电路板布线时,在PCI2050的一切电源引脚邻近需求设置一个0.1μF的陶瓷电容器作为旁路电容。

PCI2050在两边总线方向都支撑+5V和+3.3V信号环境,它们的挑选是通过对P_VCC和S_VCC引脚施加不同的电压来完结的,具体的挑选方法如表1所示。

由于PCI总线为高速总线,为了防止电源和地的搅扰,在印制板布线时采纳独自的电源层和地层布线。但由于在规划进程中运用了+5V和+3.3V两种电源,所以在同一电源层上又为+5V和+3.3V两部分分开铺铜。

3 PCI总线一次侧的衔接

数字化短波电台的嵌入式计算机模块供给了契合PCI总线标准的标准PCI信号接口,这些信号与PCI2050的榜首级总线侧的信号界说彻底兼容,在规划时能够将嵌入式计算机的PCI信号输出直接衔接到PCI2050一次侧的相应引脚。在初始化装备空间读写时,PCI2050作为上一级PCI总线的操作目标,供给了IDSEL引脚进行器材挑选,依照PCI2050运用手册,该引脚能够衔接到高24位PCI总线中的恣意一根。一起,为了减低地址线的容性负载,需求在该信号连线上串接一个1kΩ的电阻。

在CPCI总线规划中,将PCI2050的IDSEL引脚通过1kΩ电阻衔接到了AD19引脚。相同,PCI2050在二级总线侧能够支撑9个PCI器材,关于每个二级总线侧的PCI器材的IDSEL引脚,也能够通过1kΩ电阻衔接到PCI2050的S_AD31-S_AD16引脚中的恣意一根。

4 PCI总线二次侧的衔接

PCI总线信号通过桥接,在PCI2050的二级总线侧供给了标准的次级PCI总线接口信号,它们契合PCI总线标准的界说,同CPCI底板上的相应信号的界说也是相同的。但依据CPCI标准和PCI2050手册的要求,这些信号线需求通过恰当的调度后才能与相应的CPCI J1、J2衔接器的对应信号衔接。

① 依据CPCI标准的要求,为了减小单板上的CPCI总线的信号线分支(stub)对总线的影响,有必要对总线信号进行串联电阻匹配。PCB的布线特征阻抗应规划为65Ω±10%,匹配电阻阻值为10Ω。需求加串联匹配电阻的信号包括:AD0~AD31、C/BE0#~C/BE3#、PAR、FRAME#、IRDY#、TRDY#、STOP#、LOCK#、DEVSEL#、PERR#、SERR#、RST#以及INTA#、INTB#、INTC#、INTD#。而且,从接插件J1或J2到PCI2050相应管脚,总的信号线长度要小于63.5mm(2.5英寸)。其间,从接插件插针到串联电阻的PCB连线长度小于15.2mm(0.6英寸)。所以,对上述信号在实践中运用10Ω排阻作为端接终端电阻进行串联的匹配。

② 在CPCI总线的规划中,关于GNT#0~GNT#6、REQ#0~REQ#6和二级时钟输出SCLKOUT0~SCLKOUT6等引脚依据CPCI标准对体系卡的要求,也需求加上相应的10Ω端接终端电阻。

③ 依据标准要求,对CPCI总线接口来说,对体系卡的一些PCI信号输出需求进行上拉,且上拉电阻有必要被放置在端接终端电阻接近CPCI J1、J2衔接器的一侧上。能够在规划时对PCI2050的二级总线侧的相应信号通过8.2kΩ电阻上拉。需求上拉的电阻包括:FRAME#、IRDY#、TRDY#、STOP#、LOCK#、DEVSEL#、PERR#、SERR#、RST#、INTA#、INTB#、INTC#、INTD#、GNT#0~GNT#9、REQ#0~REQ#9等。

④ 关于二级时钟输出,PCI2050的二次侧有10个时钟输出S_CLKOUT[0..9],这些时钟输出能够通过相关寄存器别离使能。一起,为了保证PCI2050的二级PCI总线时钟和其他时钟输出同步,应将S_CLK引脚经一个75Ω电阻反应到S_CLKOUT9引脚,如图1所示。

图1 PCI2050的时钟衔接

⑤ PCI2050供给的JTAG鸿沟扫描接口TDI、TDO、TMS、TCLK、TRST#,这些引脚能够与CPCI标准界说的J1衔接器上的相应引脚直接衔接。

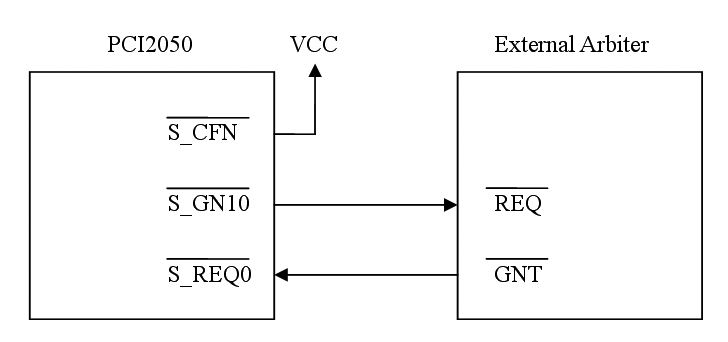

⑥ 关于二级总线的裁定,PCI2050供给两种方法:外部总线裁定和内部总线裁定。S_CFN#引脚为挑选引脚,当S_CFN#引脚为高时,运用外部总线裁定器。这时,S_REQ#1~S_REQ#8和S_GNT#1~S_GNT#8引脚被置为高阻状况,外部裁定器与PCI2050的衔接方法如图2所示。

图2 PCI2050与外部裁定器的衔接

在PCI2050的内部总线裁定形式中,S_CFN#引脚为低,PCI2050对外围卡通过S_REQ#0~S_REQ#8引脚提出的恳求进行裁定,然后通过S_GNT#0~S_GNT#8引脚和进行呼应。PCI2050的S_REQ#0~S_REQ#8和S_GNT#0~S_GNT#8引脚别离与CPCI标准界说的CPCI J1、J2的相应引脚通过串接端接电阻和上拉后衔接。

5 芯片作业形式的挑选

PCI2050能够挑选作业在三种不同的作业形式下:TI CPCI热插拔形式、TI电源办理形式和与Intel 21150兼容形式。挑选引脚别离为:MS0、MS1,形式挑选界说如表2所示。

TI CPCI热插拔形式支撑CPCI热插拔,满意CPCI电源办理接口标准1.1版别;TI电源办理形式不支撑CPCI热插拔,只满意CPCI电源办理接口标准1.1版别;与Intel 21150兼容形式也不支撑CPCI热插拔,且只满意CPCI电源办理接口标准1.0版别。依据CPCI总线运用规划的需求,能够挑选TI CPCI热插拔作业形式。

当PCI2050挑选作业在TI CPCI作业形式下时,为了保证热插拔逻辑的正常作业,要求有必要将PCI2050的HS_SWITCH/GPIO3和HSENUM#引脚上拉。一起,由于没有运用PCI2050的关于GPIO的引脚,且由于这些引脚在缺省条件下界说为输入脚,为了防止误触发,应该将这些引脚悉数上拉。

6 芯片内部寄存器设置

PCI2050桥接芯片作为一个独立功用的PCI器材,具有和一切PCI设备相同的装备空间,而且作为PCI桥,它恪守PCI-to-PCI桥标准1.1所界说的PCI装备空间。PCI2050除了具有标准的PCI-to-PCI桥标准界说的装备空间外,还具有TI特有的寄存器组(40h-FFh)。这些寄存器组包括PCI2050某些特有功用的操控位,在PCI2050的运用中起特别操控效果。但在本规划中,依据体系实践运用需求,对PCI2050的内部寄存器不需求进行特别操作,能够运用其缺省值。

定论

依据PCI2050桥接芯片的CPCI总线规划在数字化短波电台中的运用比较安稳牢靠,为数字化短波电台供给了丰厚的可插拔插槽。CPCI总线的标准化标准也为数字化短波电台的模块化规划和功用扩展供给了便当,而且还极大地进步了电台的可操作性、修理性和保证性,使数字化短波电台能更好地习惯各种杂乱的运用环境。