导言

跟着数字技能的快速开展,大容量数据存储成为商场急需的产品。NAND Flash作为一种非易失性存储器,容量 大、成本低,逐步遭到商场的喜爱,在现实生活中得到了广泛的使用。跟着NAND Flash 存储器容量的添加,犯错的可能性也在增大。这时需求用到BCH码,在中等码长的情况下,BCH具有纠错能力强、结构简略的特色,在实践中具有很广泛的使用。为了进步数据处理速率,本文提出8位并行

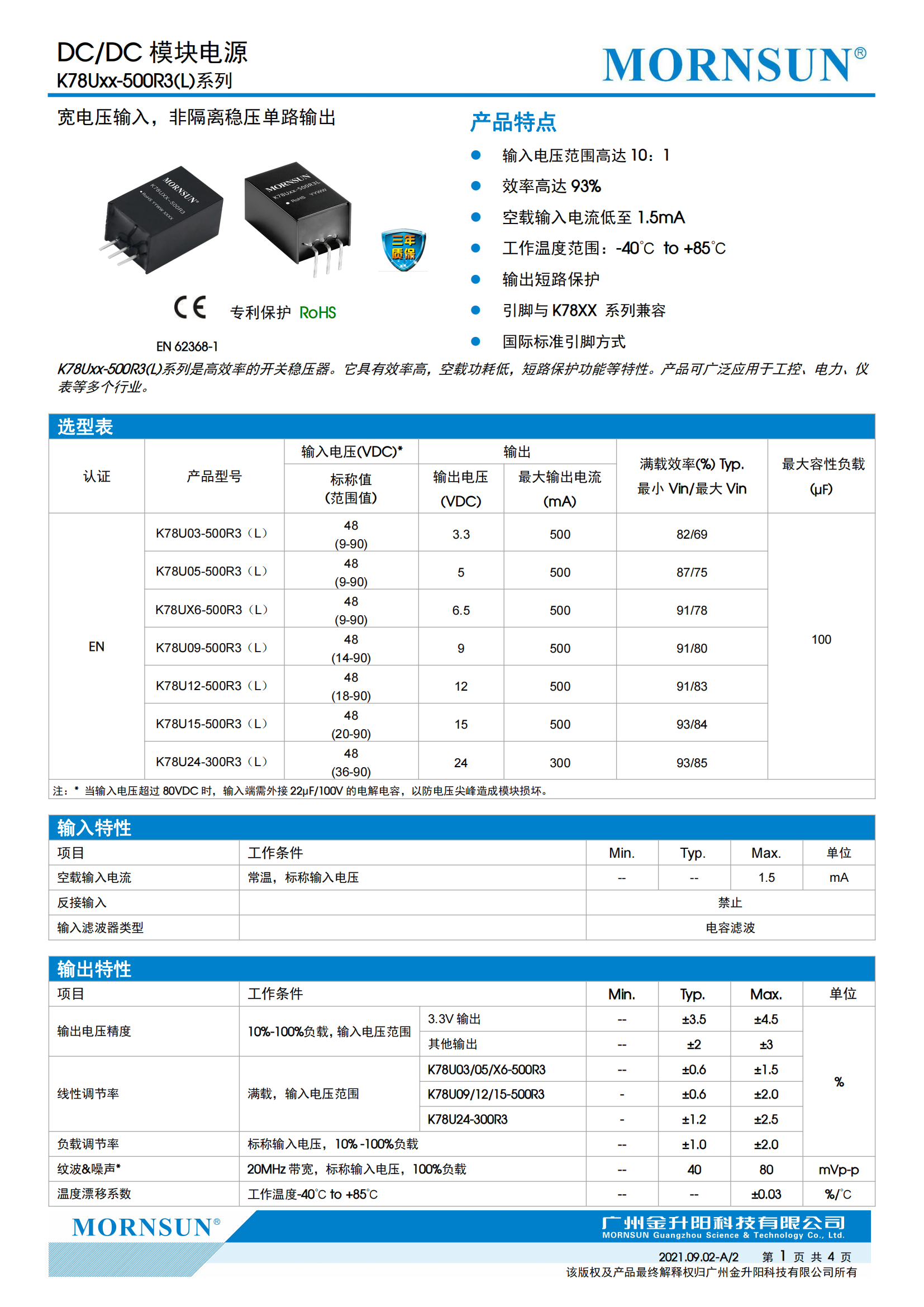

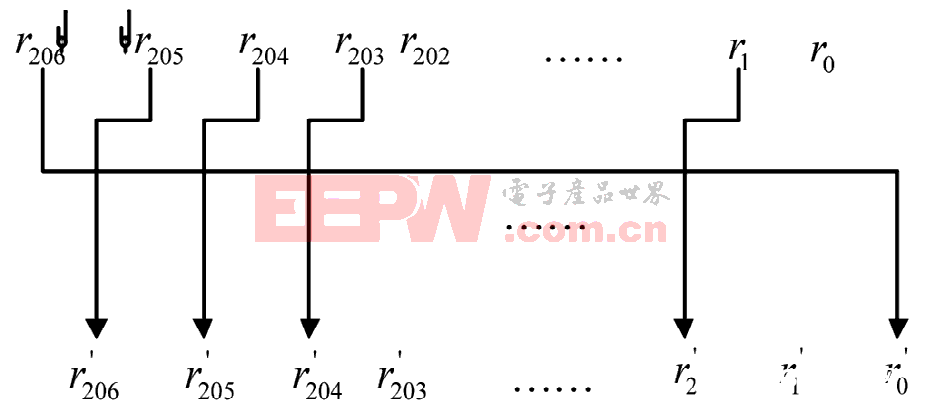

图1 BCH编码器结构

的编码结构、8位并行的随同式结构以及8位并行的钱氏查找 结构。

1 BCH编解码并行编码的进程

1.1 并行BCH(4304,4096,16)编码器的规划

本 文 设 计 的 B C H 码 是 ( 4 3 0 4 , 4 0 9 6 , 1 6 ) , 是 缩 短码 , 其 原 码为 ( 8 1 9 1 , 7 9 8 3 , 1 6 ) , 在 [ 1 ] 中 的 串 行 编 码算 法 的 基 础 上 进 行 了 改 进 , 设 计 成 8 位 并 行 的 结 构 ,对 于 B C H ( 4 3 0 4 , 4 0 9 6 , 1 6 ) 码 , L = 4304 / 8 = 538 , ,所以有:

,所以有:

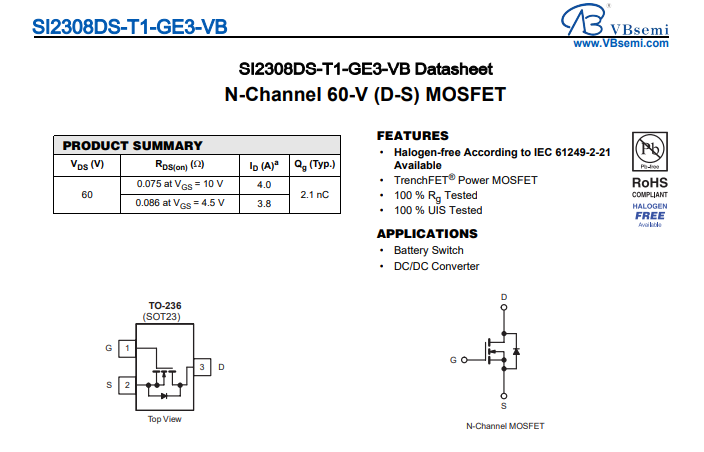

图2

2 BCH编解码并行 解码的进程

B C H 译 码 的 关 键 是 从 接 收 码 字 R(x) 中 找出 错 误 图 样 E(x) , 通 过 译 码 纠 正 后 得 到 发 送 端 发 送 的 码 子 C (x) 。

在 信 道 编 码 过 程 中 , 信息 经 过 信 道 后 会 增 加 一些 噪 声 干 扰 从 而 产 生 误 码 , 接 收 端 的 接 收 码 字 R(x) = C (x) + E(x) 。

BCH码的译码过程[2]:

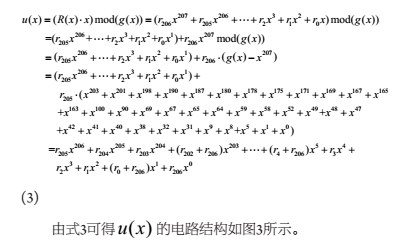

图3 u( x) 的电路结构

图4 解码器的流程图

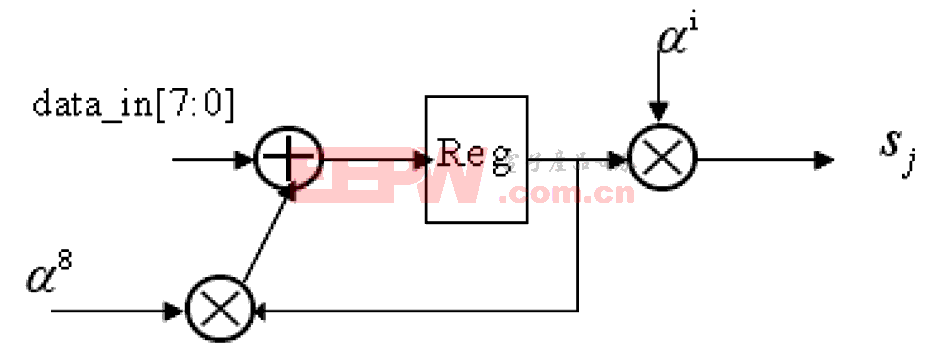

图5 随同式核算电路

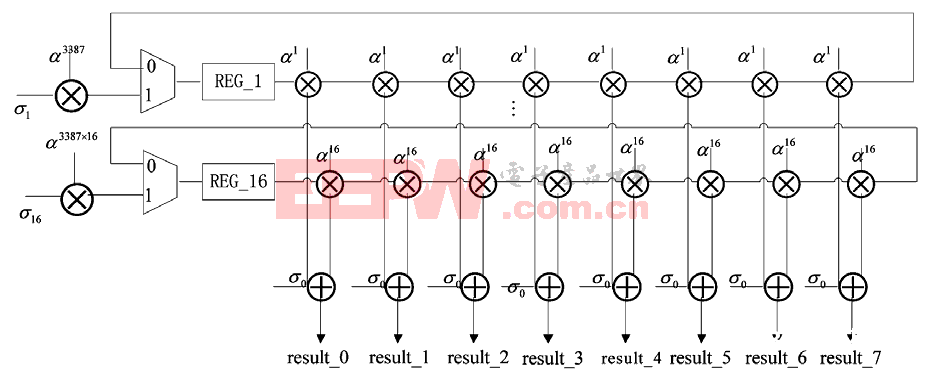

图6 并行钱氏查找电路

1)依据接纳码字 R(x) 核算随同式 S (x) ;

2)依据随同式 S (x) 求解要害方程,找犯过错图样 E(x)

即得犯过错方位多项式 ;

3)利用钱氏查找找犯过错方位;

4)依据过错方位进行过错纠正后译码输出。

其译码原理图如图4所示。

2.1 随同多项式的核算

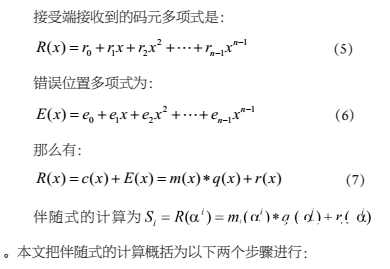

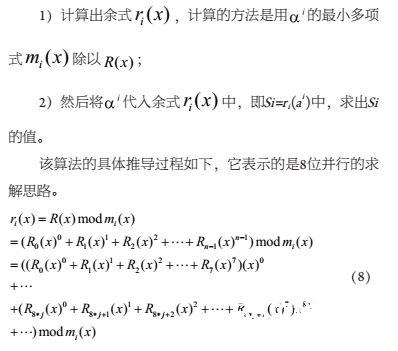

在[3]中随同值的求解是串行的,本文提出了一种8位并 行的结构,而且把随同式的求解分为两部分进行。

设体系端发送的码元多项式是:

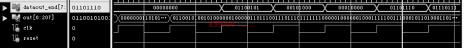

图7 编码电路仿真成果

图8 改错前的译码成果

图9 成心改错后的译码成果

电路结构如5所示。

在图5中, 分左右两部分, 左面用来求解随同式的余

式,寄存器是13位的寄存器,输入的是8位的接纳多项式的 系数。右边是一个有限域的常数乘法器,将余式的系数与伴 随式对应的根相乘得到随同式的值。(未完待续)