1 导言

现在跟着电子产品规划的日趋杂乱,测验内容也越来越杂乱,人们或许不只需求知道信号的时域特性,也想了解信号的频域特性,或许多域的联合特性也需求进行丈量。结果是,很或许在作业测验台上摆满了各种仪器:示波器、频谱仪……等等,作业空间遭到抢占,而且更重要的是测验作业变得杂乱,各种仪器的杂乱衔接,仪器间的同步问题需求处理……。因而,关于一般的调试丈量,人们期望能有一台多功用的仪器,既能满意时域测验的需求,又能进行频域的剖析,乃至时频域信号一同进行相参的联合调试,再乃至关于一些矢量信号也能进行剖析。示波器作为最根本的测验丈量仪器被广泛的运用,假如能融入这些剖析功用,将给工程师们带来极大的便当。现在,各示波器厂家也推出了一些多合一的示波器,技能也各不相同,不是别离的时域和频域通道丈量,便是选用软件核算的方法进行剖析,因而也面对一些问题。例如在频谱剖析时,咱们知道RBW(分辨率带宽)与信号的捕获时刻成反比联系,假如需求小的RBW(浅显说便是频谱看的更精密),那就需求更长捕获时刻,采样率必然会下降,那么关于高频的信号将无法进行剖析。相反,假如要对高频信号进行剖析,那么RBW将会较大,频率分辨率将会变弱。别的,在矢量信号剖析中,相同会遭到示波器存储空间和采样率的约束,导致不能对更长时刻的信号进行剖析。那么关于这些丈量傍边的问题,怎么经过示波器规划来处理呢?本文介绍了R&S公司示波器选用的DDC(数字下变频)技能,很好的处理了以上问题,将多域联合测验发挥的酣畅淋漓。

2 DDC介绍

DDC(Digital Down Converter)即数字下变频,是经过NCO(数控振荡器)发生与射频或中频信号载波相同频率的正弦或余弦信号,与射频或中频信号相乘,终究经过滤波、重采样得到基带信号的进程。

因为数字信号处理的巨大优势,使其得到了广泛的运用。在无线通讯体系中,也越来越期望能将A/D(模数)、D/A(数模)转化接近射频前端,从而能经过数字信号处理来完成通讯中的各种功用。但是现在受ADC(模数转化器)和DSP(数字信号处理器)发展水平的约束,直接在很高频的射频端进行AD改换再进行数字信号处理十分困难——数字示波器也相同,如受处理才干约束,假如在射频端对高频信号进行AD采样,需求很高的采样率,捕获时刻一旦加长,样本点数就会十分巨大,此刻就会发现示波器处理时刻变长,反响很缓慢。为了处理ADC与DSP的这个对立,选用DDC将信号变频到基带,再运用更低的速率进行重采样,就能减小数据量,进步DSP的功率。

图1 DDC原理框图

图1为DDC原理框图,主要由NCO、混频器、低通滤波器和重采样几个模块组成。射频信号经过高速ADC后变为数字信号In(n):

In(n) = s(n)×cos(wn) (1)

其间,s(n)为信号,cos(wn)为载波,w为载波频率。NCO发生与射频信号频率相同的本振信号f(n):

f(n) = cos(wn) (2)

本振信号与射频信号混频相乘后得到信号m(n):

m(n) = In(n)×f(n) = s(n)×cos(wn)×cos(wn)

= 1/2s(n)[cos(2wn)+1] (3)

将信号m(n)进行低通滤波和重采样后便可得到输出信号Out(n):

Out(n) = 1/2s(n) (4)

由此可见,经过DDC,即保存了实在的有用信号s(n),又经过重采样使得数据量大大削减,进步了后续信号处理的功率。相同,假如在数字示波器中运用了DDC技能,不但能保存射频信号中的有用信号,一起能大大削减数据量,进步示波器的处理速度。

下面咱们就来评论R&S示波器中的DDC运用。

3 R&S示波器硬件完成的DDC

在评论R&S示波器中的DDC运用之前,咱们先来比较一下R&S数字示波器与传统数字示波器结构上的不同。

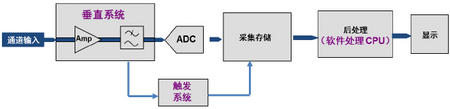

图2 传统数字示波器结构框图

图2为传统数字示波器的根本结构框图。信号经过模仿通道进入示波器,经过笔直增益放大器和滤波,经过ADC转化成数字信号,由收集存储模块存储下来,再经过软件的方法进行后续的处理,终究显现在示波器屏幕上。传统数字示波器选用软件处理的方法进行数据处理,在硬件上并没有DDC的结构。因而对一些高频信号进行收集或许频谱剖析的时分,有必要在高采样率下进行,因为示波器自身存储空间有限,因而收集或剖析的信号时刻长度也相对较短。

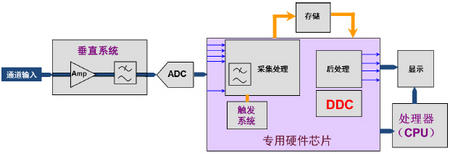

图3 R&S数字示波器结构框图

图3为R&S数字示波器的根本结构框图。信号处理流程与传统数字示波器并无太大不同,但运用了较多的硬件结构,包含触发体系、数字处理、DDC等。其它硬件结构的特色与优势本文不作评论,但能够显着的注意到该结构中运用了硬件完成的DDC。因为运用了硬件的DDC结构,能够对信号先下变频到基带,再以较低的采样率进行重采样,在相同存储空间的情况下,能够收集或剖析更长时刻的信号。而且因为是硬件的完成方法,速度也会较快。

下面,就DDC在I/Q解谐和频谱剖析傍边的运用进行评论。

3.1 I/Q解调中的DDC

咱们先来看一个实在测验中遇到的问题:待测信号为一个载波频率为300MHz,调制带宽为2MHz的调制信号。那么假如用示波器对该信号进行收集,期望收集时刻尽量长,最长能够收集多少秒时刻的信号?关于这个问题,咱们从信号剖析的视点来进行剖析。

首要关于这类调制信号,军用的有雷达信号(如chirp信号),民用的有一般通讯信号(如QAM信号),这些信号绝大多数为矢量信号。关于这类信号的剖析,一定会用到正交解调即I/Q解调。传统数字示波器关于该类信号只能先直接对射频信号进行收集,得到数据存储下来后,再交由专用软件或许用第三方软件编程进行处理(包含I/Q解谐和后续处理)。

图4 传统数字示波器对调制信号处理流程

图4显现了传统示波器关于该类调制信号的处理流程。针对上述问题,载波频率为300MHz,调制带宽为2MHz,那么信号的最高频率为301MHz。依据奈奎斯特采样定理,ADC所用的采样率有必要为信号最高频率的2倍及以上才干实在的复原波形。咱们假定传统示波器ADC运用2倍最高频率即602MSa/s的采样率进行采样(示波器选用刚好2倍联系的采样率一般是不引荐的,一般选用3~5倍的联系才干较为实在的复原波形),假定示波器存储深度为10MSa,那么所能收集信号的最长时刻为10MSa / (602MSa/s) ≈ 16.6ms。即运用传统示波器对该类信号进行收集,只能收集10多毫秒时刻的信号。假如针对载频更高的信号,如2GHz,收集时刻则会更短。

关于上述问题,R&S示波器选用了硬件完成的I/Q解调模块,其间最重要的部分便是DDC。经过运用该模块,能够收集尽或许长时刻的调制信号。