一、高速信号调试面对的应战

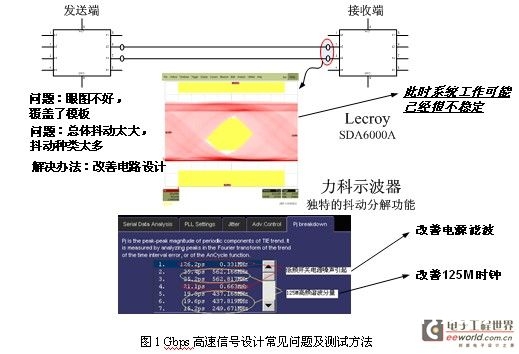

在速率抵达Gbps高速规划中,最常见的问题一般会是眼图欠好、颤动过大等等。如图1所示,接纳端芯片管脚处眼图很差,颤动成分很杂乱。关于这样的问 题,假如咱们运用力科示波器配有的共同的颤动分化功用对颤动进行分化剖析能够清楚的看到首要的颤动来自于330khz频点和125MHZ的谐波(如 250MHZ、560MHZ左右)的频点,依据这些频点,咱们能够更便利更简单的发现此体系的问题首要或许是因为电源部分和125MZH时钟电路规划得不 够完善,这样咱们就能够有针对性的去改进这些电路。

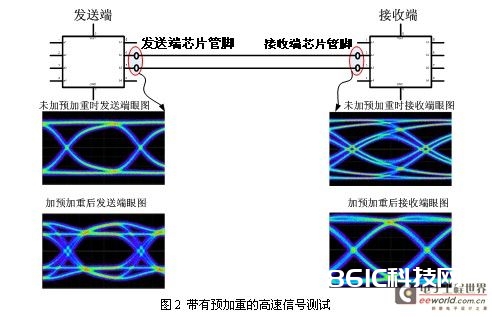

当信号速率进一步进步后,仅改进规划电路或许并不能够彻底改进信号眼图,此刻发送端芯片一般会具有预加剧调理功用,可是需求规划工程师去调理预加剧为最优 值以保证接纳端信号眼图最优化。如图2所示,未加预加剧/去加剧时分,发送端眼图很好,可是接纳端眼图很差;添加预加剧后,接纳端眼图得到有用的改进。由 于芯片厂商一般会供给多种预加剧的程度和起伏的调理,所以工程师们一般需求设法挑选最优的,一般办法都是经过测验接纳端的信号,每调理一次预加剧,测验一 次接纳端信号眼图,需求经过很屡次测验比照才干找到最优值,一般功率会比较低。

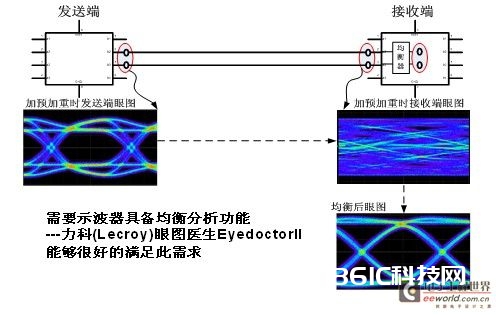

当信号速率更高时,一般抵达5Gbps以上时,仅靠调试电路、调理发送端芯片预加剧都难以改进接纳端信号的眼图,如图3所示,发送端的确现已添加了预加 重,可是接纳端眼图依旧闭合了,关于闭合的眼图就无法对其进行剖析,而奇怪的是即便眼图如此糟糕,可是体系却依旧作业杰出,那么这是为什么呢——因为芯片 接纳端采用了均衡技能,虽然在接纳端管脚处测得的眼图现已趋于闭合,可是均衡后的眼图一般会得到很好的改进。如图3右侧下方均衡后的眼图现已很好了,可是 从图中可看出均衡后的点是在芯片内部,示波器或许不能够直接测验到均衡后的信号,而咱们真实需求剖析的其实是均衡后的眼图。那么咱们应该会问,这样的话示 波器在接纳端现已测不到均衡后的信号,那么示波器还有什么用呢,在接纳端芯片管脚处测验剖析信号还有含义吗?力科眼图医师EyedoctorII软件能够 为您处理这些问题。

图3 带有预加剧和均衡的高速信号测验

二、典型的高速信号规划的首要过程

因为当时工艺水平越来越高,信号速率高于5Gbps的信号规范现已越来越多,如PCIE2.0抵达5Gbps,8Gbps的PCIE3.0规范也或许很快 就会推出;USB3.0抵达5Gbps,SATAIII抵达6Gbps等等。信号速率的进一步进步对电路规划工程师也提出了更多严厉的要求;

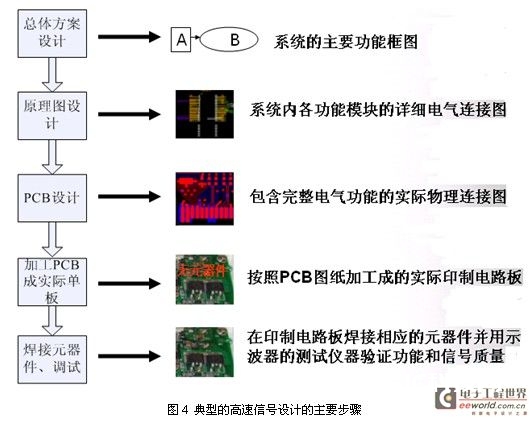

一个典型的硬件体系规划流程大约包含五个过程:即整体方案规划:首要完结体系的功用框图、原理图规划:首要完结体系内各功用模块的具体电气衔接图、 PCB规划:首要完结体系内各功用模块的电气衔接图、加工PCB地图为尚无元器件的实践单板、最终焊接好%&&&&&%进行功用信号等的调试和测验,如图4所示。

在曩昔低速体系中,一般只在硬件体系规划流程的最终一步进行测验验证来保证抵达基本功用要求。而关于高速体系来说,要求会大大不同,第一个不同是需求在设 计的更早阶段就要进行信号质量的剖析,一般在硬件体系规划流程的第三步即现已完结PCB地图规划但没有投板之前就进行严厉的信号完整性剖析;第二个不同是 不仅仅是需求满意功用测验的要求,并且是每个高速信号在满意要求之外还需求较大的余量,以保证高速信号甚至整个体系的高可靠性。关于5Gbps以上的信 号,还有个不同是有些规范中现已明确提出需求对接纳端的进行容限测验,如USB3.0,而以往接纳端测验仅仅选项测验。

三、典型的高速背板体系及其首要规划调试流程

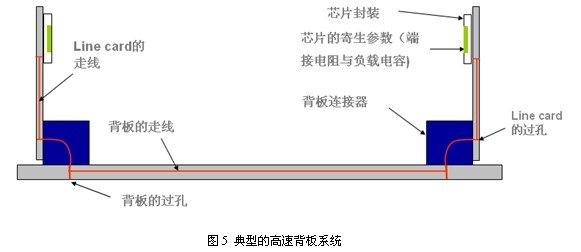

下面咱们以一个高速背板体系为例来阐明下高速体系的规划流程。如图5所示为一个典型的由两个线卡加上一块高速背板构成的高速信号传输体系。咱们看到,图最 下方的为带有高速接插件的背板,经过接插件在左右各有两个线卡(line card)插在背板上,左面的线卡上有高速信号发送芯片,右边的线卡上有高速信号接纳芯片,如图中赤色线所示,高速信号从左面子卡上的发送端芯片宣布,经 过线卡上的传输线、接插件、背板上的走线、接插件、线卡上的传输线抵达芯片接纳端。子卡上的高速信号走线一般比较短,对信号的影响很小;背板上的走线都比 较长,对信号影响最大,背板面积一般都比较大,生产本钱也比较高,所以关于这样一个体系来说,背板规划的胜败将至关重要;这样一个体系规划的首要应战在于 怎么有用的处理背板传输线对信号质量的影响(如阻抗不接连带来的反射问题、走线过长带来的信号起伏过度衰减问题、高速信号的ISI问题、板间衔接处的阻抗 接连性问题)。当然挑选好芯片、接插件、PCB板材等也是很重要的要素。此类问题都能够经过仿真办法与测验办法相结合来更好的处理。

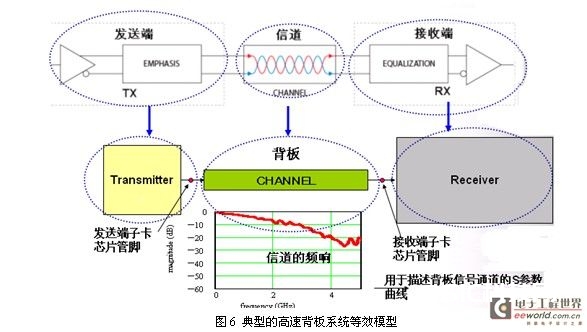

将上页的高速背板体系作一个等效的模型,如图6所示,因为线卡上走线较短,所以咱们把发送端和接纳端线卡简化,以发送端Transmitter和接纳端 Receiver表明,一般发送端带有预加剧,接纳端带有均衡;背板上的长传输线首要用于传输信号,一般称为信道,即传输信号的通道,在SI类的文献中也 称为互连,能够用S参数模型来等效其信道的呼应。S参数模型能够经过VNA测验或许电磁场、CAD等仿真软件仿真得到。

关于当今的高速体系规划来说,需求在更多的规划环节进行信号质量操控,关于上述的典型高速背板体系来说,一般有如下三个环节:(1)子卡、背板的PCB版 图现已完结(子卡指发送端子卡和接纳端子卡);(2)子卡现已加工完结,背板的PCB地图现已完结可是没有加工;(3)子卡和背板的PCB地图现已完结;

关于第一个环节,即子卡、背板的PCB地图现已完结,则首要是经过软件仿真的办法。如运用HSPICE软件将发送端和接纳端芯片的HSPICE模型和背板 的S参数模型整合到一同进行通道仿真。此一环节进行剖析的长处是现在只要电路规划图纸,还未做成什物,假如此阶段发现问题,则能够便利的修正调整规划,不 会形成很多本钱丢失;并且必将大大缩短产品研制周期,节省时间;缺陷是需求芯片厂家供给准确的HSP%&&&&&%E模型(有时分得到这样的准确模型比较困难);仿 真软件所运用的信号源为抱负信号源,未考虑子卡上的实践情况如串扰、反射等等,并且现在的高速仿真软件仿真速度比较慢,会大大影响调试功率。