1.必要性剖析

现代通讯中数据通讯越来越重要,评价误码率是评判传输体系功用的终究规范。误码率的测验都是作为一个体系目标首要会集在基带信源码的测验。跟着体系集成度的杂乱性添加,体系功用区分细化导致了在分机体系中也需求进行误码率的测验。接纳机,发射机的误码测验现已越来越多的出现在咱们面前。而误码率测验体系所面临的信号现已由传统的信源信号转变为模仿的中频信号,乃至是射频信号。

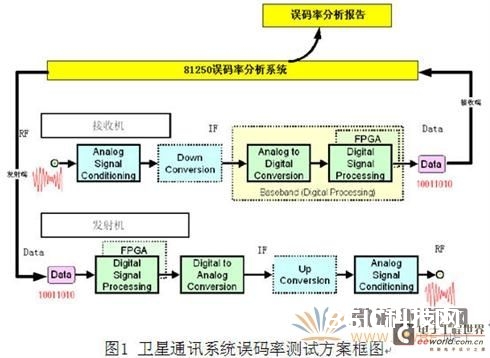

2.渠道的组成框图

体系组成:81250误码率剖析体系。

如图1,测验体系由安捷伦ParBERT 81250A 并行误码测验体系构成。ParBERT 81250A 并行误码测验体系选用VXI模块化构架,为了满意用户不同的测验需求,以及增强体系装备扩展晋级的灵活性,体系硬件区分为前端、数据模块、时钟模块、主机箱,体系操控计算机组成(如下图所示)。前端决议了数据端口的特性(码型发生器/误码剖析器)才能,而数据模块作为小的机架,承载前端并终究完结其(码型发生器/误码剖析器)功用。这样,数据模块就能够对数据码形(包括用户自定义数据文件,规范PRBS/PRWS)进行生成、排序和剖析。一切数据模块需求至少一个时钟模块驱动,才能够发生/剖析相应速率的数据,其作用是发生仪器的共用体系时钟或频率。

3.渠道的功用特色

可测验杂乱的具有多通道,多种频率的设备,例如完结数字视频多路复用器/解复用器(并串转换器/串并转换器)电路测验,可使用一个通道向被测设备供给/接纳操控信号,并可对来自被测设备的操控信号作出响应可测验多种逻辑电平,如预设CML、LVDS、ECL、PECL、SSTL-2等电平。并且用户能够自定义逻辑电平。

可生成包括根据存储器的数据和、或PRBS并支撑生成具有报头和净荷的数据包。使用嵌套循环,原则上能够生成任何长度数据包。破例能够经过捕获数据直接生成测验数据包。

在测验过程中,能够主动将预期数据与输入数据进行对准,无须以手艺方法找到正确的采样点,故可节省时间,一般仅需100ms假如终端上的误码率超过了再同步误码率的门限,则丈量主动完结再同步在改动剖析仪时延设置时丈量接连进行颤动模仿,用于颤动容限测验

4.仪器的功用参数

81250误码率测验渠道首要目标

|

项目 |

675 Mb/s渠道 |

|

数据率 |

333.3 Kb/s~675 Mb/s |

|

通道数 |

4(2发2收) |

|

输入/输出 |

Differential和single ended |

|

输出数据 |

PRBS/PRWS/ 2 MB memory |

|

码型格局 |

DNRZ, RZ, R1 |

|

输出起伏/分辨率 |

0.1V~3.5V/10mV |

|

可变上升/下降时间规模 |

0.5~4.5ns |

|

颤动 |

数据形式:<100ps(峰值)(80ps典型值) 时钟形式:8ps(RMS,典型值) |

|

输出通道加 |

XOR或模仿 |

|

输入灵敏度 |

差分:50mv 单端:100mv |

|

输入电压规模 |

0~+5v和-2~+3v |

|

抱负输入信号的相位容限 |

>1UI~100ps |

|

数字电平 |

TTL, (P)ECL, LVDS |

5.渠道的装备

81250A: 并行误码剖析仪体系

81250 #013 IEEE 1394 PC link to VXI

81250 #149 E8403A (VXI 13 slot mainFrame)

E4857A Control software.

E4805B*1 2.7GHz Central Clock Module

E4832A*1 675Mb/s Gen./An. Module

E4838A*2 675Mb/s Generator Front End

E4835A*1 675Mb/s Analyzer Front End