作者/ Rejeesh Kutty ADI公司

摘要:本文具体地描绘了RF基带处理器的一般规划准则,并运用ADI公司的AD9361 FPGA参阅规划评论了BBP的实践硬件施行。本文中提出的相关基带处理器答应对数据进行处理,以使其在两个RF体系之间进行无线传输。

现在,无线体系无处不在,无线设备和服务的数量持续增长。规划完好的RF体系是一项跨学科规划应战,模仿RF前端是其中最要害的部分。但是,AD9361等集成RF收发器的推出明显减少了此类规划的RF应战。这些收发器可为模仿RF信号链供给数字接口,能够轻松集成到ASIC或FPGA上进行基带处理。基带处理器(BBP)答应在终端运用和收发器设备之间的数字域中处理用户数据。此外,运用Simulink等体系建模东西能够轻松完结基带处理器规划。但是,新手用户或许会发现难以了解和处理这个通讯体系难题。本文测验为无线传输通讯体系规划和施行简略的RF基带处理器。规划运用AD9361 FPGA参阅规划结构,在AD-FMCOMMS2-EBZ和Xilinx® ZC706平台上施行。

1 在两个正交信号I&Q上重复数据

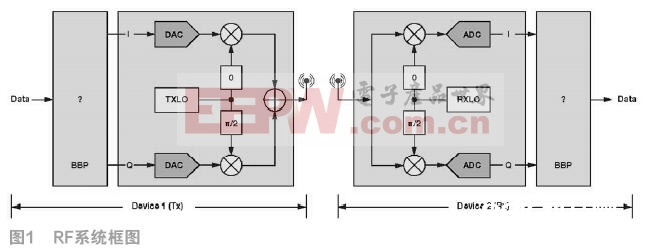

典型的RF体系如图1所示(直接RF体系在外)。图1仅显现了单个数据途径,反方向是该数据途径的镜像图画。因为载波互相独立且互相不同步,因而,发射和接纳载波之间存在相位和频率偏移,这将对接纳器的解调产生晦气影响。一个重要问题是信号回转,因为偏移会定时合并和漂离,正交信号或许会回转其效果。战胜这种不确定性的简略办法是在两个正交信号上重复相同数据。

2 以串行方式发送和接纳数据(按位)

大都情况下,与BBP衔接的RF前端接口是DAC和ADC,这些是模仿信号的数字接口。因而,不能简略地将数据发送到DAC输入,并估计在ADC输出端取得相同数据。数据以串行方式发射,将单个位数据映射到DAC的悉数分辨率。相同,数据以串行方式接纳,从ADC的悉数分辨率解映射,这供给了满足的冗余。假如这些是16位转换器,则接纳器将从或许的65536数据会集决议1或0。仅这一点,便能够明显简化解码。

3 用于RF收发器的简略基带处理器

3.1 I&Q信号互相正交

RF前端设备(如AD9361)是I/Q收发器。假如输入是正交信号,这些设备最有用。这些设备一般沿两个数据途径进行内部I/Q匹配和校对,以抵消二者之间的任何差异。规则是,实部(I)信号是余弦函数,虚部(Q)信号是正弦函数。

3.2 调制计划是BPSK

能够布置信号起伏、频率或相位调制的一切常见办法。检测相位差异相对来说愈加简略。因为数据以串行方式传输,因而,必然会挑选二进制相移键控(BPSK)。

3.3 位距离是8个样本

数据需求时序信息、位距离,或许的最大位距离是采样周期。为了使接纳器坚持简略,需求满足的时刻来解码信号,并做出决议。最简略的时序康复办法是零交越和峰值检测。在这种情况下,峰值将不共同。因而,挑选零交越进行位距离检测和盯梢。两种体系之间也存在载波差异。在某些情况下,在用户数据的恣意端,样本或许模糊不清。为每半个正弦信号留出4个样本,位距离设置为8个样本。因而,有用的传输速率是采样频率除以8。

3.4 数据没有直流成分

时序和相对相位康复以信号的零交越为根底,因而,单个信号需求不含任何直流成分。此外,要求信号每隔一个位距离答应至少一个零交越。正弦信号兼具两者的特点,而且十分契合上述BPSK调制计划要求。

3.5 数据已加扰

用户数据是恣意的,很或许是一长串1或0。数据需求加扰,以便在接纳器端康复时序和相位,然后更高效地盯梢信号。

3.6 数据以数据包的方式传输

因为体系互相不同步,因而接纳器的信号会存在起伏、频率和相位差错。解调信号是发射信号相对于本地载波产生相位改变的信号。载波或许会盯梢一段时刻,选取数据,然后再盯梢。因而,规划需求做好部分数据丢掉的预备。为此,数据以数据包的方式传输。可重复传输多个数据包,而非整个数据。

3.7 运用CRC验证数据包

数据包带着循环冗余校验(CRC)码,因而,假如存在不匹配,则答应接纳器丢包,并恳求再次发送。

3.8 在每个前同步码期间完结时序和相位校对

数据包表头带着前同步码,用于将其从接纳到的数据流中区分出来。此外,接纳器运用该前同步码复位信号的时序和相位信息,以解调数据包数据。

3.9 内置性能指标

接纳器也支撑计算计数器,如接纳到的、丢掉的或校对的数据包数量。这些计数器用于衡量和监控性能指标,包含误码率和有用数据速率。

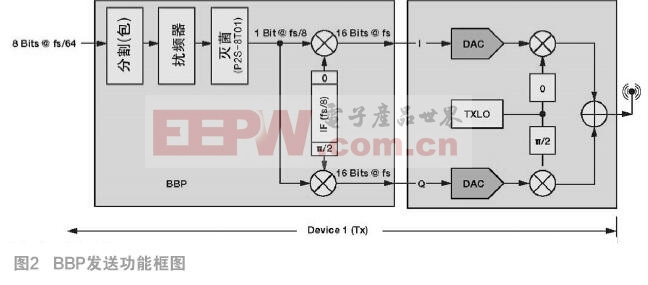

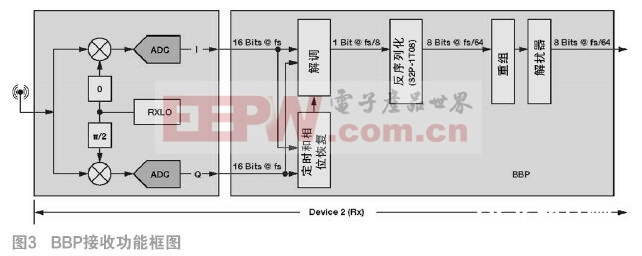

总而言之,数据作为数据包以串行方式发送和接纳。数据包带着前同步码和CRC。数据在收发器设备前的中心正交信号上经过BPSK调制和解调。因而,中心信号频率和数据的位速率是采样速率的八分之一。基带处理器模块及上述规划细节如图2和图3所示。

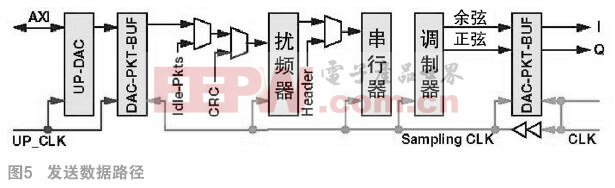

发送器读取数据字节(字符宽度),并将其转换为带有表头或前同步码的数据包。将CRC添加到数据包结尾。然后,对数据包数据进行加扰和串行处理。在衔接到收发器之前,单个位数据相位调制余弦(I)和正弦(Q)函数。

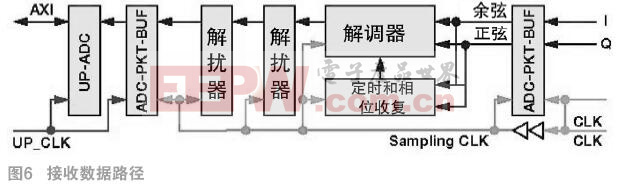

在接纳方向,离线模块康复并盯梢时序距离和调制信号的相对相位。该信息用于从输入的ADC样本中康复串行数据。然后组装到数据包,并进行解扰。在数据包结束时,比较CRC,假如不匹配,则丢掉数据包。假如CRC匹配,数据传递给终端用户。

4 完成

BBP规划在硬件中施行和测验。硬件是两个评价板的组合:具有Zynq FPGA设备的Xilinx ZC706评价板和AD9361收发器的AD-FMCOMMS3-EBZ评价板。ADI供给支撑该硬件的完好参阅规划。该开源规划在首要东西版别中免费供给,可取得彻底支撑和更新。

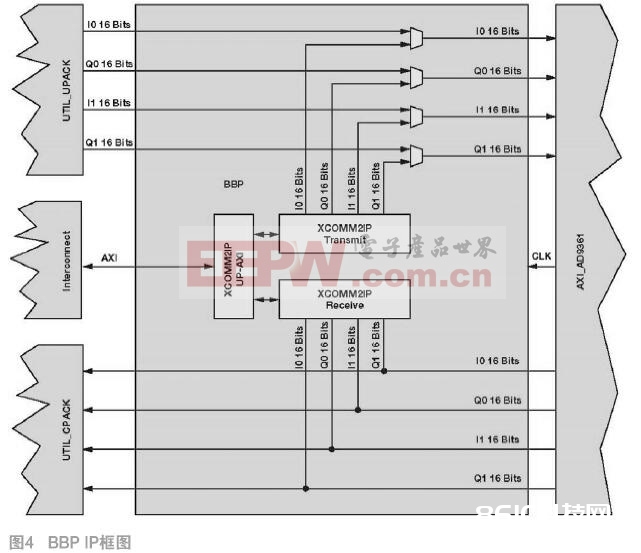

9361设备衔接到axi_AD9361 IP外设。它在RF设备和体系存储器之间传输原始采样数据。外设和设备经过Linux内核驱动程序进行初始化和操控。BBP则作为衔接到axi_AD9361的另一个IP外设。出于前史原因,BBP IP命名为axi_xcomm2ip。Linux中的用户空间运用程序用于在体系之间操控、发送和接纳数据。

在ADI参阅规划中,在发送方向,axi_AD9361 IP衔接到解包模块(util_upack),在接纳方向,衔接到打包模块(util_cpack)。在发送方向,BBP数据刺进解包模块和AD9361内核之间。为了使其不影响默许数据途径,BBP支撑可选的数据途径多路复用器,以挑选解包数据源或BBP数据源。BBP答应参阅规划数据途径作为默许途径,并仅在启用时挑选BBP数据源。在接纳方向,BBP仅衔接到AD9361内核。参阅规划数据途径不受影响。这答应结构不受阻碍地引导和设置体系。在体系设置后,启用BBP,可经过掩盖默许数据途径来进行数据传输。以ADI参阅规划施行的BBP的框图如图4所示。

5 小结

本文中评论的规划、初始化和数据传输运用一对这种硬件。设置仅需一对HDMI®监视器、键盘、鼠标及天线。体系互相彻底不同步,但需求相同设置。在每个方向,数据在不同载波上传输。设备1的发射载波频率和设备2的接纳载波频率相同,但在另一个方向上不同。但是,假如回送中运用单个设备,发射和接纳载波有必要具有相同的频率。BBP的HDL规划选用ADI库模块。

本文来源于《电子产品世界》2017年第1期第76页,欢迎您写论文时引证,并注明出处。