伴随着现代大规模集成电路制作工艺的快速开展,规划工程师必需直面芯片制作过程中或许发生的物理缺点。如今盛行的可测验性规划(DFT:Design For Testability)应运而生,并为确保芯片的良品率担任着越来越重要的人物。规划中,存在对测验覆盖率有较大危害的两种状况:一种存在于数字逻辑-模仿逻辑(包含存储器)输入-输出处之暗影部分,另一种存在于特定的多芯片封装状况下未绑出的输入-输出焊垫处。二者的共同点在于:测验办法下部分逻辑的不行控或不行观测。

规划布景

本文讨论的规划方针是一个来自意法半导体的数字音频信号处理芯片,要求对数字功用逻辑进行扫描链测验,覆盖率到达98%以上。其功用逻辑中存在一些模仿模块,如锁相环、模数转换器和一些存储器单元等。更为重要的是,该芯片需求根据不同的使用体系需求,不光需求独自封装办法,也需求多芯片同享同一封装。这样,在某些多芯片封装中,就有部分焊垫未引出或接地。而测验的规划初衷是发生一组测验向量适用于一切封装形,就要求考虑最严厉的封装下可用的管脚资源。

DFT规划有两个基本原则:可操控性和可观测性,即DFT规划要求一切输入逻辑是可控的和输出逻辑是可测的。明显,考虑到本规划中的模仿模块接口和封装办法的资源有限性,不行控逻辑和不行观测逻辑对不小于98%的方针测验覆盖率给出了很大的应战。

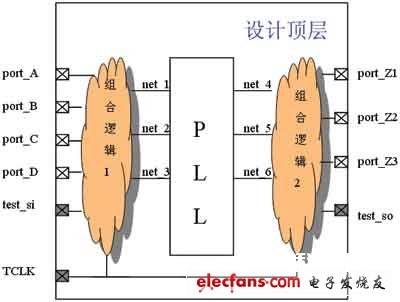

如图1所示,在某种芯片封装状况下,除信号test_si和test_so外,其他焊垫并未绑出(接地或悬空),然后形成信号port_A、port_B、port_C和port_D的不行控,以及信号port_Z1、port_Z2和port_Z3的不行观测(悬空)。导致许多相关逻辑不能正常参于DFT测验,测验覆盖率遭到较大的危害。

图1 封装形成的测验逻辑不行控和不行测

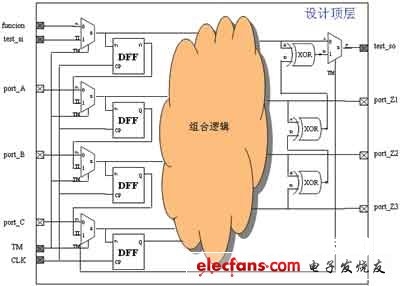

DFT规划的可操控性和可观测性是经过原始的管脚来完结的,事实上功用规划不或许专门为DFT保存足够多的管脚。如图2所示的数字-模仿接口,因为PLL模块的存在,明显信号net_1、net_2和net_3上得到的测验成果不行直接观测(不行测),组合逻辑1相应的测验覆盖率下降了;一起,因为PLL模块的存在,信号net_4、net_5和的net_6不能直接赋值(不行控),导致组合逻辑2的部分逻辑不能正常参于DFT测验,相应的测验覆盖率遭到较大的危害。总的来说,芯片的测验覆盖率下降了。

解决方案

针对规划中的上述状况,可以经过恰当增加测验点的办法,使本来不行控和不行测的逻辑改变反映到扫描链上,使之变得直接可控和可测,以期进步整个芯片的测验覆盖率和测验功率。

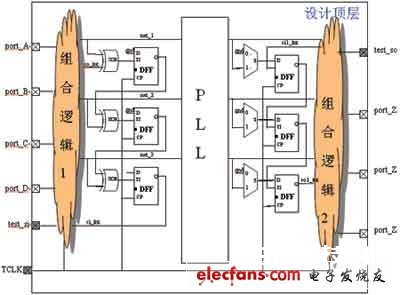

关于图1所示的某些封装中,不行控和不行测的未绑出(接地或悬空)管脚,图3给出了相应的定制的解决方案。

图3 增加操控点和观测点进步测验覆盖率(封装部分管脚未绑出状况)

在输出管脚处,增加少数异或门和挑选器材。当操控挑选信号为“0”时,电路处于正常作业状况,输出管脚正常输出功用信号。当挑选操控为“1”时,电路处于测验状况,用异或门将未能绑出的管脚的改变引出,相当于这些管脚也可以被观测了。

针对图2所示的数字-模仿接口,部分模仿模块输入信号经过组合逻辑给出,但在测验时并没有逻辑将这些“结尾”的信号影响引出调查,因而这些点是不行观测的。这与DFT规划可观测要求(需管脚直接输出)不相符,或许形成测验覆盖率的危害。一起,部分模仿模块输出信号操控相应的组合逻辑,但在测验中,这些点是“浮空”(不行操控)的。这与DFT规划可控要求(需管脚直接输入)不相符,形成测验覆盖率的下降。图4给出了相似前者的定制解决方案,其实质也是把这些不行控和不行测点连到测验链上去,让这些逻辑直接可观测或可操控以改进测验成果。

图4增加操控点和观测点进步测验覆盖率(数字-模仿接口状况)

如图所示,在模仿模块输入信号处增加少数异或门和挑选器材,并将它们连到扫描链上去。当操控挑选信号为“0”时,电路处于正常作业状况,模仿模块的输入管脚正常接纳功用信号。当挑选操控为“1”时,电路处于测验状况,用异或门或许其他器材将未能观测管脚的改变引出,相当于这些管脚直接可以被观测了。

如图所示,在模仿模块输出信号处增加一个带有挑选端的寄存器。当操控挑选信号为“0”时,电路处于正常作业状况,模仿模块信号正常输出到后续的功用逻辑。当挑选操控为“1”时,电路处于测验状况:在移位过程中,这些点由测验链预置相应的值;在捕获过程中,将之接地避免不定态在规划中的传达。

关于其他的模仿模块如ADC, 存储器等,选用相似的办法可改进整个芯片的测验覆盖率和测验功率,到达方针测验作用。

结语

在前面提及的实践项目DFT规划中,功用逻辑部分含有万余寄存器。为进步测验覆盖率,增加仅12个寄存器及很少部分组合逻辑作为测验点后,即可将测验覆盖率从本来的95%进步到 98.3%。由此看来,这种办法是很有功率的。而且可根据项目实践需求,增加更多点以期到达更高覆盖率,理论上测验覆盖率可接近100%。

引荐RTL功用规划时就能考虑这种测验结构。这样做规划工程师之间可以了解互相的规划需求,功用测验结构清楚,在DFT规划过程中省去许多费事。假如发现这类问题在RTL完结之后,一些DFT东西也供给用户自定义的测验点刺进,可是要注意测验操控信号选取必定要与需求的测验办法匹配,不然无法完结相应的测验希望。这种办法的关键是了解在哪里加测验点更为有用。