0 导言

微波接纳机是一种重要的无线通讯设备,跟着车载、机载、舰载等移动环境下的运用需求的发生,微波接纳机的小型化、模块化、通用化是当时有必要处理的问题。

Compact PCI 简称CPCI,是现在科研和军工范畴广泛运用的一种工业计算机总线规范。CPCI 结合了PCI 总线的电气、软件规范和欧式卡的工业拼装技能规范,与PCI 规范彻底兼容;界说了32 位数据总线 ( 可扩展到64 位),最高作业频率为 33MHz ;可以完结设备的即插即用;体系规划结构紧凑、可靠性高,习惯各种运送、运用环境。

结合CPCI 总线技能的微波接纳机功能优秀,可以满意智能交通、航空航天等很多范畴的运用要求。

1 体系原理

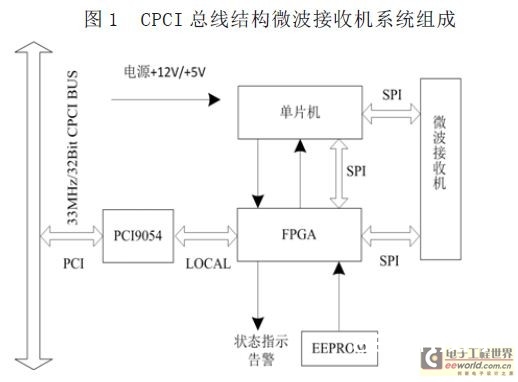

本接纳机体系以FPGA 和单片机为中心操控单元,完结CPCI 总线结构下微波信号的接纳、滤波、变频、增益操控等功能。体系主要由微波接纳机、PCI9054、FPGA(EP1C6Q240C8)和单片机(Atmega8L)组成,体系组成如图1 所示。

CPCI 总线信号经高传输速率的PCI 桥芯片PCI9054 转化为LOCAL Bus 信号,经过Verilog HDL 言语编程发生对FPGA 的操控信号,完结数据的快速读写,一起在外部选用EEPROM 进行高速数据的缓冲,然后完结与FPGA 与CPCI 总线的高速数据通讯。在操控信号效果下,FPGA 实时接纳LOCALBus 信号,并进行运算处理,对接纳机增益进行操控;对体系锁相环的操控指令、数据则经过串口发送给单片机,FPGA 和单片机共同完结对接纳机体系的操控。体系供电由CPCI 机箱内5V、12V 开关电源供给。

2 要害技能规划

依据CPCI 总线规范及结构特色要求,CPCI 总线结构微波接纳机体系的规划需求处理总线接口转化、结构规划、电源规划以及电磁兼容规划等要害技能。

2.1 总线接口转化

2.1.1 CPCI Bus 到LOCAL Bus 的接口规划

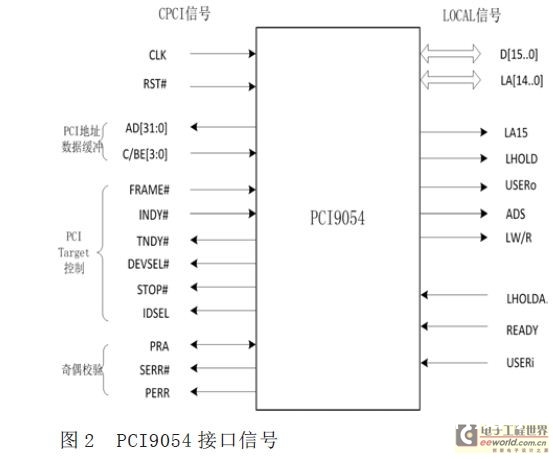

CPCI 总线信号到LOCAL 总线信号的转化是根据PCI9054芯片完结的。PCI9054 是PLX 公司出产的一款根据PCI2.2总线规范的通用接口芯片,是32 位、33MHZ的PCI总线主I/O 加速器,突发传输速度可达132MB/s.有M、J、C 三种作业形式,本规划中选用数据线与地址线独立运用的C 形式。

PCI9054 支撑主控、方针、DMA( 直接存储器拜访)3 种部分总线传输办法,这儿选用了方针传输办法和高传输速率的DMA传输办法,即PCI9054 既是PCI 总线的方针,一起又是LOCAL总线的主控者。

PCI9054 供给了3 种物理总线接口:CPCI 总线接口、LOCAL 总线接口和串行EEPROM 接口,其间需求用户规划的是LOCAL 总线接口。其接口信号见图2.

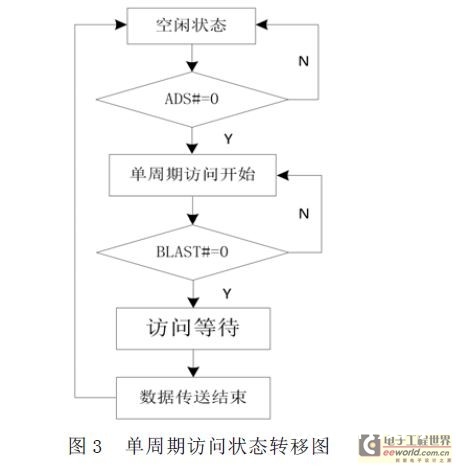

PCI9054 对本地设备的拜访有单周期拜访和突发办法拜访2 种拜访办法,单周期拜访可选用状况机完结对LOCALBus 接口的操控,其状况搬运如图3 所示。

2.1.2 SPI 总线接口规划

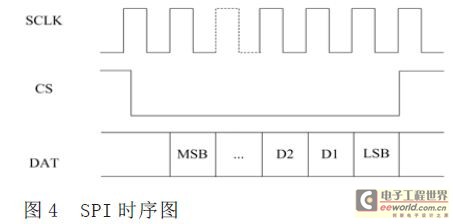

FPGA 与单片机的通讯需求经过SPI 总线来完结。SPI总线是一种同步串行总线,以3 线或4 线办法通讯。本规划中所运用的3 条通讯线为:时钟SCLK,数据DAT,片选信号CS.图4 为SPI 作业时序。

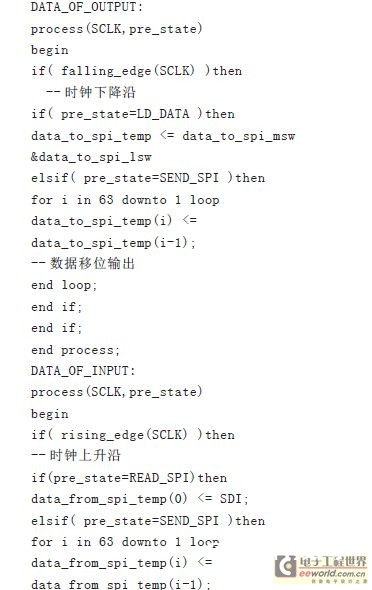

当FPGA 从单片机读取数据时,向单片机发送读使能信号RD(可用恣意I/O 口),串行数据经DAT 口在每个时钟(SCK)的上升沿送入FPGA 的移位寄存器,悉数承受结束后,CS 置1 ;当FPGA 向单片机传输指令或许数据时,CS 拉低后,移位寄存器开端作业。内部并行数据经串/ 并转化为64 位串行信号,每个时钟的下降沿移位寄存器送出一位数据,单片机经过DAT 端口读取数据。凭借VHDL 硬件描绘言语可便利地完结该体系,部分程序如下:

2.2 结构规划

微波接纳机的悉数硬件电路规划在一张CPCI 载板上,经过高密度2mm 插针式连接器安装在一个6U 规范机箱内。机箱选用220V 沟通供电,前面板设有状况指示灯,可指示体系供电、PCI 总线拜访状况及微波接纳机内部射频模块确定状况。

CPCI 总线结构的规划使该模块具有“即插即用”的高度兼容性,便利接纳机体系的树立、操作,且具有杰出的抗震性,合适移动渠道的运用。

2.3 电源规划

因为CPCI 机箱供给的开关电源电磁搅扰严峻,且纹波系数较大,严峻影响接纳机杂散、相噪等功能,因而有必要对电源进行处理。机箱内12V 开关电源经LM7809、LM7805、LT1965三级DC/DC 稳压后,别离供给给体系中数字电路、模仿电路运用,有用降低了电源纹波和数字电路、模仿电路之间的电磁搅扰。

2.4 电磁兼容规划

CPCI 结构微波接纳机的电磁搅扰来历有机箱内部的电源搅扰及接纳机的本振频率走漏等。为了消除电源搅扰的影响,将CPCI 机箱内计算机电源和接纳机电源分隔运用,并进行多级稳压处理;模块内灵敏电路选用独自的屏蔽盒进行阻隔,削减频率走漏;在PCB 板规划中将射频线和操控线分层阻隔;为了减小载板上其他模块的信号对底板总线的影响,用10Ω的电阻在CPCI 卡的接插件J1 口处进行串联电阻匹配。

3 试验验证

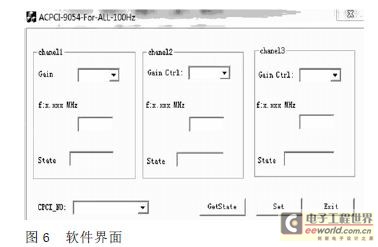

图5 为依照本文规划办法完结的 CPCI 总线结构微波接纳机什物。CPCI 载板上设有三个模块,别离完结两路中频信号到S 频段的上变频和一路S 频段信号到中频的下变频。中频输入、S 频段输出和参阅信号输进口均为SMA-50K.操控软件可以完结对上、下变频器的增益操控和输出、输入频率设置,以及每个变频模块确定状况的读取。其软件操控界面如图6 所示。

经过实践测验,本接纳机软、硬件规划满意CPCI 总线结构微波接纳机的操控及目标要求,经过验证。

4 结束语

以CPCI 总线的工控机为渠道,结合6U 的CPCI 卡研发的微波接纳机体系,将微波接纳机技能与先进的计算机技能融为一体,处理了业界长时间面对的多通道、小型化、模块化、PCI协议操控等射频接纳前端技能难题,具有宽广的运用远景。