假如您有触摸运用 FPGA 的高速数据收集规划,没准听说过新术语“JESD204B”。

我在工作中看到过许多工程师问询有关 JESD204B 接口的信息以及它怎么同 FPGA 协作。他们特别感兴趣的是 JESD204B 接口将怎么简化规划流程。

与LVDS 及CMOS 接口比较,JESD204B 数据转化器串行接口规范可提供一些明显的优势,包含更简略的布局以及更少的引脚数。因而它能取得工程师的喜爱和重视也就家常便饭了,它具有如下体系级优势:

● 更小的封装尺度与更低的封装本钱:JESD204B 不只选用 8b10b 编码技能串行打包数据,并且还有助于支撑高达 12.5Gbps 的数据速率。这可明显削减数据转化器和 FPGA 上所需的引脚数,然后可协助缩小封装尺度,下降封装本钱;

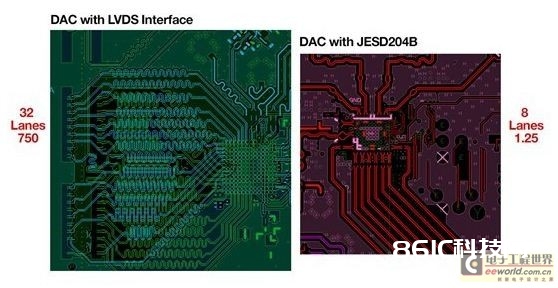

● 简化的 PCB 布局与布线:更少的引脚数可明显简化 PCB 布局与布线,由于电路板上的途径更少。由于对畸变办理的需求下降,因而布局和布线可进一步简化。这是由于数据时钟嵌入在数据流中,并在接收器中与弹性缓冲器结合,无需经过“波形曲线”来匹配长度。图 1 是 JESD204B 接口对简化 PCB 布局有多大协助的实例;

● 高活络布局:JESD204B 对畸变要求低,可完成更远的传输间隔。这有助于将逻辑器材布置在间隔数据转化器更远的方位,以防止对活络模仿器材产生影响;

● 满意未来需求:该接口可以自适应不同数据转化器分辨率。关于未来模数转化器 (ADC) 及数模转化器 (DAC) 而言,无需对 TX/RX 电路板进行物理上的从头规划。

图 1:LVDS DAC 的 PCB 布局(左);选用 JESD204B 的相同 DAC 的 PCB 布局(右)

这是不是意味着您要改用 JESD204B 接口?

不一定。与 LVDS 接口比较,JESD204B 的缺陷是具有更长的绝对时延,这关于有些运用来说是不行承受的。

虽然 JESD204B 可提供许多优势,但有些运用要求极短的时延,最好是无时延。一个很好的实例是电子战中运用的信号屏蔽器。该设备不只要求绝对时延,并且需求最大极限地下降任何或许的推迟。

关于这种运用,您应该考虑 LVDS 接口,因而它没有在 JESD204B 进步行数据串行化的推迟。