在进行嵌入式体系开发时,微处理器要与不同的设备完成互连,这就需求树立一致的通讯总线规范。通讯总线可分为并行总线和串行总线,并行通讯速度快、实时性好,但占用的口线多,不适宜小型化产品的开发;串行通讯速率虽低,但在数据通讯吞吐量不是很大的微处理电路中显得愈加简易、便利、灵敏。串行通讯总线的品种繁复,文中就当时嵌入式体系开发中最常用的RS485总线的通讯牢靠性做剖析,期望对设计者有所协助。

1 RS485规范

RS485是串行数据接口规范,由电子工业协会(EIA)拟定并发布的,它是在RS-422基础上拟定的规范,RS一485规范选用平衡式发送,差分式接纳的数据收发器来驱动总线,详细规范要求:接纳器的输入电阻Rin≥12 kΩ;驱动器能输出±7 V的共模电压;输入端的电容≤50 pF;在节点数为32个,装备了120 Ω的终端电阻的状况下,驱动器至少还能输出电压1.5 V(终端电阻的巨细与所用双绞线的参数有关);接纳器的输入灵敏度为200 mV(即(V+)一(V一)≥0.2 V,表明信号“0”;(V+)一(V一)≤一0.2 V,表明信号“l”)因为RS一485的远间隔、多节点(32个)以及传输线成本低的特性,使得EIA RS-485成为工业使用中数据传输的首选规范。

2 RS485数据传输的牢靠性

RS485总线归于外部总线,外部总线用于与外部设备进行信息和数据交换,是设备级的。

RS一485规范所具有的噪声按捺才干、数据传输速率、电缆长度及牢靠性是其他规范无法比拟的。然而在实践使用中,往往涣散操控单元数量较多、散布较远、现场存在各种搅扰,使得通讯的牢靠性不高。为了进步RS一485总线在实践使用中的牢靠性,应留意以下几个问题。

2.1 阻抗匹配

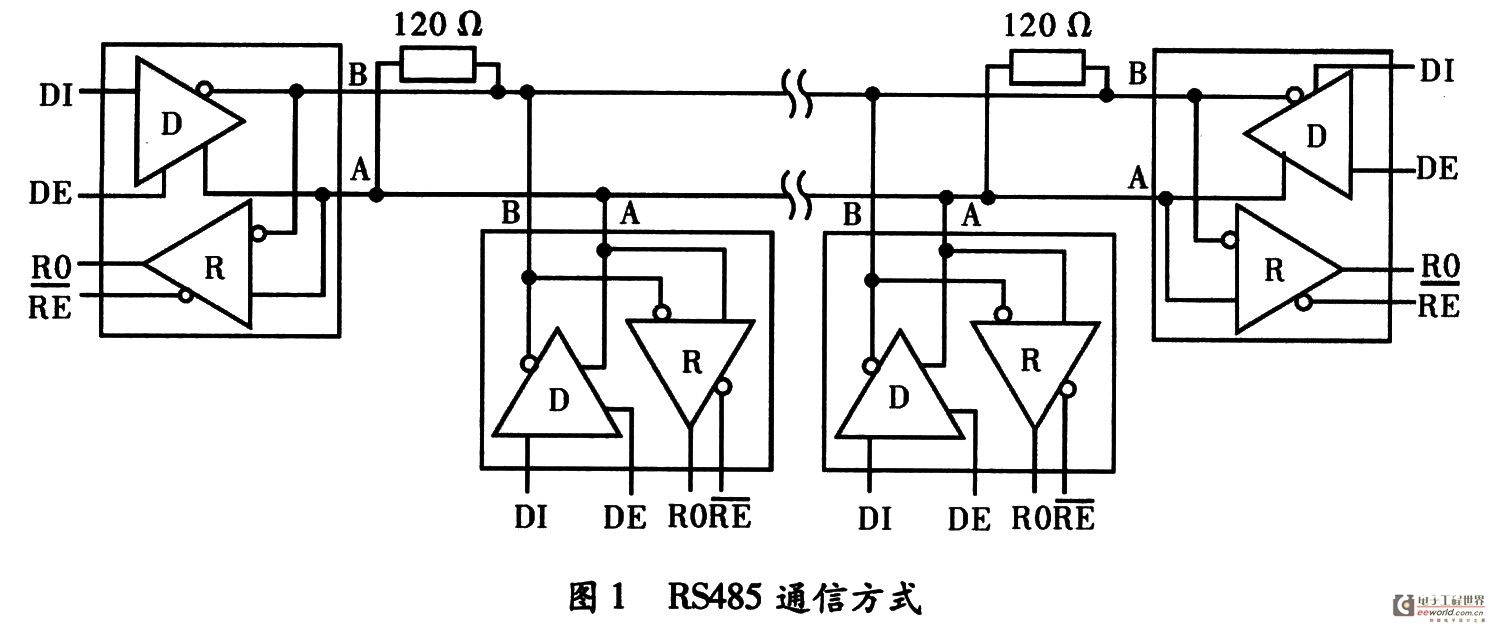

RS一485的信号线应考虑阻抗匹配问题,所谓阻抗匹配即信号线的负载应与信号线的特性阻抗持平。特性阻抗与信号线的宽度、与地线层的间隔以及板材的介电常数等物理要素有关,是信号线的固有特性。阻抗不匹配将引起传输信号的反射,使数字波形发生振动,形成逻辑紊乱。因为通讯载体是双绞线,它的特性阻抗为120 Ω左右,所以线路设计时,在RS一485网络传输线的始端和结尾各应接1只120 Ω的匹配电阻,如图1所示,以削减线路上传输信号的反射。

2.2 失效维护

RS一485规范规则接纳器门限为±200 mV。这样规则能够供给比较高的噪声按捺才干,但一起也带来了一个问题:当总线电压在±200 mV中心时接纳器输出状况不确认。因为UART以一个前导“0”触发一次接纳动作,所以接纳器的不确认状况或许会使UART过错地接纳一些数据,导致体系误动作。当总线闲暇、开路或短路时都有或许呈现两线电压差低于200 mV的状况,有必要采纳必定办法防止接纳器处于不确认状况。传统的做法是给总线加偏置,当总线闲暇或开路时,使用偏置电阻将总线偏置在一个确认的状况(差分电压≥200 mV),但这种办法依然不能处理总线短路时的问题。Maxim公司的MAX3080系列S485接口芯片将接纳门限移到一200 mV/一50 mV,奇妙地处理了这个问题。不光省去了外部偏置电阻,并且处理了总线短路状况下的失效维护问题。

2.3 地线与接地

电子体系的接地是一个十分要害而又常常被忽视的问题,接地处理不妥经常会导致不能安稳作业乃至危及体系安全。关于RS一485网络来讲也是相同,没有一个合理的接地体系或许会使体系的牢靠性大打折扣。一个典型的过错观点便是以为RS一485通讯链路不需求信号地,而仅仅简略地用一对双绞线将各个接口的“A”、“B”端连接起来。这种处理办法在某些状况下也能够作业,但给体系埋下了危险,主要有以下两方面的问题:

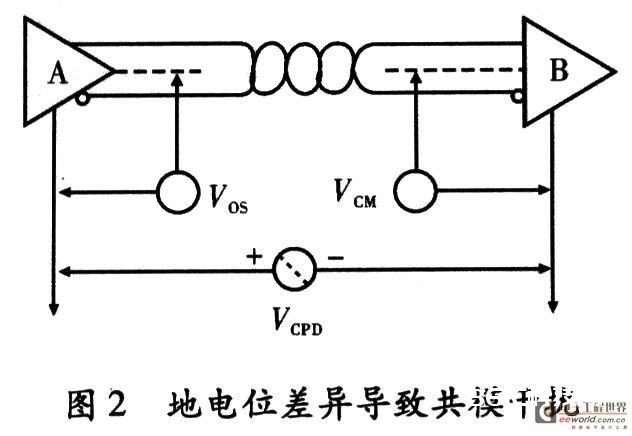

(1)共模搅扰问题。

RS一485接口选用差分方法传输信号,并不需求相关于某个参照点来检测信号,体系只需检测两线之间的电位差就能够了。但应该留意的是,收发器只要在共模电压不超出必定规模(一7~+12 V)的条件下才干正常作业。当共模电压超出此规模就会影响通讯的牢靠,直至损坏接口。如图2所示,当发送器A向接纳器B发送数据时,发送器A的输出共模电压为VOS,因为两个体系具有各自独立的接地体系,存在着地电位差VGPD。那么,接纳器输入端的共模电压就会到达VCM=VOS+VGPD。RS一485规范规则VOS≤3 V,但VGPD或许会有很大的起伏(十几伏乃至数十伏),并或许伴有强搅扰信号,致使接纳器共模输入VCM超出正常规模,并在信号线上发生搅扰电流,轻则影响正常通讯,重则损坏接口。