XFI(Ziffy音)和SFI是两个常见的10Gbps高速串行接口,都是衔接ASIC芯片和光模块的电气接口。在传统光通信,数据交换机和服务器等上都能够找到些接口。两者之间有什么类似的当地?差异在哪里?我规划的体系接口是否满意规范要求?本博客将逐个测验介绍。

XFI和SFI的来历

XFI来历于XFP光模块规范的一部分,指的是衔接ASIC芯片和XFP光模块的电气接口。XFP光模块规范界说于2002年左右,其内部的收和发方向都带有CDR电路。因而XFP模块尺度比较大,功耗也比较大,这个关于需求多端口高密度的体系,比方数通交换机会是一个问题。为了处理这两个问题,2006年左右,SFP+光模块规范出来了,其内部没有CDR电路,相关于XFP模块,SFP+模块尺度和功耗都变小了。对应SFP+的电气接口叫做SFI。

XFI接口先于SFI接口呈现。电气特性上,因为SFP+模块内部没有CDR,能够预见SFI的电气特性要求会比XFI来的更严厉一些,这个能够从接下来的介绍的眼图和颤动目标要求中能够清楚的看出来。

规范以及参考点

XFI接口的电气特性界说在INF-8077文档,SFI接口的电气特性界说在SFF8431文档。

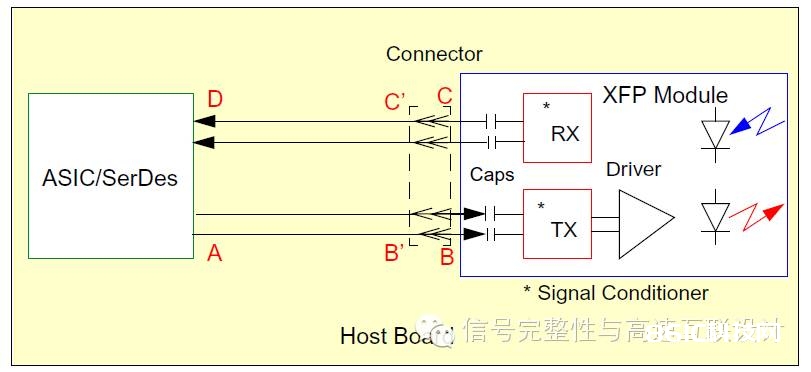

关于电气特性要求,这两个规范都界说了A,B,C和D四个参考点。

A代表体系板上ASIC芯片高速信号输出,封装管脚的方位

B代表体系板电信号输出的方位,即来自A点的信号经过PCB走线今后抵达光模块的电输入的方位

C代表体系板上接纳来自光模块的电信号,信号输入的方位

D代表体系板上ASIC芯片的高速信号输入,封装管脚的方位。即C点的信号经过PCB走线今后抵达ASIC的电输入方位

图1:参考点方位

以XFI的INF-8077i文档所界说为例,上图能够看到A、B、C和D参考点的方位。

眼图和颤动目标

在上述两个规范文件里,关于每个参考点的输入信号起伏,颤动,和回损等等都有悉数或许部分的界说。其间比较重要的目标是眼图模板和颤动要求,如下表格所示:

|

ASIC 发送端 |

光模块电接纳 |

||||

|

参考点 |

XFI(A) |

SFI(A) |

参考点 |

XFI(B) |

SFI(B) |

|

INF-8077i |

SFF8431 |

INF-8077i |

SFF8431 |

||

|

X1(UI) |

0.15 |

– |

X1 |

0.305UI |

0.12UI |

|

X2(UI) |

0.4 |

– |

X2 |

0.5UI |

0.33UI |

|

Y1(mV) |

180 |

– |

Y1 |

60mV |

95mV |

|

Y2(mV) |

385 |

– |

Y2 |

410mV |

350mV |

|

Jitter |

0.3UI |

– |

Jitter |

0.61UI |

0.28UI |

|

光模块电发送 |

ASIC 接纳端 |

||||

|

参考点 |

XFI(C) |

SFI(C) |

参考点 |

XFI(D) |

SFI(D) |

|

INF-8077 |

SFF8431 |

INF-8077 |

SFF8431 |

||

|

X1 |

0.17UI |

0.35UI |

X1 |

0.325UI |

– |

|

X2 |

0.42UI |

0.5UI |

X2 |

0.5UI |

– |

|

Y1 |

170mV |

150Mv |

Y1 |

55mV |

– |

|

Y2 |

425mV |

425mV |

Y2 |

525mV |

– |

|

Jitter |

0.34UI |

0.7UI |

Jitter |

0.65UI |

– |

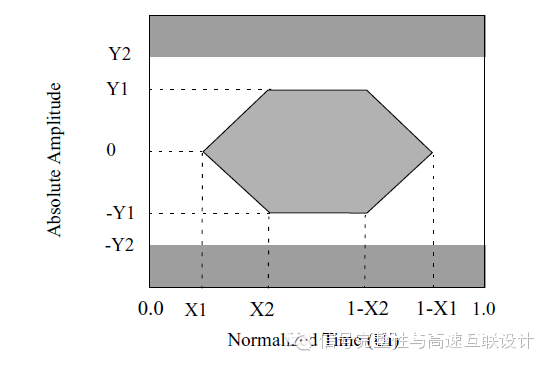

其间X1和X2,Y1和Y2是如下归一化眼图模板中,标示眼宽和样高的参数

图2:归一化眼图模板

A点和D点是体系板上的信号,这些是板内信号,做体系规划的时分,更需求关怀的是B点和C点的信号,因为这两个当地是跟外部接口的方位。

从上表能够看出,关于B点的要求,XFI的颤动要求是小于0.61UI,SFI要求小于0.28UI。XFI的电压要求大于120mV,SFI要求大于190mV。XFI比SFI的要求来的要宽松一些,这是因为XFP光模块内部集成了CDR。

关于C点的要求,XFI的颤动要求是小于0.34UI,SFI要求小于0.7UI。XFI的电压要求大于340mV,SFI要求大于300mV。这儿因为SFP+模块内部没有集成CDR,来自SFP+的电信号要比XFP模块来的差。

体系规划的问题和处理计划

经过以上的介绍,咱们知道体系规划时,需求重视B点和C点的信号。实践上这样带来了两个问题。第一个是,怎么确保我的体系B点是满意规范要求的。第二个是,怎么确保我的体系板上ASIC能够忍受来自C点最差的信号。这个就触及到到光模块和ASIC之间的链路了,咱们仍是先从规范开端。

XFI界说的最大链路衰减是9.6dB(见page19,INF-8077i, Revision 4.5)。SFI界说的引荐的最大链路衰减是9dB(见page66,SFF8431Revision 4.1),可是这项界说不是强制性的,也就是说ASIC供货商供给的产品功能有或许低于这个数值。

一般ASIC的供货商会供给规划主张,比方要求SFI链路长度小于5inches,或许供给通道的SDD21的模板。可是在咱们实践体系规划中,因为的运用不同,会碰到各种情况,比方:

1)面板要出的光模块端口许多,两头的光模块离ASIC间隔比较远。然后超越ASIC所界说的通道长度要求。

2)光模块放在一块子卡上,经过板间衔接器或许背板衔接器衔接别的一块板子,除了通道变长以外,衔接器的阻抗不接连都会带问题。

3)ASIC自身的发送端颤动输出功能不够好,或许接纳的颤动忍受功能不够好,导致AS%&&&&&%能够支撑的通道间隔很短。

怎么应对这个问题?

1)关于SFI接口,TI官网上有一个运用笔记本Selecting TI SigCon Devicesfor SFF-8431 SFP+

Applications,具体介绍了TI对SFP+接口的处理计划。关于光接口能够选用TI的Retimer芯片,如DS110DF111、DS100DF410等等。关于有源电缆运用,能够考虑运用Repeater如DS100BR111。

2)关于XFI接口,除了能够运用Retimer以外,因为XFP光模块内部集成了CDR,所以也能够考虑Repeater计划。

TI公司的产品DS110DF111、DS100DF410等芯片选用了体积小而且利于散热的QFN封装。您能够在www.ti.com/sigcon查询更多运用于Server、Storage以及Telecom等范畴的高速数据传输的Repeater和Retimer产品。