本文首要归纳一下,怎么针对Xilinx+ModelSim进行FPGA的仿真规划。

1. xHDL仿真器

常用的硬件描绘言语的仿真器有许多种,例如,VCS,Ncsim,Affirima,Verilog-XL,SpeedWave,Finisim和ModelSim。个人认为比较盛行的便是ModelSim和Ncsim,像opencores供给的源码大部分都含有Ncsim仿真支撑,或许ModelSim仿真支撑。

1.1 ModelSim简介

ModelSim仿真器在FPGA/CPLD规划中的运用得到了广泛的运用,这是因为Model Technology公司为各个FPGA/CPLD厂家都供给了OEM版别的ModelSim东西。ModelSim仿真原理是依据作业驱动的,它可支撑Verilog和VHDL言语的的独自仿真与混合仿真。

1.2 ModelSim版别

ModelSIm仿真东西有许多版别,首要便是他的版别号许多,这儿不多介绍,因为它无非便是软件功用,功用的晋级。这儿首要是要阐明ModelSim PE/LE/SE之间的差异:

为了满意不同用户的需求,ModelSim每个版别号都能够分为PE,LE和SE等类别。其间SE功用是比较完善的,可是它有一个特色便是,在进行仿真前,要首要编译相应的仿真库(通过设置,也能够一老永逸),后边会专门介绍。

在进行Xilinx FPGA产品开发时,咱们有时会遇到ModelSim XE版别,这是ModelSim的Xilinx OEM版别,里边集成了Xilinx的仿真库。相同道理也适用于Altera。

2. 仿真库的生成

结合自己的实践经历,本文以Verilog + ModelSim SE + Xilinx ISE为例来阐明仿真库的生成。

2.1 仿真库的命名

在ModelSim中编译器材的仿真库时,运用的仿真库的称号能够随意界说,只需满意操作系统的命明规矩就行。可是在实践操作中,则否则。

当咱们运用Xilinx ISE + ModelSim进行仿真时,Xilinx ISE会发生一些对ModelSim进行操控的文件,而在这些文件中,包括仿真库的映射机制,因而为了兼容性,这儿的仿真库的命名便是固定的了,而不是恣意界说。他们分别是Unisim_ver,Simprim_ver,Xilinxcorelib_ver。

2.2 仿真库文件的阐明

上面提到了ModelSim仿真所需求的3个根本的库,这儿首要介绍一下他们的效果。

Unisim_ver:假如要做归纳后的仿真,还要编译这个库。即UNISIM,Library of Unified Component simulation models,这个库用来做功用仿真。这个库包括了Xilinx的一切的规范元件,能够被绝大多数的归纳东西推论。UNISIM库被分为VHDL和Verilog两种。以Verilog为例:Verilog UNISIM库文件中每一个元件运用一个独立的文件。依据器材的不同,这个库分为两个目录,关于FPGA器材宗族,源文件方位在$Xilinx\Verilog\src\unisims目录下,关于CPLD宗族,源文件方位在$Xilinx\Verilog\src\uni9000目录下。

Simprim_ver:这个库用于布局布线后的仿真。关于Verilog来说,这个库坐落$Xilinx\Verilog\src\simprimes,关于VHDL来说,这个库坐落$Xilinx\VHDL\src\simprimes。

Xilinxcorelib_ver:这个库只是用来做功用仿真。但其和Unisim_ver不同,假如规划中调用了CoreGen发生的核,则需求编译这个库。Core Generator HDL Library models, 它包括了适用Core Generator发生的各种IP核的仿真模型。Xilinx的IP核都针对不同的器材结构作了很好的优化,可是关于运用者来说,大部分只能够做为黑合来处理。关于Verilog来说,其对应的源文件方位地点的方位是$Xilinx\Verilog\src\xilinxcorelib,对VHDL来说,其对应的源文件地点的方位是$Xilinx\VHDL\src\xilinxcorelib。

2.3 仿真库的树立

本节将以Verilog言语中时序仿真库simprimes为例来阐明,为ModelSim树立仿真库。

第一步:将ModelSim根目录下的装备文件Modelsim.ini特点由只读改为可读写。这样做的意图便是为了让软件能够记载仿真库树立的途径以及映射联系。今后每次发动Modelsim时,软件会依据ModelSim.ini中的装备寻觅仿真库,而且构成映射联系。

第二步:在这一步,有2种办法能够作。

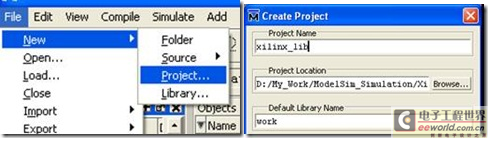

(1) 在modelsim环境下,新建工程,工程的途径与你想把库存储的途径共同。这儿Project Name: Xilinx_lib;

Project Location: D:/My_Work/ModelSim_Simulation/Xilinx—即仿真库保存的途径。如下图所示:

(2): 在主窗口中挑选[File] / [Change Directory]指令,将作业目录改到咱们想要保存仿真库的目录下,即D:/My_Work/ModelSim_Simulation/Xilinx。

以上两个办法均可,终究的成果都是相同的。

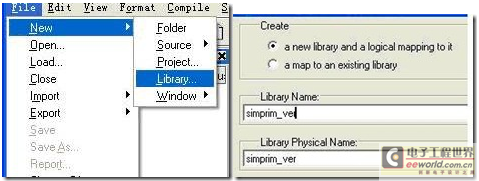

第三步:新建库,库名起作simprim_ver。咱们首要便是要建的便是这个库。

即在主窗口挑选[File] / [New] / [Library]指令,然后依据下图设置[Create]选项,[Library Name]选项,以及Libray Physical Name]选项(软件主动生成)。如下图所示:

这一操作实践上相当于在ModelSim主窗口的脚本区域输入指令

vlib simprimes_ver

vmap simprimes_ver simprimes_ver

第四步:这一步有两种办法完结,这两种方法是等效的

(1): 在modelsim的指令栏上,打下如下指令:

vlog -work simprim_ver $xilinx/verilog/src/simprims/*.v

其间的$xilinx是Xilinx ISE的装置途径,你把这个改成你的就行了。编译完之后,你会发现你的工程文件夹下呈现了一个simprim文件夹,里边又有许多个文件夹。这些便是咱们要的库了。

(2): 在主窗口挑选[Compile] / [Compile]指令,弹出[Compile Source Files]窗口,然后挑选$xilinx/verilog/src/simprims/目录下的一切*.v文件,点击Compile按钮履行编译。

第五步:依照第三步中的恣意一种方法编译其它两个库,对应的指令行是:

vlog -work unisim_ver $xilinx /verilog/src/unisims/*.v

vlog -work xilinxcorelib_ver $xilinx /verilog/src/XilinxCoreLib/*.v

第六步:库文件编译好了今后,为了便利今后运用,能够修正ModelSim.ini装备文件,翻开装备文件之后,可增加对Xilinx仿真库的映射。通过修正后,Xilinx ISE+ ModelSim进行各个阶段的仿真就不会呈现任何的错误了。PS:有的人反映,在仿真进程中,有时还需求指定库的途径,其原因便是ModelSim.ini文件没有装备正确。

假如还需求其它的仿真库支撑,例如abel_ver, cpld_ver,可依照上述的1~5步完结这些仿真库的增加。

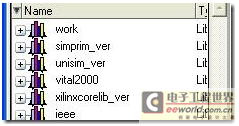

完结上面的进程后,假如从头翻开ModelSim,发现下面的库文件的话,就阐明,你的仿真环境树立好了,接下来就能够做你该做的作业了。

3. ModelSim常用指令

在作FPGA开发时,因为需求多次的修正源文件进行调试,因而,每次仿真都不可避免的要进行编译。这道程序比较费事,ModelSim供给了一个捷径,即咱们只需求编写一个*.do文件,然后再ModelSim指令行里键入do *.do就能够代替这一费事进程。

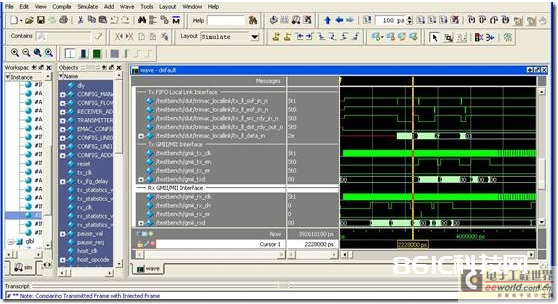

下面以Giga Eth MAC开发仿真为例,阐明一下*.do的语法结构,如下图所示:

(1) vlib work >> 因为vlib<库名>,表明创立一个库,因而vlib work表明创立一个work库,这儿的work是库的称号。

(2) vmap work work >>vmap表明映射库,前一个work表明以创立的库的称号,后一个work表明当时ModelSim作业目录下的文件夹,行将一个名为work的库映射到当时目下的work文件夹。

(3) vlog -work work C:/Xilinx91i/verilog/src/glbl.v >> vlog表明编译源代码,”-work”表明其后边跟着的参数表明编译完的源文件要寄存的方位,终究的参数表明源文件的方位,即该语法表明,将文件C:/Xilinx91i/verilog/src/glbl.v编译,得到的编译后的文件,寄存在当时作业目录下的work目录下。

终究的仿真成果如下图所示: